引言

在同步電路設(shè)計(jì)中,時(shí)序是一個(gè)非常重要的因素,它決定了電路能否以預(yù)期的時(shí)鐘速率運(yùn)行。為了驗(yàn)證電路的時(shí)序性能,我們需要進(jìn)行靜態(tài)時(shí)序分析,即在最壞情況下檢查所有可能的時(shí)序違規(guī)路徑,而不需要測(cè)試向量和動(dòng)態(tài)仿真。本文將介紹靜態(tài)時(shí)序分析的基本概念和方法,包括時(shí)序約束,時(shí)序路徑,時(shí)序裕量,setup檢查和hold檢查等。

時(shí)序路徑

同步電路設(shè)計(jì)中,時(shí)序是一個(gè)主要的考慮因素,它影響了電路的性能和功能。為了驗(yàn)證電路是否能在最壞情況下滿足時(shí)序要求,我們需要進(jìn)行靜態(tài)時(shí)序分析,即不依賴于測(cè)試向量和動(dòng)態(tài)仿真,而只根據(jù)每個(gè)邏輯門的最大延遲來(lái)檢查所有可能的時(shí)序違規(guī)路徑。

時(shí)序,面積和功耗是綜合和物理實(shí)現(xiàn)的主要驅(qū)動(dòng)因素。芯片EDA工具的目標(biāo)是在最短的運(yùn)行時(shí)間內(nèi),用最小的面積和功耗,生成滿足時(shí)序網(wǎng)表,并進(jìn)行布局和布線。EDA工具會(huì)根據(jù)設(shè)計(jì)者給定的約束條件,在時(shí)序,面積,功耗和EDA工具運(yùn)行時(shí)間之間做出權(quán)衡。

芯片要想以期望的時(shí)鐘頻率運(yùn)行,就必須遵守時(shí)序約束,因此時(shí)序是最重要的設(shè)計(jì)約束。靜態(tài)時(shí)序分析的核心問(wèn)題是:

“在所有情況下(multi-mode multi-corner),每個(gè)同步設(shè)備(synchronous device,例如觸發(fā)器)的數(shù)據(jù)輸入端,在時(shí)鐘邊沿到達(dá)時(shí),是否已經(jīng)有正確的數(shù)據(jù)?”

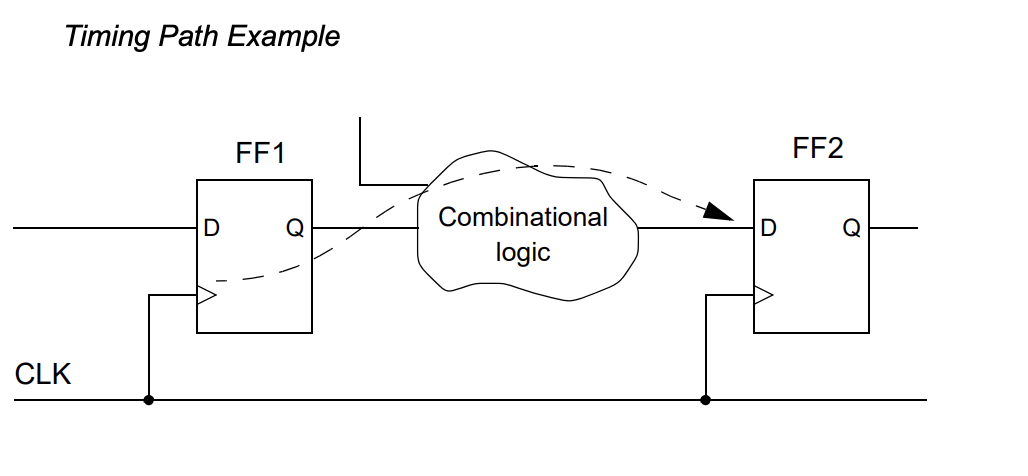

上圖中的虛線箭頭代表了時(shí)序路徑。為了保證數(shù)據(jù)能被準(zhǔn)確地鎖存,數(shù)據(jù)信號(hào)必須在時(shí)鐘邊沿到達(dá)觸發(fā)器FF2的時(shí)鐘端之前,傳遞到觸發(fā)器FF2的數(shù)據(jù)端。

setup檢查

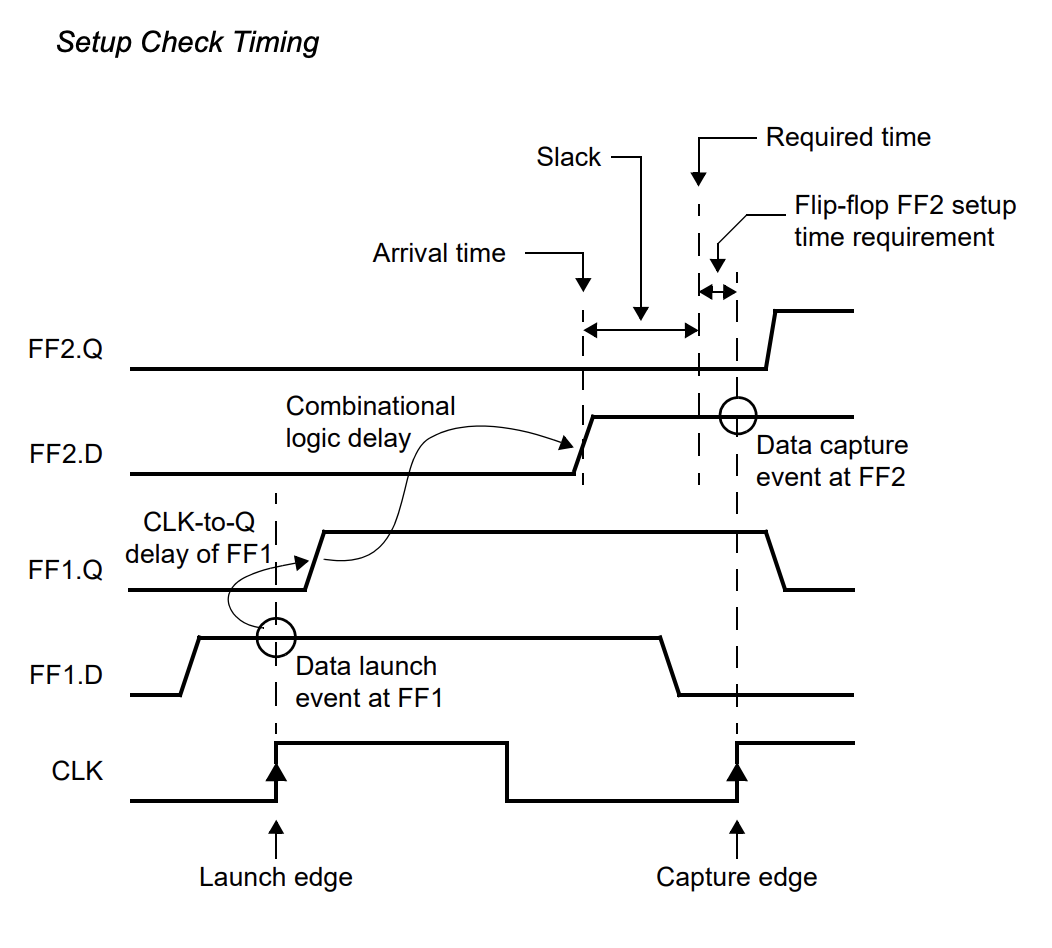

上圖展示了這條時(shí)序路徑的時(shí)序情況。當(dāng)時(shí)鐘邊沿到達(dá)FF1時(shí),F(xiàn)F1會(huì)鎖存FF1.D的數(shù)據(jù)。經(jīng)過(guò)觸發(fā)器的CLK-to-Q延遲后,數(shù)據(jù)會(huì)出現(xiàn)在觸發(fā)器的輸出端FF1.Q。這個(gè)過(guò)程叫做時(shí)序路徑的launch event。

然后,數(shù)據(jù)信號(hào)經(jīng)過(guò)一定的延遲,通過(guò)組合邏輯,到達(dá)觸發(fā)器FF2的輸入端FF2.D。數(shù)據(jù)信號(hào)到達(dá)這里的時(shí)間叫做路徑的arrival time。

為了讓FF2能正確地鎖存數(shù)據(jù),F(xiàn)F2.D的值必須在時(shí)鐘邊沿到達(dá)FF2的時(shí)鐘端之前穩(wěn)定下來(lái),并且提前一定的時(shí)間,即觸發(fā)器的建立時(shí)間。這個(gè)最小的允許時(shí)間叫做路徑的required time。FF2鎖存數(shù)據(jù)的過(guò)程叫做時(shí)序路徑的capture event。

時(shí)序裕量

時(shí)序路徑是否滿足時(shí)序約束,取決于它的時(shí)間裕量,即slack。

如果數(shù)據(jù)信號(hào)比必要的時(shí)間早到達(dá),那么slack就是正值。

如果數(shù)據(jù)信號(hào)剛好在required time到達(dá),那么slack就是零。

如果數(shù)據(jù)信號(hào)比required time晚到達(dá),那么slack就是負(fù)值。

在任何情況下,slack都等于required time減去arrival time。

上面描述的時(shí)序檢查叫做setup檢查,它用來(lái)驗(yàn)證數(shù)據(jù)是否能在每個(gè)時(shí)鐘邊沿之前及時(shí)到達(dá)時(shí)序電路。這是綜合和時(shí)序優(yōu)化中最常見的一種時(shí)序檢查類型。

hold檢查

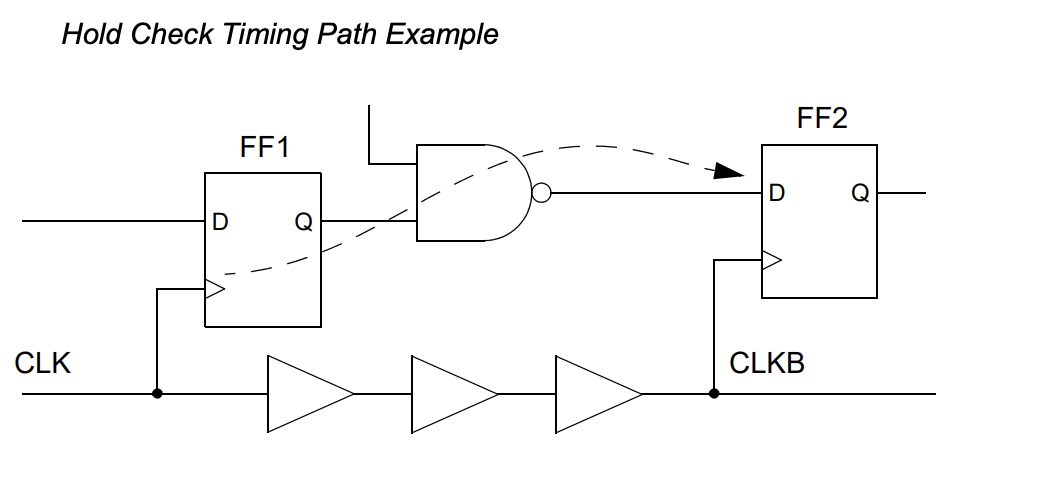

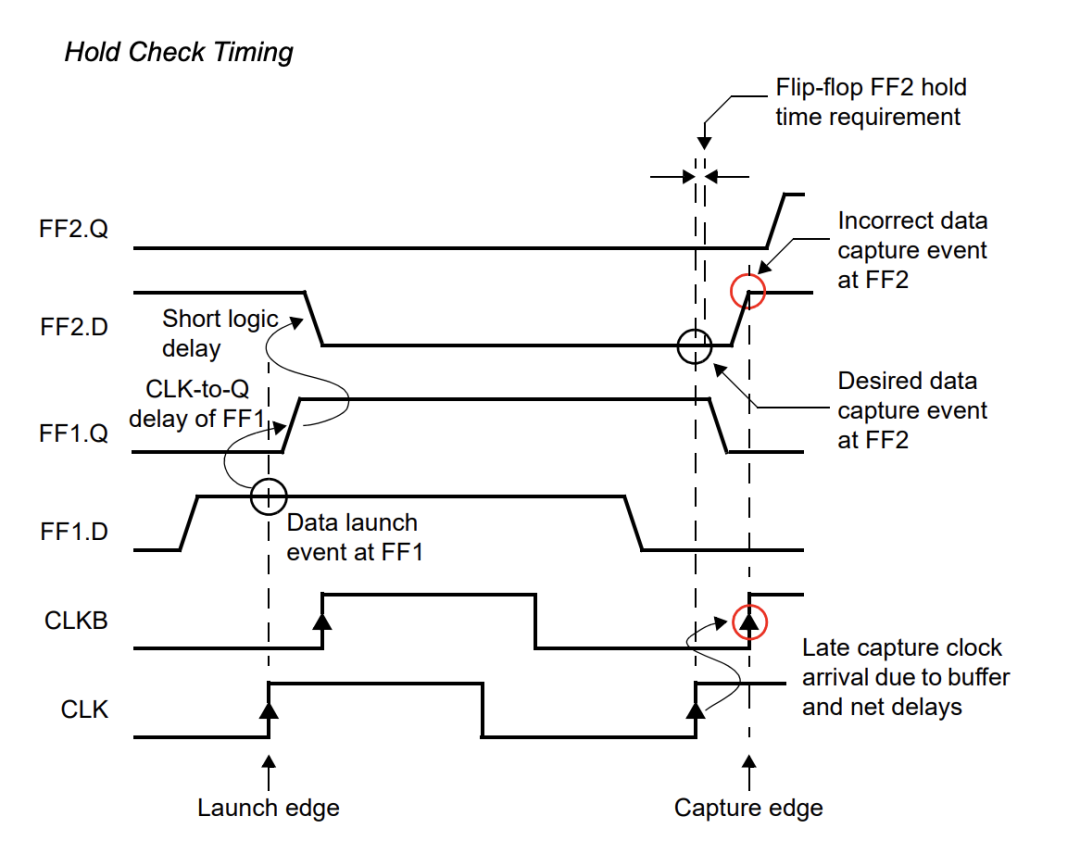

hold檢查用來(lái)驗(yàn)證數(shù)據(jù)在時(shí)鐘邊沿到達(dá)后,還能保持多久的有效性。如果從launch到capture的數(shù)據(jù)路徑上的組合延遲太短,而從launch到capture的時(shí)鐘路徑上的延遲太長(zhǎng),就有可能出現(xiàn)hold違規(guī)。下圖給出了這種情況的例子。

上圖中,數(shù)據(jù)從FF1到FF2的時(shí)序路徑只經(jīng)過(guò)了一個(gè)NAND門,組合延遲非常短。而時(shí)鐘信號(hào)從時(shí)鐘源到FF2的路徑上有三個(gè)緩沖器,延遲非常長(zhǎng)。

上圖顯示了這種情況下的可能時(shí)序。由于數(shù)據(jù)在setup time之前到達(dá),所以很容易滿足setup約束。然而,問(wèn)題在于FF2的D輸入端的數(shù)據(jù)不能保持足夠長(zhǎng)的時(shí)間,導(dǎo)致hold約束不能滿足。也就是說(shuō),數(shù)據(jù)在時(shí)鐘CLKB鎖存之前發(fā)生變化。

為了修復(fù)這種類型的違規(guī),我們可以通過(guò)縮短時(shí)鐘線的延遲或增加數(shù)據(jù)路徑的延遲來(lái)調(diào)整時(shí)序。

最壞情況(worst-case conditions)

每種類型的時(shí)序檢查都考慮了不同的最壞情況(worst-case conditions)。例如,一個(gè)setup檢查(驗(yàn)證數(shù)據(jù)是否在時(shí)鐘邊沿之前到達(dá))考慮最長(zhǎng)的組合邏輯/最慢的數(shù)據(jù)路徑,以及最早的時(shí)鐘路徑。相反,hold檢查(驗(yàn)證數(shù)據(jù)是否在時(shí)鐘邊沿之后保持有效的時(shí)間)考慮最短/最快的數(shù)據(jù)路徑,以及最晚的時(shí)鐘路徑。

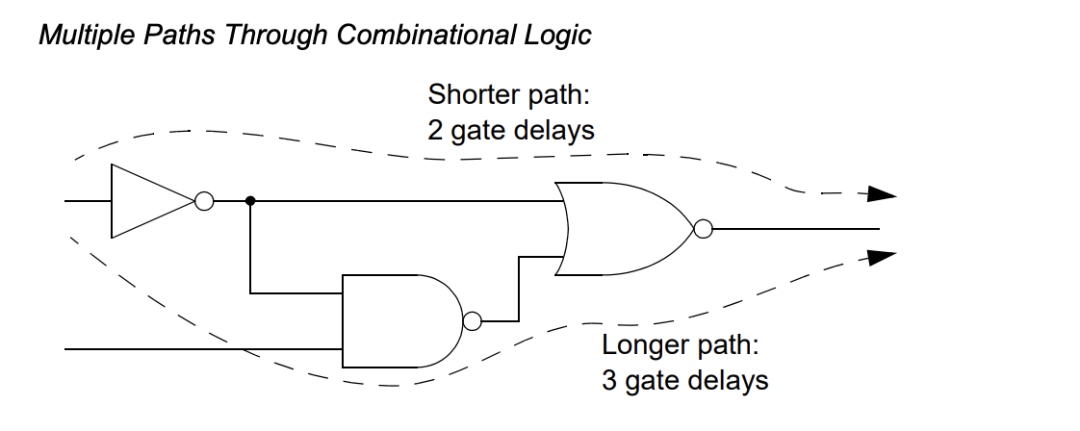

上圖顯示了通過(guò)同一個(gè)模塊不同組合邏輯路徑的示例。在數(shù)據(jù)路徑中,setup檢查會(huì)考慮較長(zhǎng)的延遲(通過(guò)三個(gè)門),而hold檢查將考慮較短的路徑(通過(guò)兩個(gè)門)。

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7241瀏覽量

91007 -

eda

+關(guān)注

關(guān)注

71文章

2888瀏覽量

176463 -

靜態(tài)時(shí)序分析

+關(guān)注

關(guān)注

0文章

29瀏覽量

9665

發(fā)布評(píng)論請(qǐng)先 登錄

時(shí)序分析中的一些基本概念

靜態(tài)時(shí)序分析與邏輯(華為內(nèi)部培訓(xùn)資料)

時(shí)序分析中的一些基本概念

時(shí)序分析基本概念——STA概述簡(jiǎn)析

時(shí)序分析基本概念介紹——時(shí)序庫(kù)Lib,除了這些你還想知道什么?

正點(diǎn)原子FPGA靜態(tài)時(shí)序分析與時(shí)序約束教程

時(shí)序分析和時(shí)序約束的基本概念詳細(xì)說(shuō)明

FPGA設(shè)計(jì)中時(shí)序分析的基本概念

時(shí)序分析Slew/Transition基本概念介紹

時(shí)序分析基本概念介紹—Timing Arc

靜態(tài)時(shí)序分析的基本概念和方法

靜態(tài)時(shí)序分析的基本概念和方法

評(píng)論