今天我們要介紹的時(shí)序分析概念是generate clock。中文名為生成時(shí)鐘。generate clock定義在sdc中,是一個(gè)重要的時(shí)鐘概念。

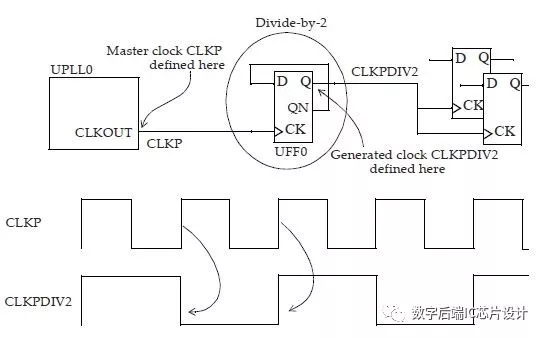

它從master clock中取得的時(shí)鐘定義。master clock就是指create_clock命令指定的時(shí)鐘產(chǎn)生點(diǎn),如圖所示:

我們可以用如下命令來(lái)描述generated clocks:

#定義master clock

create_clock -name CLKP -period 10 \

-waveform {0 5} [get_pins UPLL0/CLKOUT]

#在Q點(diǎn)定義generated clock

create_generated_clock -name CLKPDIV2 \

-source UPLL0/CLKOUT -add \

-master_clockCLKP -divide_by 2 [get_pins UFF0/Q]

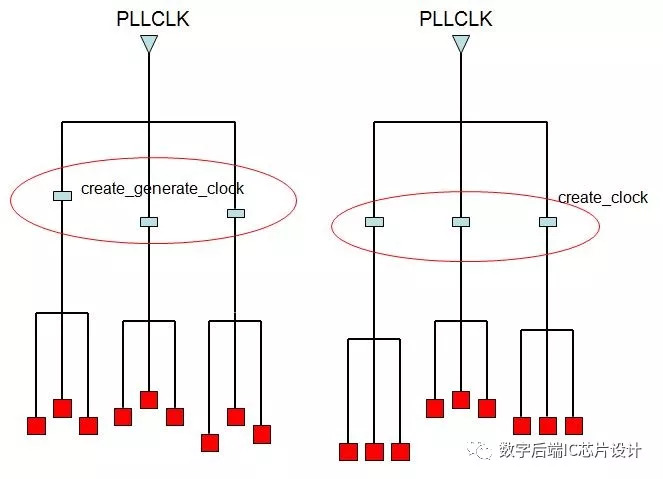

一般我們把時(shí)鐘的源頭會(huì)定義成create_clock,而分頻時(shí)鐘則會(huì)定義為create_generated_clock. 兩者的主要區(qū)別在于CTS步驟,generated clock并不會(huì)產(chǎn)生新的clock domain, 而且定義generated clock后,clock path的起點(diǎn)始終位于master clock, 這樣source latency并不會(huì)重新的計(jì)算。

上圖中描述,如果我們給PLLCLK出來(lái)的三個(gè)分頻點(diǎn)定義為generate clock,則在trace clock tree時(shí),工具會(huì)穿過這三個(gè)點(diǎn),并不會(huì)產(chǎn)生新的clock,對(duì)工具來(lái)說(shuō),它會(huì)balance所有clock sink。這種情況下,clock tree通常會(huì)做得比較長(zhǎng)一些。

相反,如果我們給這三個(gè)分頻點(diǎn)定義為create_clock,則在trace clock tree時(shí),這三個(gè)點(diǎn)會(huì)生成各自新的clock tree,屬于他們自己的sink會(huì)分別做balance,但是相互之間會(huì)不做balance。而且它本身的input clock pin也會(huì)被當(dāng)成PLLCLK的sink進(jìn)行balance。

-

時(shí)序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22824 -

CTS

+關(guān)注

關(guān)注

0文章

35瀏覽量

14383

原文標(biāo)題:時(shí)序分析基本概念介紹

文章出處:【微信號(hào):IC_Physical_Design,微信公眾號(hào):數(shù)字后端IC芯片設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

時(shí)序分析的基本概念ETM的詳細(xì)介紹及如何應(yīng)用的資料概述

時(shí)序分析和時(shí)序約束的基本概念詳細(xì)說(shuō)明

FPGA設(shè)計(jì)中時(shí)序分析的基本概念

時(shí)序分析Slew/Transition基本概念介紹

時(shí)序分析基本概念介紹—Timing Arc

時(shí)序分析基本概念之生成時(shí)鐘詳細(xì)資料介紹描述

時(shí)序分析基本概念之生成時(shí)鐘詳細(xì)資料介紹描述

評(píng)論