今天要介紹的時(shí)序分析基本概念是 Latency , 時(shí)鐘傳播延遲。主要指從Clock源到時(shí)序組件Clock輸入端的延遲時(shí)間。它可以分為兩個(gè)部分: 時(shí)鐘源插入延遲 (source latency)和 時(shí)鐘網(wǎng)絡(luò)延遲 (network latency)

source latency :也被稱為insertion delay。主要指從clock source端到clock定義端的延遲,即是時(shí)鐘源(例如PLL)到當(dāng)前芯片時(shí)鐘根節(jié)點(diǎn)(clock root pin)之間的延遲。

network latency :主要指從clock定義端到時(shí)序器件的clock pin端的延遲。

以下兩張圖分別定義了片上(on chip)和片外(off chip)中clock latency的描述。

我們可以用如下命令來定義描述clock latency:

#specify source latency

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

#specify network latency

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

那latency值有什么用呢?其實(shí)這相當(dāng)于一個(gè)target值,CTS的engine會(huì)根據(jù)你設(shè)置的latency值來插入buffer(當(dāng)然只是對network latency操作),做出一個(gè)接近于你設(shè)定的值,可能多一點(diǎn),也可能少一點(diǎn)。

latency值的大小直接影響著clock skew的計(jì)算和固定。因?yàn)槲覀兊臅r(shí)鐘樹是以平衡為目的,假設(shè)你對一個(gè)root和sink設(shè)置了1ns的latency值,那么對另外的幾個(gè)sink來說,就算你沒有給定latency值,CTS為了得到較小的skew,也會(huì)將另外的幾個(gè)sink做成1ns的latency。過大的latency值會(huì)受到OCV和PVT等因素的影響較大。而當(dāng)我們生長好了clock tree以后,latency的設(shè)定也就不起作用了。

-

時(shí)序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22822 -

OCV

+關(guān)注

關(guān)注

0文章

25瀏覽量

12689 -

時(shí)鐘源

+關(guān)注

關(guān)注

0文章

97瀏覽量

16234 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6713 -

時(shí)序分析器

+關(guān)注

關(guān)注

0文章

24瀏覽量

5340

發(fā)布評論請先 登錄

時(shí)序分析基本概念介紹<Operating Condition>

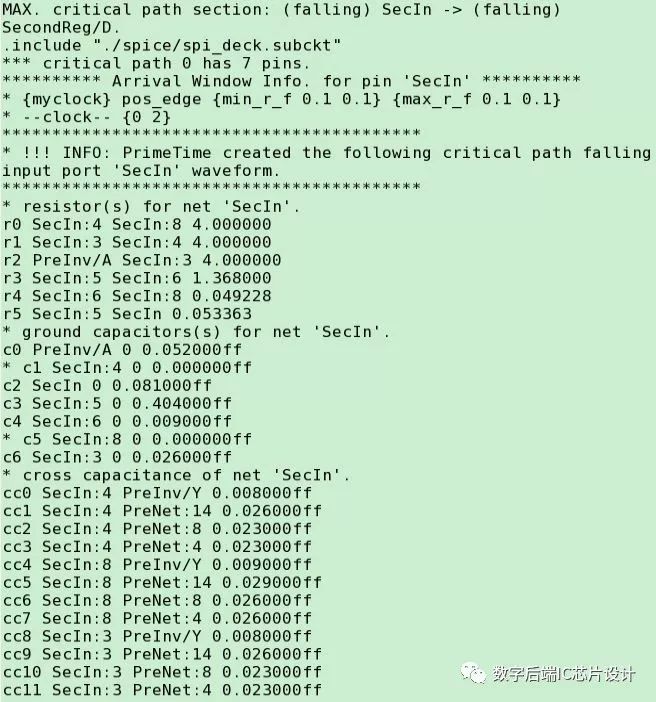

時(shí)序分析基本概念介紹&lt;spice deck&gt;

時(shí)序分析基本概念介紹&lt;generate clock&gt;

時(shí)序分析基本概念介紹—Timing Arc

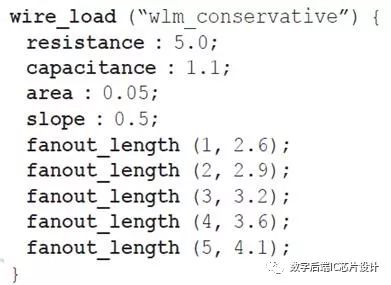

時(shí)序分析基本概念介紹&lt;wire load model&gt;

時(shí)序分析基本概念介紹&lt;ILM&gt;

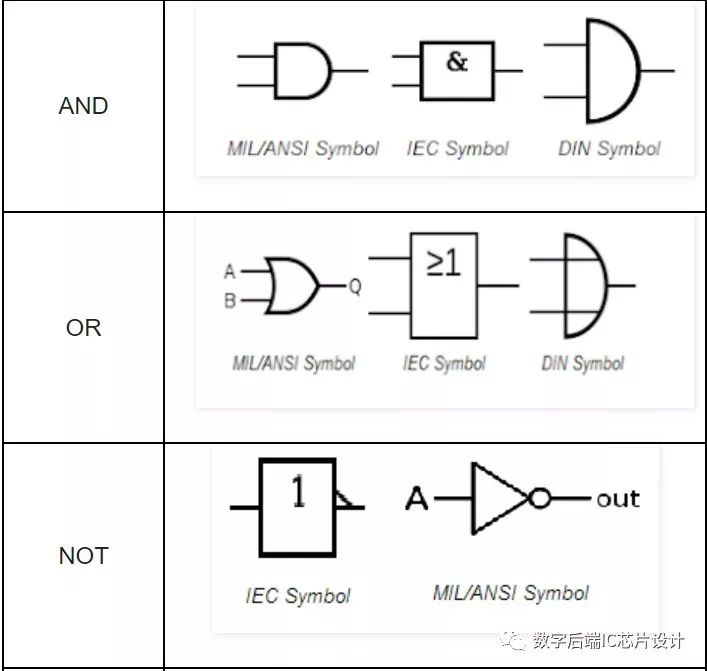

時(shí)序分析基本概念介紹&lt;Combinational logic&gt;

時(shí)序分析基本概念介紹<Latency>

時(shí)序分析基本概念介紹<Latency>

評論