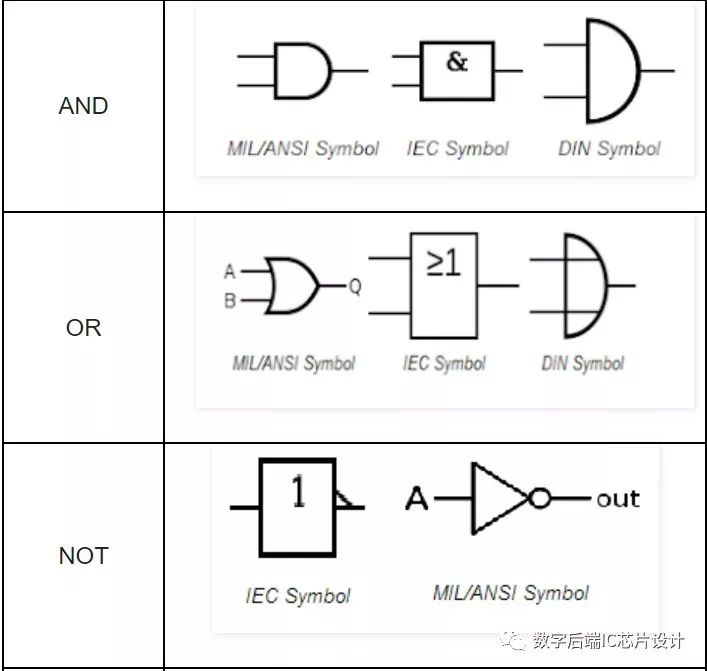

今天我們要介紹的時(shí)序分析概念是 Combinational logic . 中文名組合邏輯單元。這是邏輯單元的基本組成器件。比如我們常見(jiàn)的and, or, not, nand,nor等門電路。

對(duì)于組合邏輯來(lái)說(shuō),輸出只是當(dāng)前輸入邏輯電平的函數(shù)(有延時(shí)),與電路的原始狀態(tài)無(wú)關(guān)。當(dāng)前電路輸入信號(hào)任何一個(gè)發(fā)生改變,輸出都將發(fā)生改變。

AND, OR, NOT是最基本的門電路,NAND與NOR是通用門電路,可以實(shí)現(xiàn)任何其他組合邏輯電路。還有一些常見(jiàn)的復(fù)雜組合邏輯電路,比如全加器,數(shù)據(jù)選擇器,譯碼器等等。

下表是常見(jiàn)的邏輯門電路示意圖:

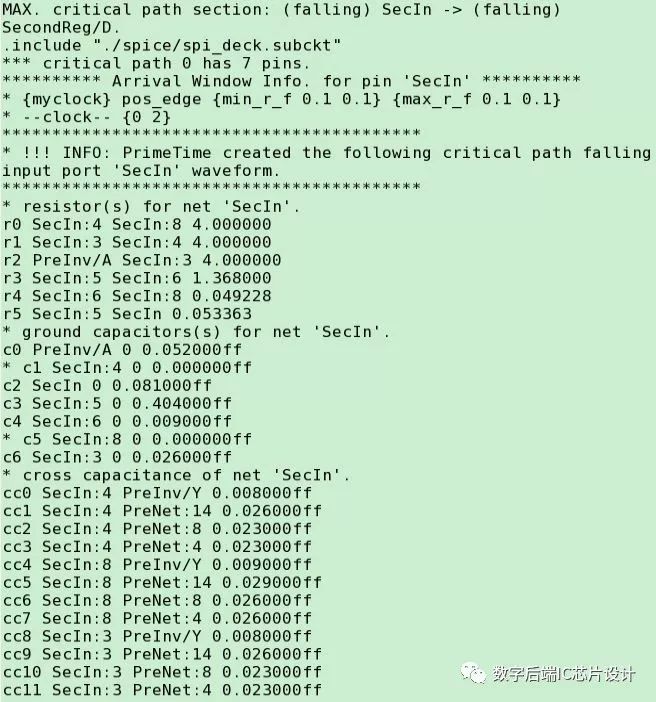

對(duì)于組合邏輯單元,每個(gè)輸入pin和輸出pin都會(huì)存在一個(gè)timing arc關(guān)系,這也是我們平時(shí)說(shuō)的cell的delay.

如下圖所示:

-

門電路

+關(guān)注

關(guān)注

7文章

201瀏覽量

40739 -

全加器

+關(guān)注

關(guān)注

10文章

62瀏覽量

28835 -

時(shí)序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

23790 -

時(shí)序分析器

+關(guān)注

關(guān)注

0文章

24瀏覽量

5369 -

邏輯電平設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

2瀏覽量

1184

發(fā)布評(píng)論請(qǐng)先 登錄

時(shí)序分析基本概念介紹<Operating Condition>

時(shí)序分析基本概念介紹&lt;Latency&gt;

時(shí)序分析Slew/Transition基本概念介紹

時(shí)序分析基本概念介紹&lt;spice deck&gt;

時(shí)序分析基本概念介紹&lt;generate clock&gt;

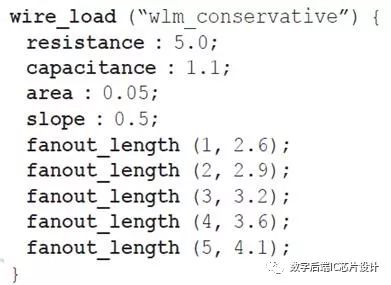

時(shí)序分析基本概念介紹&lt;wire load model&gt;

時(shí)序分析基本概念介紹&lt;ILM&gt;

時(shí)序分析基本概念介紹<Combinational logic>

時(shí)序分析基本概念介紹<Combinational logic>

評(píng)論