今天我們要介紹的時序分析概念是Combinational logic. 中文名組合邏輯單元。這是邏輯單元的基本組成器件。比如我們常見的and, or, not, nand,nor等門電路。對于組合邏輯來說,輸出只是當前輸入邏輯電平的函數(有延時),與電路的原始狀態無關。當前電路輸入信號任何一個發生改變,輸出都將發生改變。

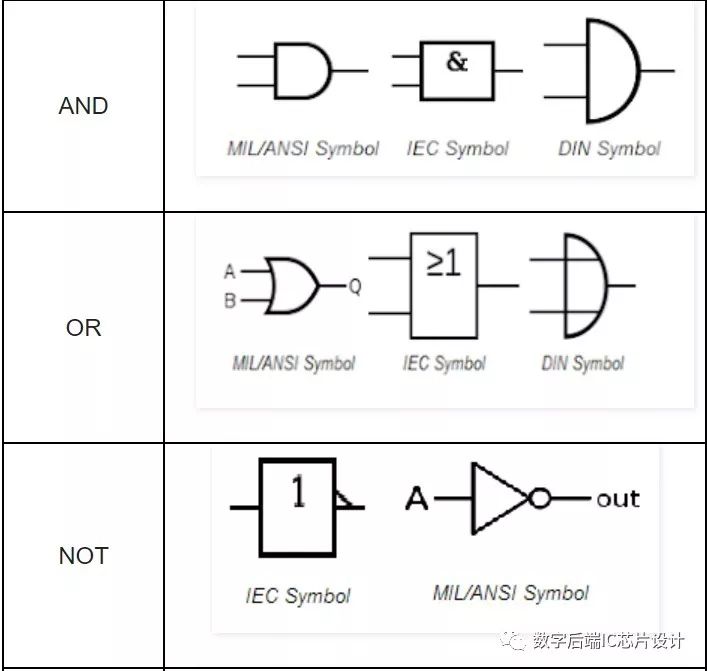

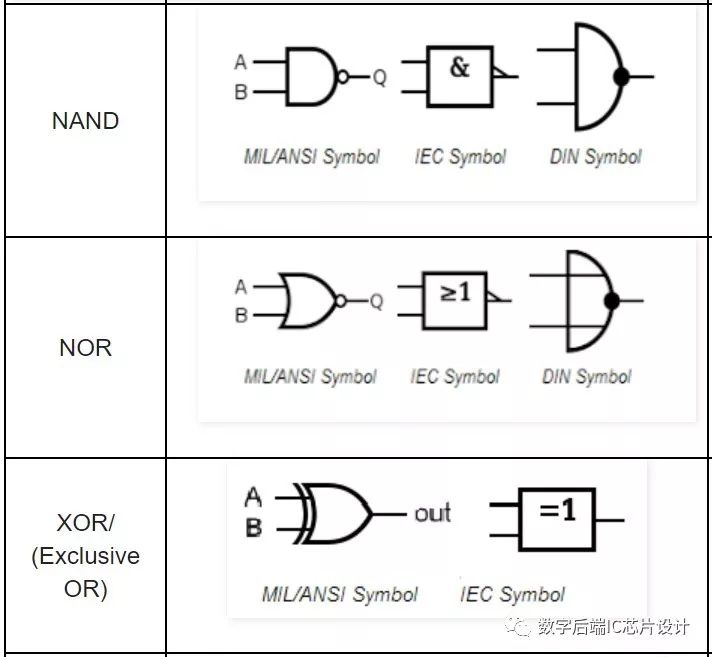

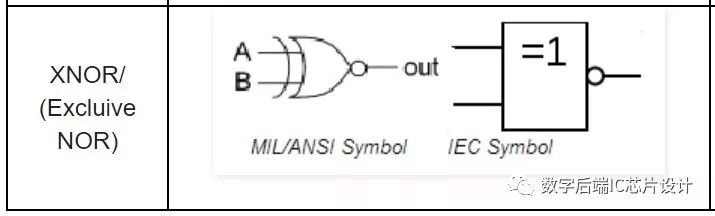

AND, OR, NOT是最基本的門電路,NAND與NOR是通用門電路,可以實現任何其他組合邏輯電路。還有一些常見的復雜組合邏輯電路,比如全加器,數據選擇器,譯碼器等等。

下表是常見的邏輯門電路示意圖:

對于組合邏輯單元,每個輸入pin和輸出pin都會存在一個timing arc關系,這也是我們平時說的cell的delay.

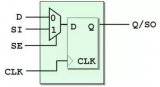

如下圖所示:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

邏輯電路

+關注

關注

13文章

502瀏覽量

43167

發布評論請先 登錄

相關推薦

熱點推薦

時序分析基本概念介紹——花一樣的“模式”

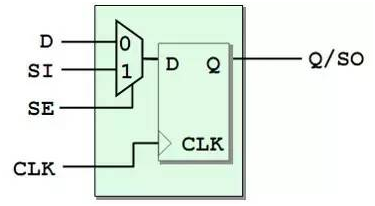

SE是scan enable信號,它控制著scan cell的工作模式。從圖中可以看出,SE,SI,D端通過一個Mux實現工作模式的切換。當SE輸入為0時,scan cell工作在普通模式下,相當于是普通的flop;當SE輸入為1時,scan cell就進入scan模式,相當于一個移位寄存器。

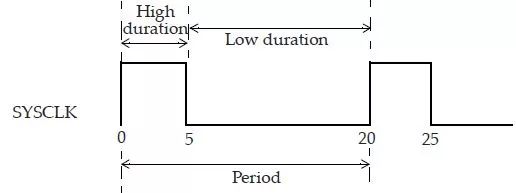

時序分析基本概念介紹<generate clock>

今天我們要介紹的時序分析概念是generate clock。中文名為生成時鐘。generate clock定義在sdc中,是一個重要的時鐘概念

時序分析基本概念介紹—花一樣的“模式”

今天要介紹的時序基本概念是Mode(模式). 這是Multiple Scenario環境下Sign off的一個重要概念。芯片的設計模式包括最基本的功能function模式,以及各種各

時序分析基本概念介紹

時序分析基本概念介紹

評論