電信行業(yè)要求具有很高的服務可用性-正如你一拿起電話就希望聽到撥號音一樣。隨著寬帶服務提供商爭相進入音頻和視頻領域(伴隨所謂的"三重播放"的展開),用戶期望他們可以在這些領域實現(xiàn)同樣的高可用性。

高可用性只能通過為構成系統(tǒng)的硬件提供冗余性來實現(xiàn)。然而,為了有效管理這種冗余,系統(tǒng)必須能夠監(jiān)控自己的運行狀態(tài),如果發(fā)生故障,系統(tǒng)必須在用戶覺察到任何故障停機之前切換到備用硬件。對物理環(huán)境的密切監(jiān)控,讓運營商可以在發(fā)生任何部件故障時采取積極行動。這涉及到監(jiān)控機架內部的物理環(huán)境,利用各種傳感器來記錄相關變量,比如溫度、電源電壓、濕度和冷卻性能等。

FPGA是高可用性基礎設施中的重要構建模塊。因此,應該密切監(jiān)控系統(tǒng)內FPGA的片上環(huán)境及其周圍環(huán)境。Xilinx Virtex-5系統(tǒng).可以更加輕松地監(jiān)控FPGA及其外部環(huán)境。

Virtex-5系統(tǒng).

Virtex-5系統(tǒng).能夠讓用戶輕松獲得FPGA片上(晶片)溫度和電源條件方面的信息。它還可以通過外部模擬輸入通道獲取外部傳感器信息(最多可以監(jiān)控17個外部傳感器)。獲取上述信息需要很少的設計努力,甚至不需要,具體取決于所需的功能。常見的功能,比如報警、自動通道定序器和數(shù)據(jù)平均,都可以從系統(tǒng).模塊中得到,這樣設計人員就能夠輕而易舉地開發(fā)出一個解決方案。

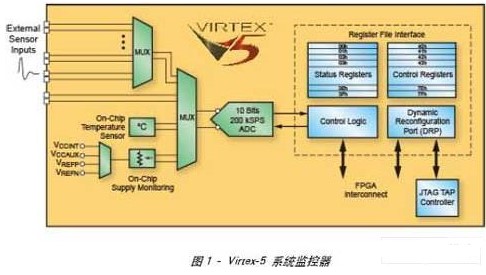

圖1給出了Virtex-5系統(tǒng).的結構圖。該.的核心是一個10位(每秒200,000個采樣)模數(shù)轉換器(ADC)。ADC的模擬輸入范圍是0~1V。在10比特的分辨率下,該ADC能夠處理的輸入電壓精度大約為1mV。

如圖1所示,片上傳感器和外部模擬輸入通道都通過模擬多路復用器與ADC輸入端相連。因此,從不同傳感器獲得的電壓必須由ADC轉化成數(shù)字量。測量結果被寫入狀態(tài)寄存器,并能夠利用FPGA架構或者通過FPGA和PCB的JTAG基礎設施從外部輕松讀取上述狀態(tài)寄存器中的數(shù)據(jù)。利用同樣的接口也可以對.的控制寄存器進行讀寫操作。控制寄存器對系統(tǒng).的操作(例如,針對測試、編程報警極限和傳感器平均的要求選擇合適的傳感器通道)進行配置。加電后不久系統(tǒng).就完全進入工作狀態(tài),而且在不配置FPGA的條件下就能夠進行正確的操作。默認情況下,加電后只會監(jiān)控片上傳感器;但也可以啟用外部模擬輸入。配置前只能通過JTAG測試訪問端口(TAP)獲取測量信息。

1. 用戶報警

系統(tǒng).的實用內置特性之一是,它能為片上傳感器生成報警信號。設計師能夠設定上述報警信號的閾值。系統(tǒng).可以自主監(jiān)控這些傳感器,并且只有在檢測到報警狀態(tài)時才會對系統(tǒng)發(fā)出報警。

系統(tǒng).還含有一個工廠設置的報警狀態(tài),被稱為過熱報警(OT)。一旦啟用該功能,如果檢測到晶片溫度高于125℃,系統(tǒng).就會請求關閉整個芯片。當晶片冷卻到設定的溫度水平時,才給晶片加電。在芯片掉電期間,系統(tǒng).會繼續(xù)操作片上傳感器,并且對其進行監(jiān)控。

默認情況下不會啟用OT功能,如果需要,必須明確啟用此功能方可生效。

2. 對“檢驗器”進行檢驗

為了讓Virtex-5系統(tǒng).提供精確而又可靠的環(huán)境信息,需要對測量數(shù)據(jù)和系統(tǒng).操作進行可靠性檢查。系統(tǒng).擁有大量有助于保證操作可靠性的功能。ADC的內置自動校準功能和傳感器可以糾正模擬測量系統(tǒng)中由工作環(huán)境造成的任何漂移。自檢功能還能讓系統(tǒng)主機對系統(tǒng).的運行狀態(tài)進行監(jiān)控。

利用系統(tǒng).JTAG訪問功能

Virtex-5系統(tǒng).還具備一個新功能,即通過JTAG TAP訪問模塊的所有功能。通過實現(xiàn)模擬測試和訪問模擬信息,您能夠利用系統(tǒng)中現(xiàn)有的JTAG獲得更大的價值和效率。在配置FPGA(該FPGA作為實際生產(chǎn)中PCB測試方案的一部分)之前或正常操作的過程中,可以訪問這些功能,從而簡化了調試。

為了簡化PCB的電源電壓和電流之類的片外測量,您可以在配置FPGA之前使用特殊的JTAG命令來為外部模擬輸入創(chuàng)造條件。即使配置完FPGA,系統(tǒng).也不需要在設計中進行明確例示,因此可以通過JTAG TAP訪問那些用于實現(xiàn)調試功能的特性,即使是在設計后期。為了確保系統(tǒng).的可用性,唯一的要求在于,必須提供正確的PCB支持。這涉及與系統(tǒng).用戶指南中描述的外部2.5V參考IC進行連接的問題。

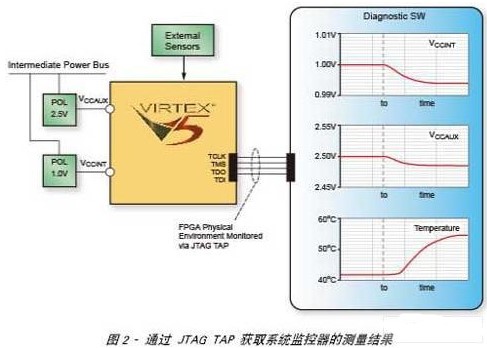

圖2顯示了一個典型診斷應用,在正常操作時對FPGA的物理運行環(huán)境進行監(jiān)控。在圖2的例子中,系統(tǒng).用于觀察大電流需求期間(從t0時刻開始)功率分配系統(tǒng)(PDS)中的電壓(IR)降。在上述高活動期間,我們還監(jiān)控了FPGA的溫度。能夠在開發(fā)階段迅速確定電源或PCB設計的潛在問題。JTAG訪問功能還提供了一個簡便的方法,能夠確認特定設計是否配有適當?shù)睦鋮s系統(tǒng)。ChipScope Pro分析器可以輕松訪問系統(tǒng).;而且,這種訪問功能還能夠輕松地集成到其它JTAG測試和編程環(huán)境中。

系統(tǒng)集成

除了能夠利用JTAG TAP輕松訪問系統(tǒng).之外,還可以通過FPGA架構訪問系統(tǒng).的控制和狀態(tài)寄存器。利用FPGA架構可以在任何時刻對這些寄存器進行配置和讀取。允許通過JTAG TAP控制器和架構接口對系統(tǒng).的寄存器進行雙重訪問,并提供了相應的仲裁方案來管理可能出現(xiàn)的爭用現(xiàn)象。

在設計中例示系統(tǒng).,并在FPGA配置過程中對其初始化時,還能夠定義這些寄存器的內容。因此,可以對系統(tǒng).進行配置使其以用戶自定義的運行(后配置)模式啟動。架構接口就是我們所熟知的動態(tài)重配置端口(DRP)。DRP是一個并行的16位同步數(shù)據(jù)端口(類似于block RAM)。

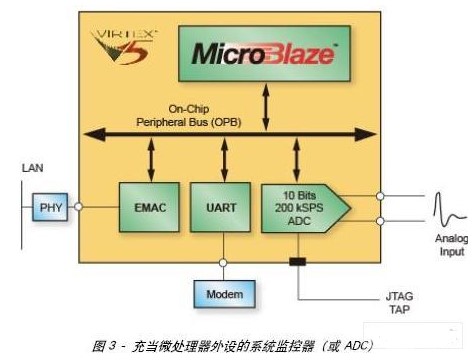

對于需要對系統(tǒng).進行更多控制的高級應用(此時)而言,DRP能夠讓系統(tǒng).輕松地映射到硬/軟微處理器的外設地址空間中。圖3顯示了一個典型系統(tǒng)管理應用,這里MicroBlaze處理器運行一個類似于協(xié)議的智能平臺管理接口(IPMI),并且通過管理通道(如以太網(wǎng),甚至是簡單的UART/調制解調器)與系統(tǒng)主機進行通信。

系統(tǒng).還以通用ADC的形式提供了一個重要的微處理器外設。這是業(yè)界首次將微控制器中常見的模擬外設集成到FPGA中。此外,該系統(tǒng)還可以完全控制ADC操作。ADC提供了大量采樣模式,并且支持單極、雙極和全差分模擬輸入方案。

本文小結

Virtex-5系統(tǒng).為一般的片上和外部環(huán)境監(jiān)控需求提供了一個大大簡化了的解決方案。其功能訪問需要極少的開發(fā)和設計工作。通過將系統(tǒng).和JTAG TAP控制器連接在一起,JTAG功能已經(jīng)延伸到新的應用領域,從而實現(xiàn)了新的測試能力。我們非常希望收到您對本文所提到的任何專題的意見和反饋信息,特別是我們的開發(fā)隊伍如何更好地為您的系統(tǒng)監(jiān)控和測試需求提供支持。

-

傳感器

+關注

關注

2562文章

52560瀏覽量

763680 -

FPGA

+關注

關注

1643文章

21960瀏覽量

614061 -

微處理器

+關注

關注

11文章

2370瀏覽量

83848

發(fā)布評論請先 登錄

如何使用的是Virtex-5 FPGA

在Virtex-5 FPGA中如何使用BRAM代替SRAM

如何利用Virtex-5系統(tǒng)監(jiān)控器加強系統(tǒng)管理和診斷?

Stratix III FPGA與Xilinx Virtex-5之間有什么不同?

Xilinx Virtex-5 FXT FPGA開發(fā)方案

Virtex-5, Spartan-DSP FPGAs Ap

Opal Kelly推出基于Virtex-5的USB集成模塊

基于Virtex-5 FPGA的音視頻監(jiān)視系統(tǒng)設計

利用Virtex-5 SXT 的高性能DSP解決方案

WWP248 - 移植到Virtex-5 FPGA的指南

WP245 - 使用Virtex-5系列FPGA獲得更高系統(tǒng)性能

基于賽靈思Virtex-5的音視頻監(jiān)視系統(tǒng)設計的詳細分析

Virtex-5系列FPGA CLB芯片的數(shù)據(jù)手冊免費下載

digilent Virtex-5 FPGA開發(fā)板簡介

利用Virtex-5系統(tǒng)監(jiān)控FPGA及其外部環(huán)境的管理和診斷

利用Virtex-5系統(tǒng)監(jiān)控FPGA及其外部環(huán)境的管理和診斷

評論