7月17-18日,在中國規(guī)模最大、規(guī)格最高的RISC-V峰會上,芯華章向數千名專業(yè)用戶展示其面向RISC-V指令集打造的完整敏捷驗證方案,其中最新發(fā)布的GalaxSim Turbo 3.0創(chuàng)新性地結合事件驅動和周期驅動雙引擎在仿真性能上的優(yōu)勢,以自動負載調度算法提升并行仿真效率,在周期加速場景中,相比于傳統(tǒng)商業(yè)仿真器相比可實現十倍以上的驗證效率提升。

GalaxSim Turbo 3.0

雙仿真引擎兼顧性能和易用性

隨著現在設計復雜性的提高,傳統(tǒng)的邏輯仿真器產品在很多場景下受限于事件的異步行為,設計的分割(Partition)和線程同步有較大的限制,往往無法支持高速的并行仿真,從而大大限制了驗證的場景和規(guī)模。

GalaxSim Turbo高速仿真模式讓用戶在不需要修改驗證環(huán)境的情況下,大幅提高了仿真并行度。同時混合仿真模式兼顧了傳統(tǒng)仿真器對SystemVerilog語法和UVM特性的支持,結合XEDB波形合并、功能覆蓋率分析等一系列實用的調試工具,有效確保了驗證流程的連貫性。

使用門檻更低

支持Verilog/SystemVerilog全語法,額外支持SVA,Functional Coverage等Verilator沒有的功能,同時可在原先的仿真用例上可以一鍵切換;

易用性更強

不局限C Testbench,驗證環(huán)境的移植平滑,維護成本大大降低;

并行效率高

Verilator線程數目需要編譯前指定,Turbo的線程數目可以在RunTime的時候根據服務器資源指定,大大提高多線程的管理效率;

仿真運行速度更快

在拆分設計之前對設計描述方式和信號同步機制進行深度優(yōu)化,同時可以根據客戶設計特點進行特殊的定向優(yōu)化;

運行資源管理優(yōu)化

運行時可以自動尋找合適的CPU資源,并得到計算資源,通訊資源的優(yōu)化匹配;

調試能力強

支持并行下載芯華章波形文件格式XEDB,波形文件大幅減小,下載速度顯著提升,得到完整的一體化Debug體驗。

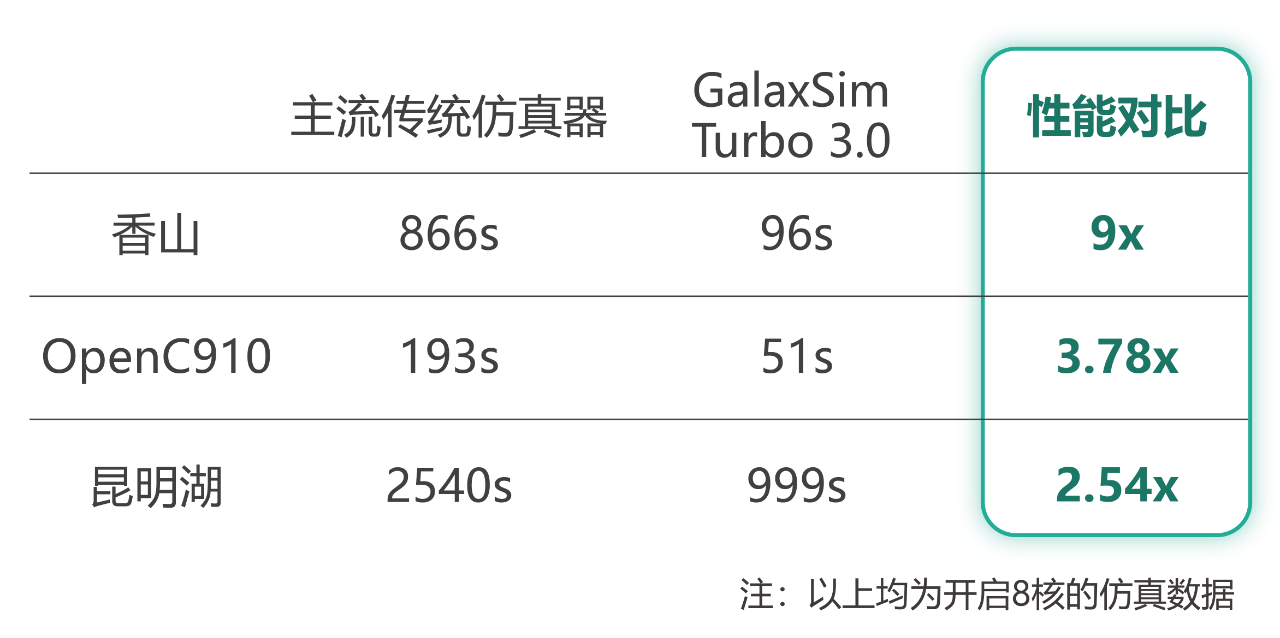

表1:RISC-V開源項目實踐,驗證效率顯著提升

芯華章科技聯(lián)席CEO謝仲輝表示:“在科技競爭異常激烈的今天,我們以AI賦能EDA技術革新的同時,也在積極地探索具有巨大潛能的應用場景,以更敏捷、更充分、更完備的驗證方案,保障基于RISC-V架構相關產品的穩(wěn)定性,從而助力RISC-V其獲得大規(guī)模的商業(yè)部署,發(fā)展中國自主可控的RISC-V架構芯片服務于市場。”

芯華章在與芯來、開芯院、國家集成電路設計自動化技術創(chuàng)新中心、中國科學院計算技術研究所等多家客戶深度合作中,產品也在不斷升級,幫助客戶解決從IP高度定制化到系統(tǒng)軟硬件協(xié)同驗證等一系列挑戰(zhàn)。

RISC-V 具有高度可定制化和場景復雜的特點,在AI芯片定制當中,設計者為了提高計算效率、支持如浮點運算、AI算子等特定應用需求,往往會對傳統(tǒng)處理器指令(如RISC-V)進行擴展定制,而其計算復雜度高,驗證難度大,使用傳統(tǒng)驗證方法難以做到有效完備驗證。

GalaxEC

面向EDA 2.0目標,芯華章運用新一代形式化求解算法和并行計算技術打造高性能求解引擎,GalaxEC基于形式化底層技術,能一站式滿足用戶全流程等價性驗證需求,避免多工具切換成本,幫助工程師確保不同層次設計之間的一致性,同時,GalaxEC HEC可完備驗證RISC-V處理器算子實現的正確性,包括算術邏輯單元ALU、整數運算單元及浮點運算單元等C++算法模型到RTL實現的等價性,可支持原生云部署,更好地滿足敏捷驗證與設計需要。

基于RISC-V的應用系統(tǒng)需要系統(tǒng)級驗證及軟件適配,更多軟件生態(tài)需要移植到RISC-V處理器,但由此帶來的bug是軟件問題還是硬件問題?定位和調試困難,需要更強大的軟件代碼-硬件電路聯(lián)合調試手段。

HuaPro P3

HuaPro P3采用最新一代可編程SoC芯片,結合自研的HPE Compiler工具鏈 ,可支持容量更大、速度更快、更多最新高速接口的用戶芯片設計;同時,對基于RISC-V等多種異構處理器架構的定制化高性能應用芯片,HuaPro P3的軟硬件系統(tǒng)可支持自動化和智能化的實現流程、支持靈活模塊化擴展和云部署,有效減少用戶人工投入、縮短芯片驗證周期,兼顧驗證性能和深度調試的需求。

關于第五屆RISC-V中國峰會

RISC-V中國峰會是全球三大RISC-V專業(yè)會展之一,也是中國規(guī)模最大的RISC-V年度活動。

本屆由上海開放處理器產業(yè)創(chuàng)新中心(SOPIC)主辦,旨在協(xié)同RISC-V產業(yè)鏈上下游企業(yè),共建RISC-V關鍵共性技術平臺,用開放的硬件平臺構建開源的軟件生態(tài),從而有力促進RISC-V技術的產業(yè)化應用和商業(yè)化落地。

-

soc

+關注

關注

38文章

4397瀏覽量

222923 -

仿真器

+關注

關注

14文章

1040瀏覽量

85453 -

RISC-V

+關注

關注

46文章

2590瀏覽量

48906 -

芯華章

+關注

關注

0文章

184瀏覽量

11658

原文標題:芯華章RISC-V敏捷驗證方案再升級,總體可達數量級效率提升

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

芯華章邀您共赴2025 RISC-V中國峰會

芯來科技攜手芯芒科技發(fā)布RISC-V CPU系統(tǒng)仿真平臺

智芯公司榮獲RISC-V聯(lián)盟2024年度IP創(chuàng)新獎

芯來科技亮相RISC-V Day Tokyo 2025

芯啟源亮相首屆RISC-V產業(yè)發(fā)展大會

芯華章推出新一代高性能FPGA原型驗證系統(tǒng)

國產EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統(tǒng)

《RISC-V能否復制Linux 的成功?》

思爾芯加入甲辰計劃,共推RISC-V生態(tài)

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

思爾芯亮相RISC-V中國峰會,展示架構建模與混合仿真驗證方法

芯華章RISC-V敏捷驗證方案再升級

芯華章RISC-V敏捷驗證方案再升級

評論