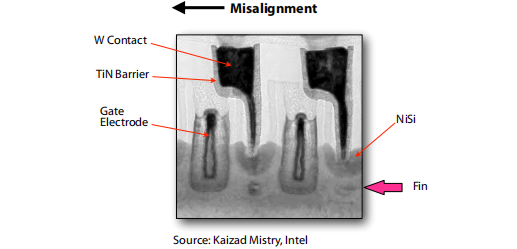

源漏區(qū)的單晶硅和柵極上的多晶硅即使在摻雜后仍然具有較高的電阻率,自對準硅化物(salicide)工藝能夠同時減小源/漏電極和柵電極的薄膜電阻,降低接觸電阻,并縮短與柵相關的RC延遲。另外,它避免了對準誤差,從而可以提高器件集成度。由于自對準硅化物直接在源漏區(qū)和柵極上形成,CMOS 器件的微縮對自對準硅化物工藝有深遠的影響。

工業(yè)界最初采用TiSi2作為標準的硅化物材料,主要應用于0.35μm 和0.25μm 技術節(jié)點。在TiSi2工藝中,由高電阻的C49相形成低電阻的C54相的過程與線寬有關。更短的柵使得從C49晶粒相到C54相是一種一維生長模式,這種相變需要更高的溫度,因此可能導致結塊并會增加窄線的RS。由于窄線條效應限制,在0.18μm 技術代 Salicide 工藝使用CoSi2取代TiSi2。

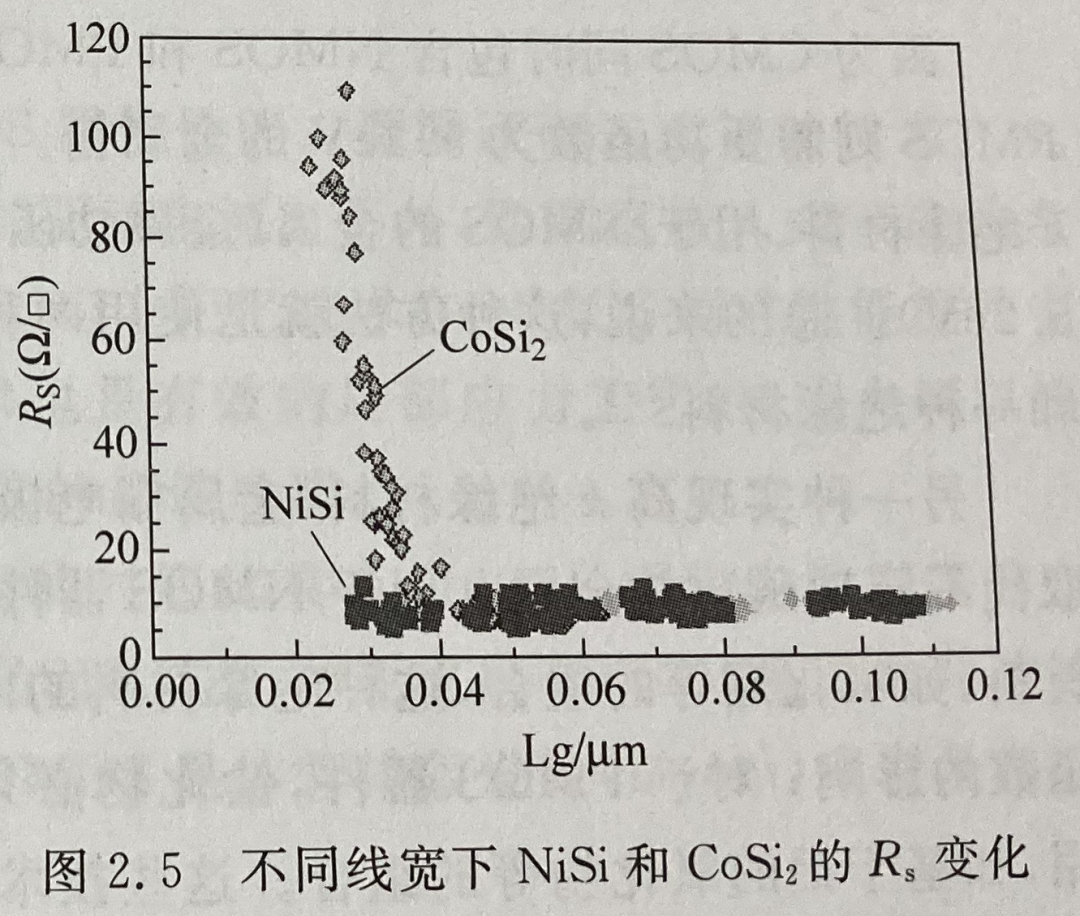

如圖 2.5所示,當線條物理寬度小于40nm 時,CoSi2在多晶硅上的薄層電阻迅速變高,而 NiSi即使到30nm以下,其電阻率仍保持在較低水平。另外,NiSi工藝中退火溫度更低,因此具有熱預算方面的優(yōu)點;同時NiSi的硅消耗相比 CoSi2,工藝降低35%左右。這對于超淺結技術來說是一個非常重要的優(yōu)點。綜上所述,在90nm 和 65nm 技術節(jié)點,NiSi 工藝取代CoSi2,工藝。

需要注意的是,NiSi 的熱穩(wěn)定性相對較差,在高于600°C時,低阻態(tài)的NiSi會轉變?yōu)楦咦钁B(tài)的NiSi2相,這一點,在工藝整合中非常關鍵。同時,NiSi需要采用新的RTP 工藝技術,如尖峰退火技術(spikeanneal)或者毫秒級退火技術(MSA),在有效地形成硅化物的基礎上,避免Ni在界面上的擴散,從而降低漏電流。

-

CMOS

+關注

關注

58文章

6021瀏覽量

238831 -

工藝

+關注

關注

4文章

681瀏覽量

29439 -

柵極

+關注

關注

1文章

185瀏覽量

21358

原文標題:自對準硅化物工藝

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

半導體制造的合金化熱處理工藝

集成電路芯片制造中的3種硅化物工藝介紹

自對準硅化物 (Self -Aligned Silicide) 工藝

半導體行業(yè)之刻蝕工藝技術

IBC技術新突破:基于物理氣相沉積(PVD)的自對準背接觸SABC太陽能電池開發(fā)

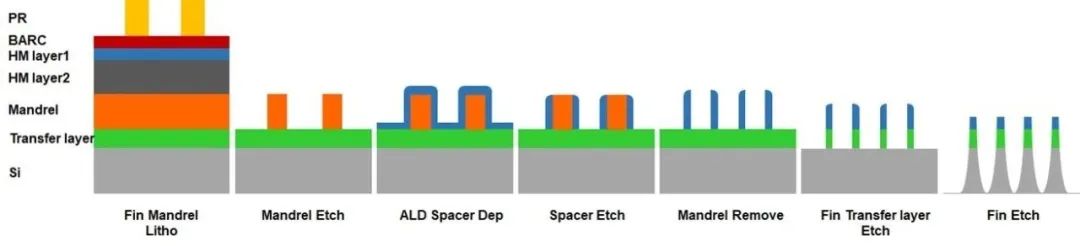

自對準雙重圖案化技術的優(yōu)勢與步驟

自對準硅化物工藝詳解

自對準硅化物工藝詳解

評論