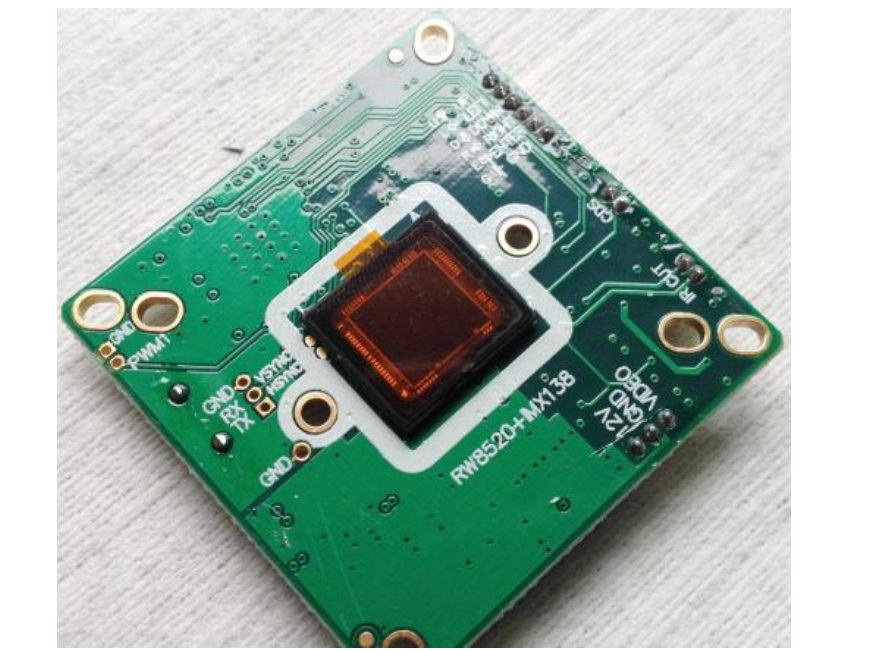

為了降低接觸電阻和串聯(lián)電阻,在集成電路制造中引入了硅化物工藝,業(yè)界先后采用了可規(guī)模生產(chǎn)的 WSi2、TiSi2、CoSi2、NiSi 等工藝。

早期發(fā)展起來的鎢硅化物工藝采用 WF6作為鎢原料,并用Si2H6作為硅原料,通過 CVD 加熱技術將其沉積到多晶硅表面后生成鎢硅化物。

在鎢硅化物工藝之后,集成電路芯片制造中主要有如下3種硅化物工藝。

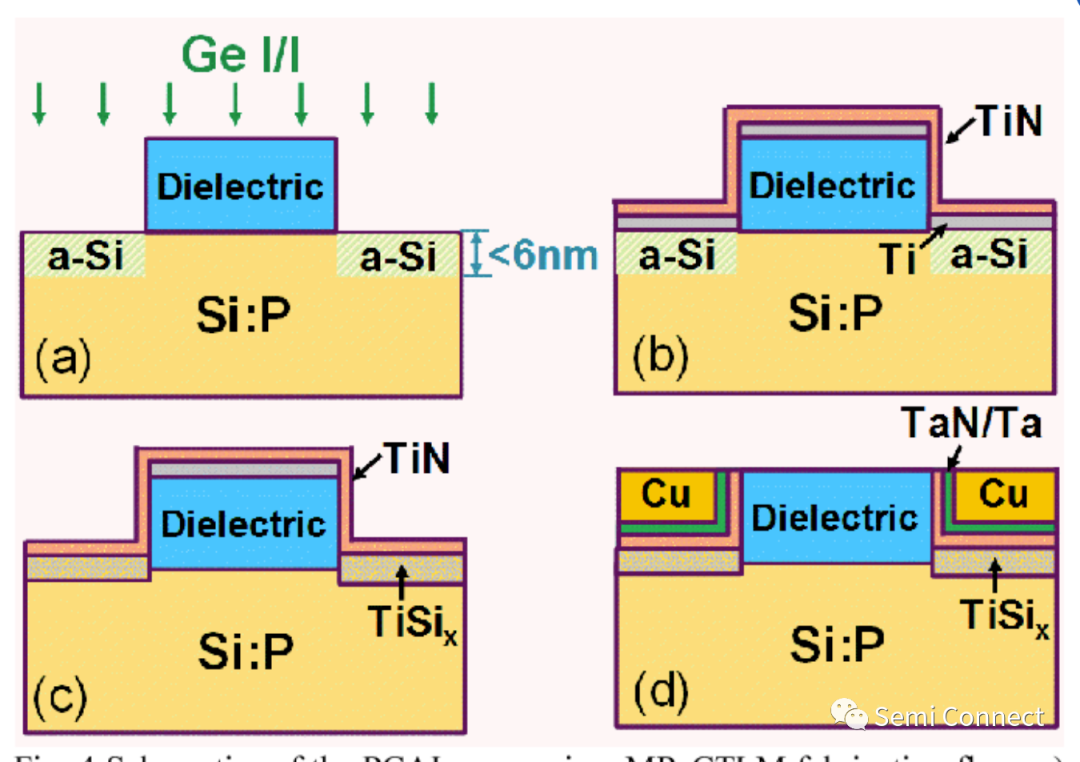

(1)鈦硅化物TiSi2工藝:廣泛應用于0.25umn 以上集成電路的制造,具有工藝簡單、高溫穩(wěn)定的特點。產(chǎn)業(yè)中的主流工藝是采用 PVD 物理濺射方法將Ti金屬沉積在晶片上形成薄膜,然后經(jīng)過兩次退火處理。

其中,第1次的退火溫度為 600~700℃,形成高阻的中間相C49;第2次退火溫度稍高,為 800-900℃,使C49相轉(zhuǎn)變?yōu)榈妥璧?C54 相。

當線寬變得過窄時,第2次退火轉(zhuǎn)變所需的溫度和時間可能大幅度增加。

但因受熱預算的限制,使得退火溫度不能過高,避免硅加劇擴散而引起漏電和短路。因此需要精密控制溫度參數(shù),尤其是隨著 MOS 尺寸變小時,應盡量控制 TiSi2相變的充分性,保證接觸電阻不會增加。

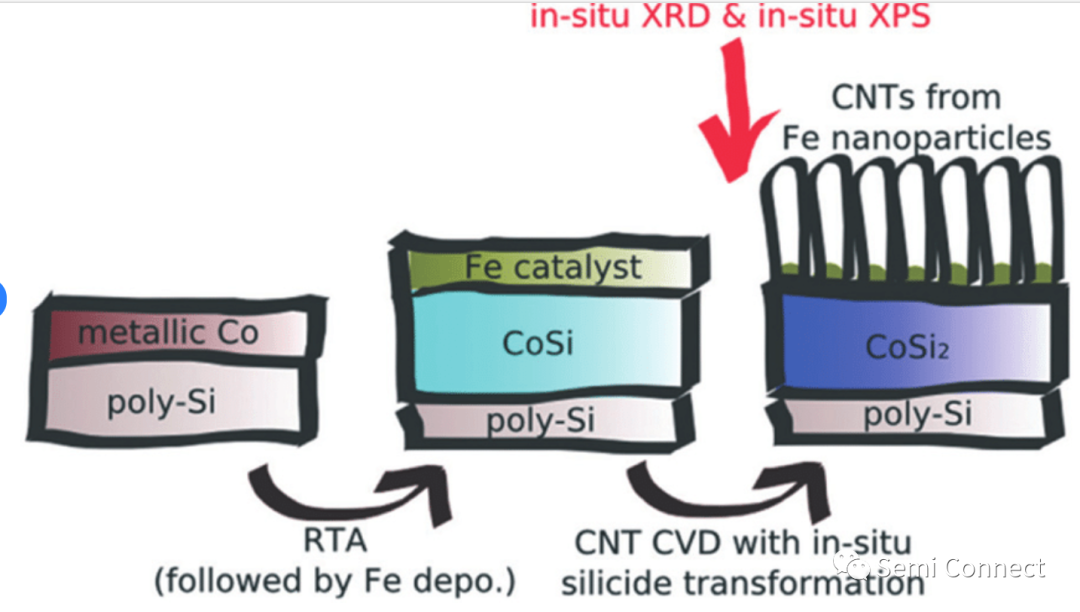

(2)鈷硅化物CoSi(x)工藝:鈷硅化物形成過程中所需的退火溫度比鈦硅化物的明顯降低,這表示該工藝具有較少的熱預算,因此 CoSi(x)可作為 TiSi2的替代品。

當芯片技術推進到 65nm/ 45nmn 節(jié)點以下時,線寬效應又顯現(xiàn)出來。

另外,當CMOS 技術進入65nm/ 45nm 及更小節(jié)點以后,有源區(qū)結深越來越淺,而鈷硅化物在形成過程中需消耗較多的高摻雜硅;同時對硅化物過程中的熱預算有更苛刻的要求,而 CoSi2需要 700℃ 以上的二次退火,因此產(chǎn)業(yè)界尋找了具有更低熱預算的替代者———鎳硅化物。

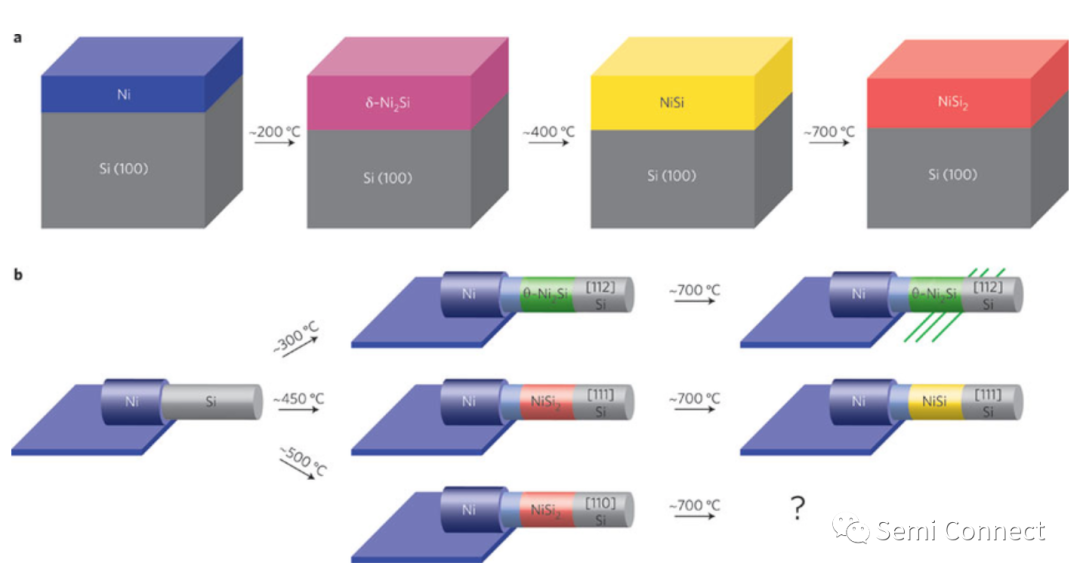

(3) 鎳硅化物 NiSi 工藝:對于 65/45nm 及以下技術節(jié)點的芯片制造工藝,為了突破鈷硅化物的工藝限制,產(chǎn)業(yè)界開發(fā)了鎳硅化物(NiSi),作為替代物,其主要優(yōu)勢在于,即使鎳硅化物工藝沿用了兩步退火,但其退火溫度比鈷硅化物工藝明顯降低(通常小于 600℃),且采用較短的退火時間,可以有效地抑制離子的擴散,降低對器件超淺結的破壞性。

鎳硅化物的第1次退火多采用尖峰退火(Spike Anneal)或激光退火(Laser Anneal),此類退火方式的升/降溫時間很短,且不再需要保持峰值溫度的時間,縮短了總退火時間,因此摻雜離子在硅化物形成過程中的擴散被有效遏制,保持了原有的摻雜剖面。

除了上述3種硅化物工藝,Ti的低溫硅化物在 14nm 及以下節(jié)點被采用,可顯著降低接觸電阻和減小漏電。這種Ti-Si 化合物不同于傳統(tǒng)的 TiSi2,其本身的電阻率并不比 NiSi 的低,但是通過改變與硅接觸的肖特基勢壘,可有效降低其接觸電阻。

審核編輯:劉清

-

串聯(lián)電阻

+關注

關注

1文章

234瀏覽量

15235 -

CVD

+關注

關注

1文章

76瀏覽量

10984 -

集成電路芯片

+關注

關注

0文章

62瀏覽量

9811

原文標題:硅化物工藝(Silicidation)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

#硬聲創(chuàng)作季 #芯片制造 IC制造工藝-1-1 集成電路制造工藝概述-集成電路制造工藝的發(fā)展

集成電路芯片制造中的3種硅化物工藝介紹

集成電路芯片制造中的3種硅化物工藝介紹

評論