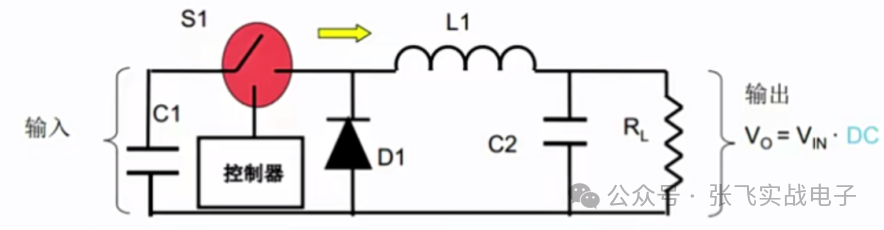

(1)BUCK降壓

狀態一:當S1閉合時,輸入的能量從電容 C1,通過 S1—>電感器 L1—>電容器 C2—>負載 RL供電,此時電感器 L1 同時也在儲存能量,可以得到加在 L1上的電壓為: Vin-Vo=L*di/dton。

狀態二:當 S2 關斷時,能量不再是從輸入端獲得,而是通過續流回路,從電感器 L1 存儲的能量—>電容 C2—>負載 RL—>二極管 D1,此時可得式子: L*di/dtoof= Vo,最后我們可以得出 Vo/Vin=D,而 Vo 永遠是小于 Vin 的,因為占空比 D≤1。

各個件的作用:

輸入電容器(C1) 用于使輸入電壓平穩;

輸出電容器(C2) 負責使輸出電壓平穩;

位二極管(D1) 在開關開路時為電感器提供一條電流通路;

電感器(L1) 用于存儲即將傳送至負載的能量;

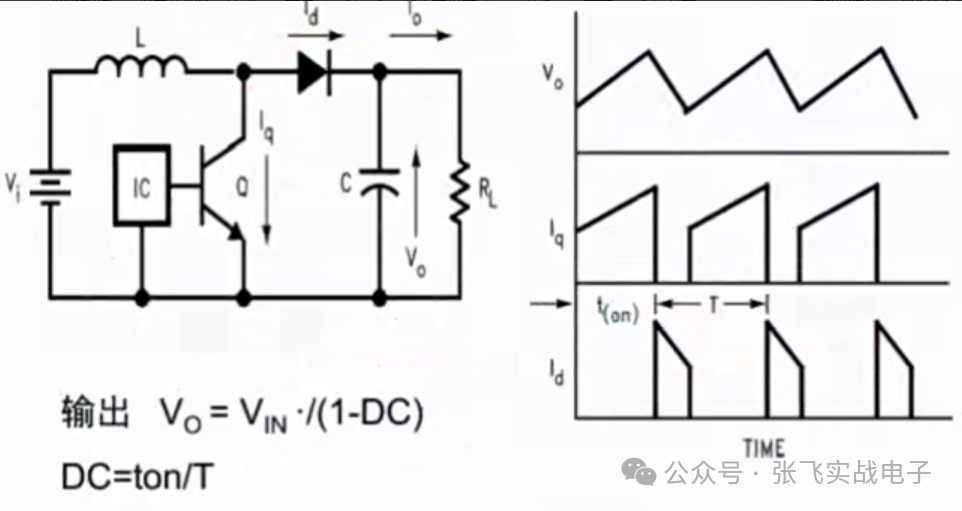

(2)BOOST升壓

下圖是升壓轉換器(Boost)的拓撲結構,電感 L是一個儲能元件,當開關管導通的時候,輸入的電壓對電感充電,形成的回路是:輸入 Vi—>電感L—>開關管 Q;當開關管關斷時,輸入的能量和電感能量一起向輸出提供能量,形成的回路是:輸入 Vi—>電感L—>二極管 D—>電容 C—>負載 RL,因此這時候輸出的電壓肯定就比輸入的電壓高,從而實現升壓。

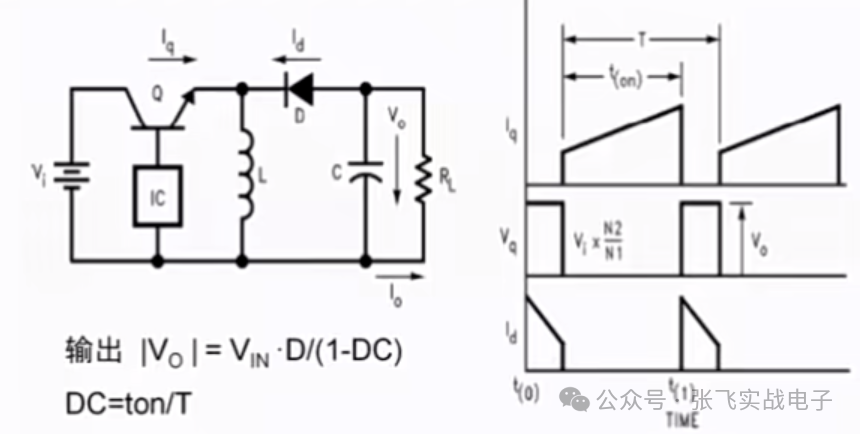

(3)BUCK-BOOST極性反轉升降壓型

狀態一: 開關管開通,二極管 D 反向截止,電感器儲能,電流回路為: 輸入 Vin —>開關管 Q—>電感器 L;

狀態二: 開關管關斷,二極管 D 正向導通續流,電流回路為:電感器 —>電容 C—>負載 RL—>二極管 D;

根據公式 Vo=VinxD/(1-D) 中知道,當D=0.5時,Vo=Vin:當D<0.5時,Vo0.5時,Vo>Vin(升壓)。這種拓撲結構我們很容易得到了負向的電壓,當某些場合不想用隔離變壓器拉抽頭的方式的時候我們可以用這種方式來實現負電壓。

二、重要傳輸

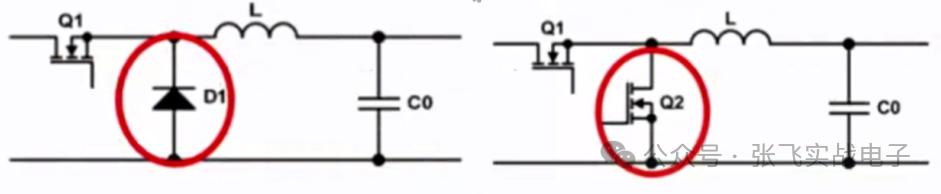

1、同步與非同步

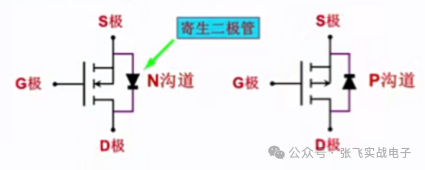

同步是采用通態電阻極低的專用功率 MOSFET,來取代整流二極管以降低整流損耗的一項新技術。它能大大提高 DC/DC 變換器的效率并且不存在由肖特基勢壘電壓而造成的死區電壓。功率 MOSFET 屬于電壓控制型器件,它在導通時的伏安特性呈線性關系。用功率 MOSFET 做整流器時,要求柵極電壓必須與被整流電壓的相位保持同步才能完成整流功能,故稱之為同步整流。

(1)同步的優缺點

①MOSFET具有較的電壓降

在 MOSFES 的參數中有一個很重要的參數那就是MOSFES 的導通電阻 Rds_on ,一般情況MOSFES 的導通電阻 Rds_on 是非常小的。一般都為毫歐級別,所以 MOSFES 在導通之后的壓降非常比較低的。

②效率高

在相同的條件下,一般的 MOS 管的導通電壓降遠運小于普通肖特基二極管的正向導通壓降的,所以在電流不變的情況下,MOS 管的損耗功率是運運比二極管小的,所以說使用 MOS 管的效率會比使用二極管的效率會高。

③需要額外的控制電路

MOS 管需要驅動電路的,所以說同步的需要為 MOS 管額外添加一個控制電路,使得上下兩個MOS 管能夠同步,而非同步的二極管是自然整流的,所以不需要額外添加驅動控制電路,所以所先對非同步,同步的電路也會比較復雜。

④成本較高

由于一般相同 MOS的價格比二極管高,而且 MOS管還需要驅動電路,驅動 IC,所以在成本上同步的比非同步的制造成本相對會貴一些,生產的流程工藝也會復雜一些。

(2)非同步的優缺點

①在輸出電流變化的情況下,極管的電壓降相當恒定

當續流二極管正向導通時,輸出電流變化,二極管的正向壓降是恒定不變的,鍺管的壓降為 0.2-0.3V,硅管的壓降為 0.7V。

②效率低

因為二極管的電壓降恒定,所以當流過二極管的電流很大的時候,原本在二極管上很小的電壓再乘以電流之后,輸出的電壓很低的時候,這時候的二極管的小電壓降就占了很大的比重,它的消耗功率就很可觀了,所以在大電流的時候效率就會減低了。

③比較便宜

大家都知道的二極管的價格肯定是比 MOS 的價格便宜的,這里說是可以是同等條件下的,大家都是用同一個襯底的情況下。

④可采用較高輸出電壓

在輸入電壓比較高的時候使用是比較好的,因為在輸出電壓高時,二極管的正向導通壓價所占的比重就很小,對效率的影響就比較低,而且它的電路結構比較簡單,不需要外加控制電路,生產的工藝流程也會比較簡單。

2、效率

如果要求效率比較高,而成本高一點無所謂的話,那么必定是要選擇的同步的。上面也提到了,MOS管損耗小,可以提高效率,但它也比較貴,成本也高。

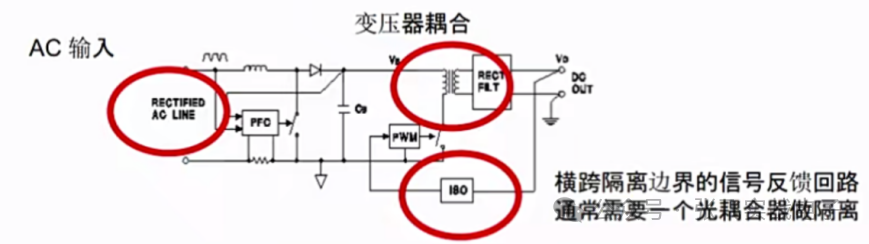

3、隔離與非隔離

由于許多應用中都需要輸入/輸出隔離,所以基于 Buck、Boost、Buck-Boost 這三種拓撲推導出了其他的常用拓撲:反激式,正激式, 推挽式,半橋式, 全橋式。

隔離式變換器在輸入和輸出之間沒有電流回路,原副邊不同地;

變壓器通過磁場將能量從初級耦合至次級隔離式變換器通常在需要提供初級至次級;

不同地,高可靠性、防雷、耐高壓等,如隔離的醫療電源;

并非標準負載點電源(POL解決方案所常用;

優點:

保護人員、設備免遭感應在隔離另一端的危險瞬態電壓損害;

去除隔離電路之間的接地環路以改善抗噪聲能力;

在系統中輕松完成輸出接線,而不與主接地發生沖突;

缺點:

體積較大,或同等體積的功率較小;

4、工作模式(Burst Mode-CCM)

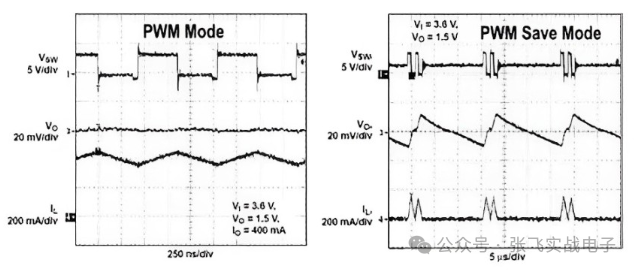

①跳躍模式PWM

在輕負載時, PWM 轉換器能自動切換至一種“低功耗”模式以最大限度地減少電池電流消耗,該模式有時被稱為“ PFM” 但實際上是一個間歇式地接通和關斷的固定頻率。

根據左邊和右邊的波形我們可以看到,左邊的是經典的 PWM 模式,右邊的圖是在輕載或者時的 PWM 跳躍模式的波形,跳躍模式中的 PWM 的頻率降低,所以開關損耗減少了。如果我們從輸出電壓紋波來看的話,紋波是變大了,因為它這種模式下已經不是每個周期都調整 PWM,而是反饋信號到了窗口比較器的上限或者下限的時候才做出調整。

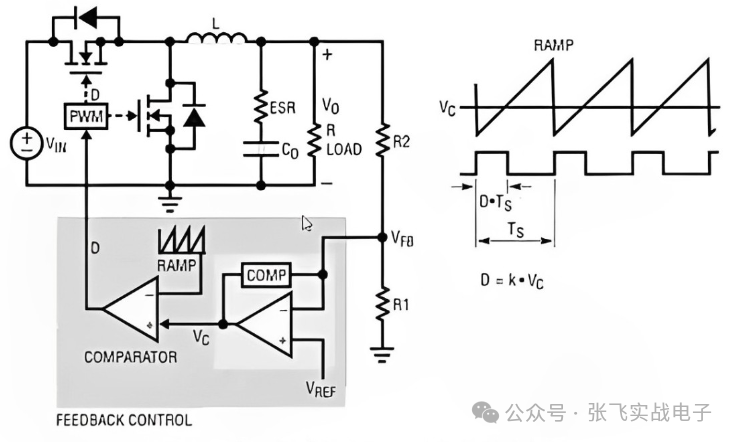

②電壓控制模式

當輸出電壓增加時,反饋電壓Vfb增加,而負反饋誤差放大器的輸出減少。因此,占空比減小。輸出電壓被拉回,使Vfb= Vref。只有一個控制環路來調節輸出。這種方案稱為電壓模式控制。

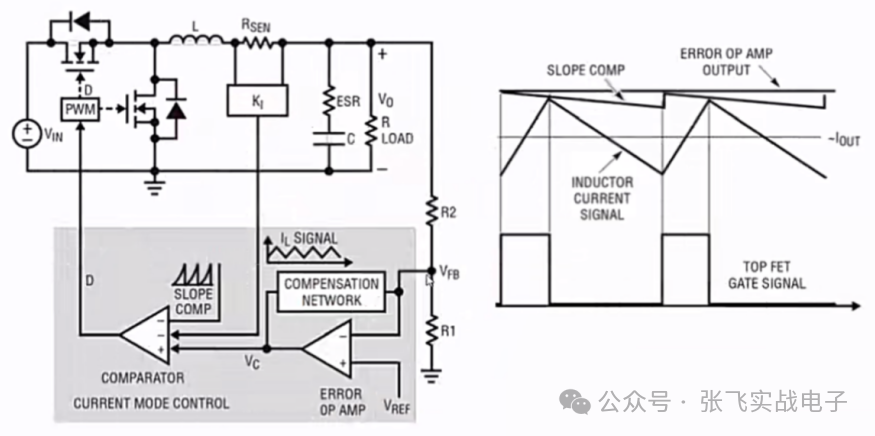

③電流控制模式

電流模式控制使用兩種反饋環路:類似于電壓模式控制轉換器控制環路的外電壓環路,以及將電流信號饋送回控制環路的內電流環路。環路補償簡單,更快速地限制電流。

5、MOSFET選擇要點

IGSS表示柵極驅動漏電流,越小越好。

VGS(th)表示的是MOS的開啟電壓。

RDS(ON)表示MOS的導通電阻,通常導通電阻越小越好,其決定MOS的導通損耗,導通電阻越大損耗越大。

6、輸入電壓,輸入電流,輸出電壓

7、功耗

8、紋波和噪聲

9、上電時序

三、DCDC芯片引腳說明(TPS54331為例)

TPS54331數據手冊鏈接:TPS54331 Datasheet(PDF) - Texas Instruments (alldatasheet.com)

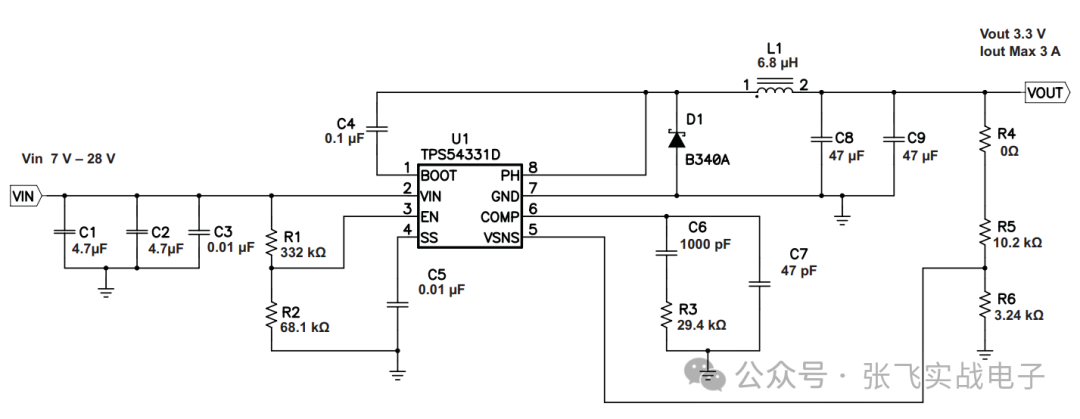

參考電路

1、EN引腳電阻

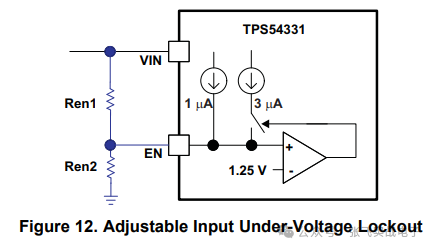

EN 引腳具有一個內部提升電流源,當EN引腳浮動時可提供TPS54331運行的默認條件。

當 VIN 引腳電壓降至內部 VIN UVLO 閾值以下時,該TPS54331被禁用。除非 VIN 大于 (VOUT + 2V),否則建議使用外部 VIN UVLO 來增加遲滯。要通過遲滯調節 VIN UVLO,請使用連接到 EN 引腳的外部電路。

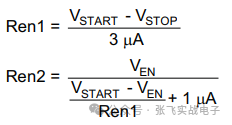

一旦EN電壓超過1.25V,就會增加額外的3uA遲滯。使用公式 可計算所需的 VIN UVLO 閾值電壓所需的電阻值。VSTART是輸入啟動閾值電壓,VSTOP是輸入停止閾值電壓,VEN是1.25V的使能閾值電壓,VSTOP應始終大于 3.5V。

2、SS引腳/緩啟動電容引腳

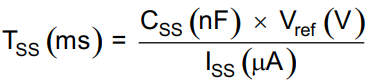

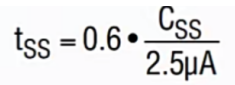

TPS54331有效地使用內部基準電壓的較低電壓或SS引腳電壓作為饋入EROR放大器的電源基準電壓,并相應地調節輸出。SS 引腳接地上的電容器 (Css) 可實現較慢的靜態時間。TPS54331具有一個 2uA 的內部提升電流源,該電流源對外部慢啟動電容器進行調節,慢啟動時間(10% 至 90%)的公式如下。Vref為0.8V,lss電流為2uA。

慢啟動時間應設置在1ms至10ms之間,以確保良好的啟動行為。起步緩慢電容器應不超過27nF。

軟啟動的設置。根據電壓啟動需要的次序設置幾個電源模塊的SS的電容。使其產生需要的上電次序。注意: 電容設置過大會造成電源啟動過緩,出現CPU啟動異常的現象。太小會出現電源啟動不起來的情況。

3、輸入電容

TPS54331需要一個輸入去耦電容,根據不同的應用,需要一個大容量輸入電容。去耦電容的典型推薦值為10uf。推薦使用高質量的陶瓷型號X5R或X7R。額定電壓應大于最大輸入電壓。只要滿足所有其他要求,就可以使用較小的值。此外,一些散裝電容可能需要,特別是如果TPS54331電路不位于約2英寸從輸入電壓源。該電容的值并不重要,但應額定以處理最大輸入電壓,包括紋波電壓,并應過濾輸出,使輸入紋波電壓是可接受的。

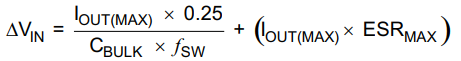

該輸入紋波電壓公式如下表示,其中lout(MAX)為最大負載電流,fsw為開關頻率,CBULK為大容量電容值,ESRmax為大容量電容的最大串聯電阻。

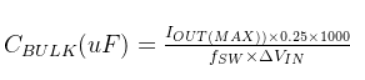

輸入電容近CBULK似計算公式:

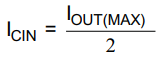

最大RMS紋波電流也需要檢查。在最壞的情況下。這可以用下面公式近似表示

同樣重要的是要注意,實際輸入電壓紋波將受到與布局和電壓源輸出阻抗相關的寄生效應的極大影響。該電路的實際輸入電壓紋波顯示在設計參數中,它大于計算值。所選的散裝電容器和旁路電容器的額定電壓均為50 V,紋波電流容量大于3a,兩者都提供了充足的余量。在任何情況下都不能超過電壓和電流的最大額定值。

4、輸出電感

需要為輸出濾波器選擇兩個組件L1 和 C2。由于TPS54331是外部的補償裝置,可以支持各種濾波器組件類型和值。

感值高 - 紋波電流小;

感值低 - 紋波電流大;

紋波電流是決定磁芯損耗的要素;

減少功率電感損耗的重要參數不僅包括開關頻率,還包括紋波電流;

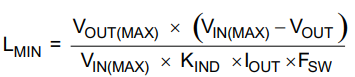

要計算輸出電感的最小值,請使用公式 :

Kind是表示電感紋波電流相對于最大輸出電流的量的系數,一般情況下,該值由設計者自行決定;但是,可以使用以下指導方針。對于使用低ESR輸出電容器(如陶瓷)的設計,可以使用高達Kip = 0.3的值。當使用更高ESR輸出電容時,Kind = 0.2產生更好的結果。

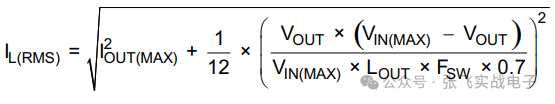

對于輸出濾波器電感來說,重要的是不要超過RMS電流和飽和電流,RMS電感電流公式如下:

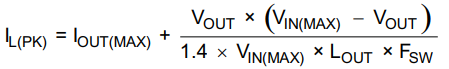

電感峰值電流公式如下:

只要滿足其他設計要求,就可以根據設計人員希望允許的紋波電流的大小使用更小或更大的電感值。較大的電感值將具有較低的交流電流并導致較低的輸出電壓紋波,而較小的電感值將增加電流和輸出電壓紋波。一般來說,用于TPS54331的電感值在6.8 uH至47uH的范圍內。

5、輸出電容

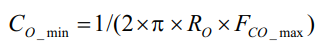

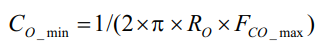

輸出電容的重要設計因素是直流額定電壓、紋波電流額定值和等效串聯電阻(ESR)。不能超過直流電壓和紋波電流,ESR很重要,因為它與電感電流一起決定了輸出紋波電壓的大小。輸出電容的實際值并不重要,但確實存在一些實際限制。考慮設計所需的閉環交叉頻率與輸出濾波器的LC角頻率之間的關系。一般來說,保持閉環交叉頻率小于開關頻率的1/5是可取的。對于高開關頻率,如本設計的570KHz頻率,tps54331的內部電路限制將實際最大交叉頻率限制在25 KHz左右。一般情況下,閉環交頻應高于由負載阻抗和輸出電容決定的轉角頻率。這限制了輸出濾波器的最小電容值為:

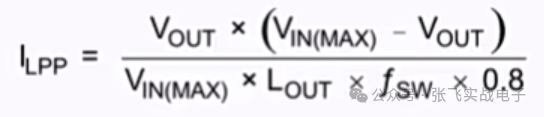

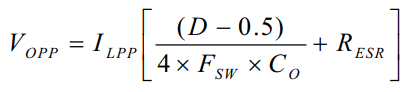

其中Ro為輸出負載阻抗(V/lo), fco為期望的交叉頻率。對于期望的最大交叉頻率為25Khz,輸出電容的最小值約為5.8uF。這可能不滿足輸出紋波電壓的要求。輸出紋波電壓計算公式如下:

式中Nc為并聯輸出電容的個數。

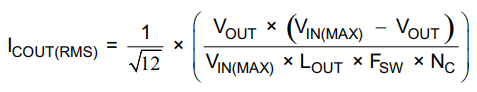

輸出電容的最大ESR由初始設計參數中規定的允許輸出紋波量決定。輸出紋波電壓為電感紋波電流乘以輸出濾波器的ESR,因此總輸出RMS紋波電流公式如下:

選擇的輸出電容額定電壓必須大于期望輸出電壓加上紋波電壓的1/2。任何降額金額也必須包括在內。輸出電容的最大有效值紋波電流由設計參數給出。

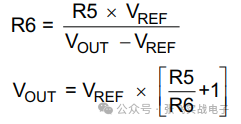

6、輸出電壓設置

TPS54331的輸出電壓是外部可調的,使用電阻分壓器網絡。參考電路中,該分頻網絡由R5和R6組成。輸出電壓與電阻分壓器的關系如式如下:(Vref=0.8V)

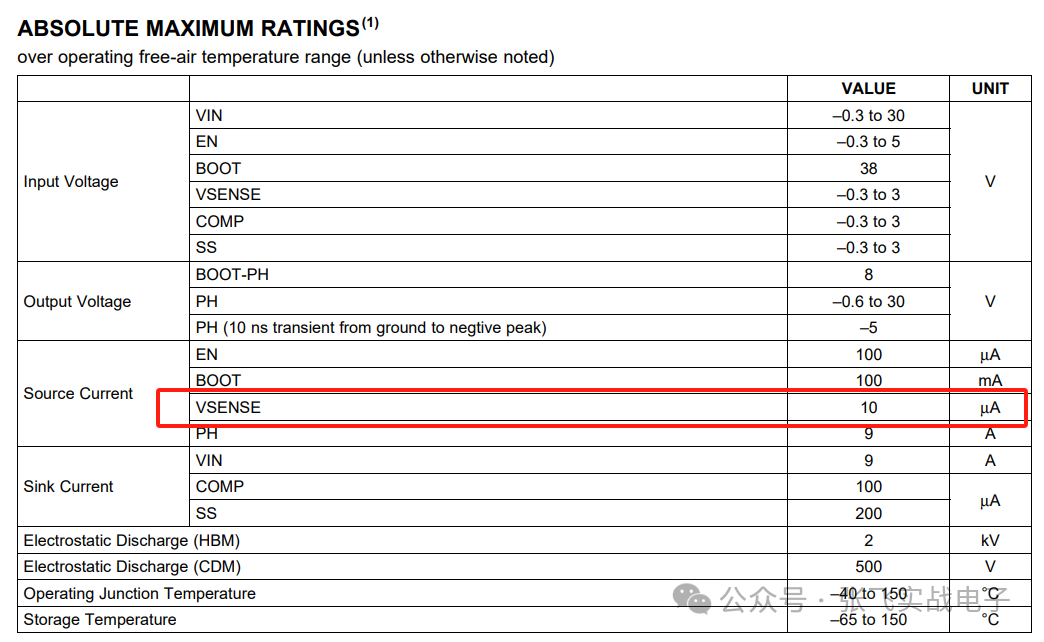

過壓保護設置(可查看第8點):R6<=VSENSE/Ivsense=0.8V/10uA=80K

當使用標準值電阻器時,稍微增加或減少R5可以導致更緊密的輸出電壓匹配。零歐姆電阻R4提供了一個方便的地方修改控制回路穩定性測試。

7、過流保護和頻移

TPS54331實現了電流模式控制,它使用COMP引腳電壓一個周期一個周期地關斷高側場效應管。每個周期比較開關電流和COMP引腳電壓,當電感電流峰值與COMP引腳電壓相交時,高位開關關閉。在拉低輸出電壓的過流條件下,誤差放大器通過驅動COMP引腳高來響應,導致開關電流增加,限制了輸出電流。

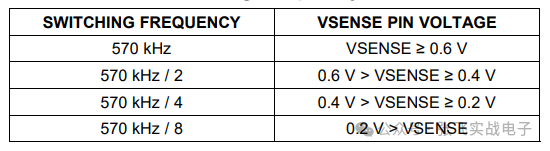

TPS54331在短路期間提供強大的保護。在輸出端短路時,輸出電感有過流失控的可能。TPS54331通過降低開關頻率來增加短路條件下的斷開時間,從而解決了這個問題。開關頻率除以2/8/4。2和1在VSENSE引腳上的電壓從0V上升到0.8V。開關頻率與VSENSE引腳電壓的關系如下。

8、過壓保護(VSENCE=0.8V/Fsw=570kHZ)

TPS54331集成了過壓瞬態保護(OVTP)電路,在從輸出故障條件或強卸載瞬態恢復時最大限度地減少輸出電壓過調。OVTP電路包括一個過電壓比較器,用于比較VSENSE引腳電壓和內部閾值。當VSENSE電壓高于109% x Vref時,高側MOSFET將被迫關閉。當VSENSE引腳電壓降至107% x Vref以下時,高側MOSFET將再次啟用。

輸出電壓設置電阻R6<=VSENSE/Ivsense=0.8V/10uA=80K(R6阻值必須小于80K)

9、剪切頻率要高于由負載阻抗和輸出電容確定的角頻率

考慮設計所需的閉環交叉頻率與輸出濾波器的LC角頻率之間的關系。一般來說,保持閉環交叉頻率小于開關頻率的1/5。對于高開關頻率,如本設計的570kHz頻率,tps54331的內部電路限制將實際最大交叉頻率限制在25 kHz左右。一般情況下,閉環交頻應高于由負載阻抗和輸出電容決定的轉角頻率。這限制了輸出濾波器的最小電容值為:

其中Ro為輸出負載阻抗(V/lo), fco為期望的交叉頻率。對于期望的最大交叉25khz,輸出電容的最小值約為5.8uF,這可能不滿足輸出紋波電壓的要求。

10、續流二極管/肖特基二極管

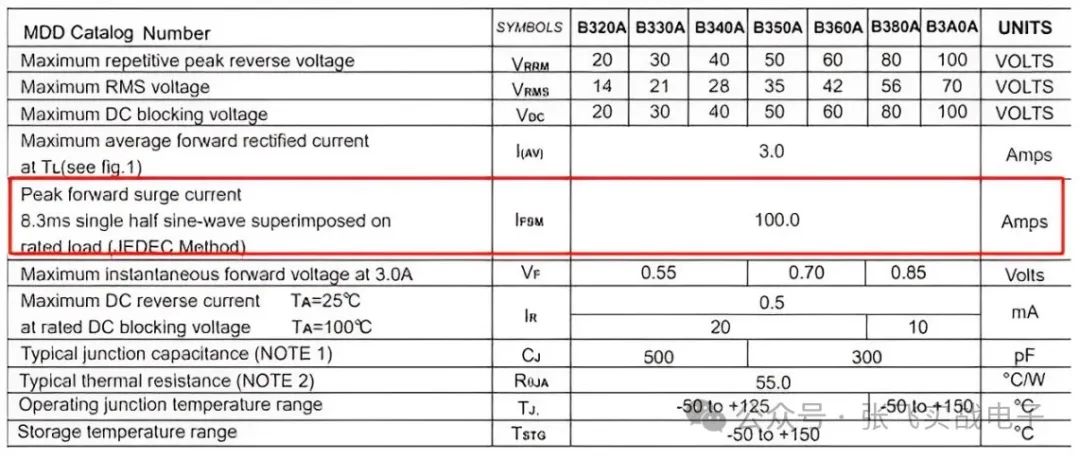

TPS54331設計用于在PH和GND之間使用外部捕獲二極管。所選二極管必須滿足應用的絕對最大額定值:反向電壓必須高于PH引腳的最大電壓,即VINMAX + 0.5 V。峰值電流必須大于lOUTMAX加上電感器峰值電流的一半。為了提高效率,正向壓降應該小。值得注意的是,捕獲二極管導通時間通常比高側場效應管導通時間長,因此注意二極管參數可以顯著提高整體效率。此外,檢查所選擇的器件是否能夠消除功率損耗。對于本設計,a二極管選用B340A,反向電壓40v,正向電流3a,正向壓降0.5 V。

11、環路設計/補償組件

環路設計指標:剪切頻率、相位裕量、增益裕量。

(1)剪切頻率:有的文檔上叫穿越頻率,是指環路增益為0dB時對應的頻率。剪切頻率越高,響應速度越快,但更容易引起環路不穩定或振蕩;剪切頻率過低,則環路瞬態響應不夠,可能導致輸出電壓異常。通常剪切頻率設計為開關頻率的1/10~1/20, 瞬態響應不足的系統往往其剪切頻率低于10KHz,此時環路處于過度補償的狀態。

(2)瞬態響應:主要表征因負載變化而引起的輸出電壓變化,瞬態響應越差,則相同負載變化引起的輸出電壓變化越大。

(3)相位/增益裕量:相位裕量一一當環路增益為0時,對應的信號相位與“180”的差值;增益裕量一一當信號相位為“0”時,對應的負增益量。表征開關電源的穩定度,如相位裕量或(和) 增益裕量不夠,則可能因溫度、PCB布局布線以及器件個體差異等影響,使系統進入不穩定或振蕩的狀態。足夠穩定的開關電源設計,一般應使相位裕量>=45°,增益裕量<=10dB。

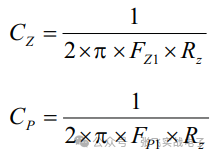

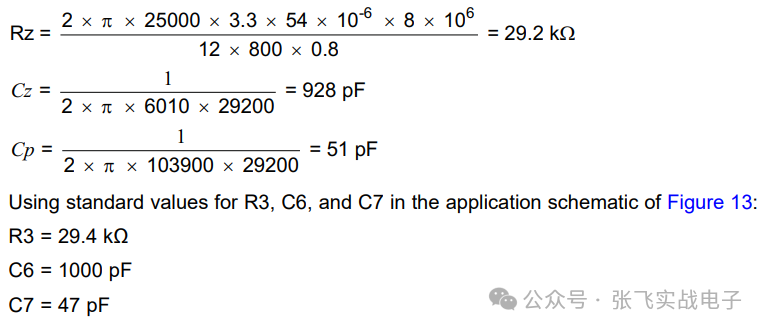

補償組件

與TPS54331一起使用的外部補償允許廣泛的輸出濾波器配置。支持電容值和電介質類型的大范圍。設計示例使用陶瓷x5r介電輸出電容器,但支持其他類型。

TPS54331建議采用ii型補償方案。選擇補償元件來設置輸出濾波器元件所需的閉環交叉頻率和相位裕度。i型補償具有以下特點:一個直流增益元件,一個低頻極和一個中頻零極對。

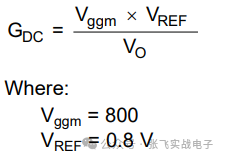

直流增益公式如下:

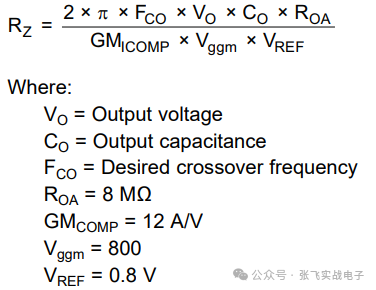

設置低頻極,使交叉頻率處的增益等于調制器和輸出濾波器增益的倒數。由于極點和零點關系所建立的關系,RZ計算公式如下:

已知RZ,則Cz和Cp計算如下:

參考電路中補償組件設計

原文鏈接:

https://blog.csdn.net/weixin_52856735/article/details/140901739

-- END --

免責聲明:本文轉自網絡,版權歸原作者所有,如涉及作品版權問題,請及時與我們聯系,謝謝!

-

電容器

+關注

關注

64文章

6531瀏覽量

101869 -

開關電源

+關注

關注

6500文章

8544瀏覽量

488510 -

DCDC

+關注

關注

29文章

867瀏覽量

72741 -

buck降壓電路

+關注

關注

1文章

9瀏覽量

5670

發布評論請先 登錄

DCDC電源模塊組成及要點

推挽式DCDC開關電源的設計與校正

電力電子技術教程---dcdc與開關電源

DCDC開關電源設計要點

DCDC開關電源設計要點

評論