今天我們要介紹的時序分析概念是setup和hold。這兩個概念大家肯定再熟悉不過了,這是兩個最基礎(chǔ)的時序分析。我們每天都要看setup和hold的timing report。那大家有沒有想過,究竟我們?yōu)槭裁匆鰏etup和hold分析?

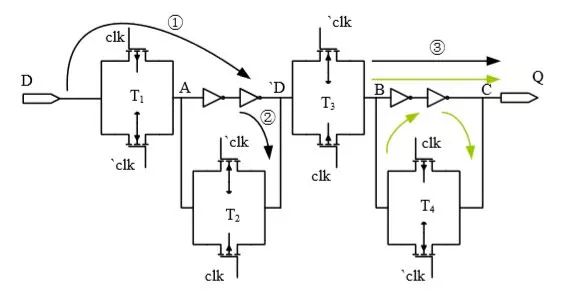

上圖是一個觸發(fā)器的簡要示意圖。其中T1,T2,T3,T4均為傳輸門,均為電平敏感,所謂的時鐘跳變可以理解為高低電平的相互跳變所致。T1和T4同時導(dǎo)通,T2和T3同時導(dǎo)通,且T1,T4和T2,T3導(dǎo)通狀況互反。而電路中實(shí)際單元的延時主要是由于電信號導(dǎo)通時通過電子器件時耗費(fèi)的時間所導(dǎo)致。

那觸發(fā)器是如何工作的呢?

低電平時,T1和T4導(dǎo)通,此時數(shù)據(jù)進(jìn)入到`D,因?yàn)榇藭rT4導(dǎo)通,由于一對反相器形成雙穩(wěn)態(tài)結(jié)構(gòu),圖中綠色箭頭線中的數(shù)據(jù)保持上一拍的數(shù)據(jù)結(jié)果。

當(dāng)高電平到來時,T1和T4關(guān)斷,T2和T3導(dǎo)通,雙穩(wěn)態(tài)結(jié)構(gòu)保證②中的數(shù)據(jù)維持穩(wěn)定,通過T3輸出至Q端,同時B點(diǎn)和C點(diǎn)的數(shù)據(jù)保持一致穩(wěn)定;當(dāng)?shù)碗娖降絹頃r,T2和T3關(guān)斷,T1和T4導(dǎo)通,因?yàn)榇藭rB點(diǎn)和C點(diǎn)數(shù)據(jù)一直穩(wěn)定,因此可以保證綠色箭頭線部分有穩(wěn)定一致的數(shù)據(jù)通過Q端發(fā)送出去。所以,可以看到在上升沿采樣的數(shù)據(jù)可以保持一個時鐘周期。

setup時間(Tsu):輸入數(shù)據(jù)D必須在時鐘上升沿之前必須有效的時間。為了得到有效的數(shù)據(jù),必須保證A點(diǎn)和`D點(diǎn)的數(shù)據(jù)保持一致穩(wěn)定。因此,可以這樣理解,所謂的建立時間是指輸入數(shù)據(jù)D經(jīng)過多長時間才能使`D的數(shù)據(jù)穩(wěn)定可靠。所以setup時間是指的是數(shù)據(jù)從D到達(dá)`D的時間。

hold時間(Thold):我們可以想象一下,在時鐘上升沿發(fā)生之后,如果A點(diǎn)的數(shù)據(jù)受到D點(diǎn)的影響,從而導(dǎo)致A點(diǎn)和D點(diǎn)數(shù)據(jù)不一致,也就是在上升沿發(fā)生后,即T2、T3導(dǎo)通時,②中循環(huán)的數(shù)據(jù)不能保持穩(wěn)定一致,從而導(dǎo)致Q端數(shù)據(jù)不穩(wěn)定。因此,hold時間可以理解為D端數(shù)據(jù)通過T1,再經(jīng)過②到達(dá)A點(diǎn),保證A和`D點(diǎn)數(shù)據(jù)一致穩(wěn)定的時間。

-

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2039瀏覽量

62142 -

Setup

+關(guān)注

關(guān)注

0文章

30瀏覽量

12234

原文標(biāo)題:時序分析基本概念介紹

文章出處:【微信號:IC_Physical_Design,微信公眾號:數(shù)字后端IC芯片設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

時序分析中的一些基本概念

建立時間和保持時間(setup time 和 hold time)

時序分析和時序約束的基本概念詳細(xì)說明

對于時序分析基本概念setup和hold的介紹

對于時序分析基本概念setup和hold的介紹

評論