一.簡介

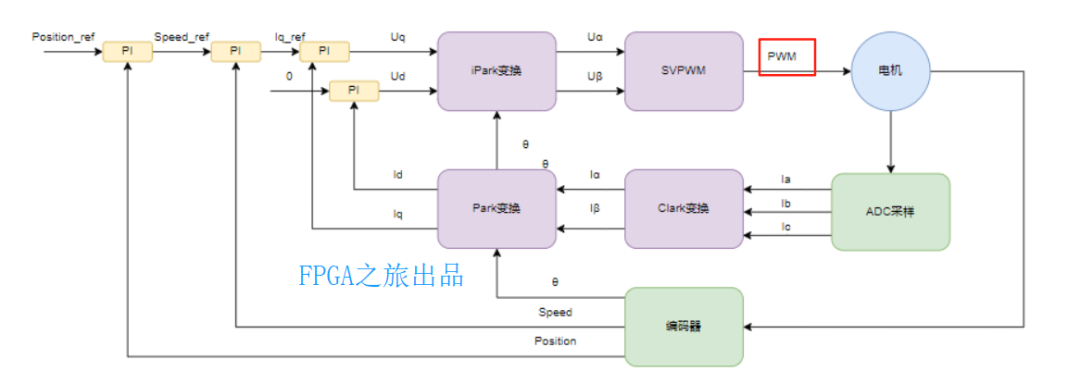

哈嘍,大家好,從今天開始正式帶領大家從零到一,在FPGA平臺上實現FOC算法,整個算法的框架如下圖所示,如果大家對算法的原理不是特別清楚的話,可以先去百度上學習一下,本教程著重介紹實現過程,弱化原理的介紹。那么本文將從PWM模塊開始進入FOC算法中去。

二. PWM模塊設計

我們知道有些驅動芯片是需要輸入互補的PWM,例如FD6288,而有些驅動芯片則只需要輸入PWM,芯片內部會自動將其轉為互補的PWM進行工作,例如DRV8313和MP6540。單路FOC開發板使用的是MP6540,多路電機驅動板使用的是FD6288,因此設計的PWM模塊需要兼容這兩種模式。

模塊端口信號如下所示,命名和工作模式借鑒了STM32定時器的工作方式。

moduletimer_top #( parameter DEFAULT_ARR =16'd1500 , //5000 parameter DEFAULT_CCR = 16'd750 , //2500 parameter COUNT_MODE ="UP" , //UP DOWN CENTRE parameter TRIG_ENABLE ="ENABLE" , //ENABLE DISABLE parameter PWM_OUT ="NONE" , //NONEP PN parameter PWM_OUT_MODE ="MODE1" , //MODE1 MODE2 parameter PWM_DEATH_TIME =3'd0 // 0 ~ 10 sys_clk )( input sys_clk_i , input sys_rst_n_i , input pwm_clk_200M_i , input timer_wr_type_i , input timer_write_en_i , input[15:0] timer_write_data_i , input timer_read_en_i , output[15:0] timer_read_data_o , output timer_trig_o , output timer_pwm_o , output reg timer_pwm_n_o );

首先給大家介紹一下端口參數

DEFAULT_ARR: 默認的定時器計數周期。

DEFAULT_CCR: 默認的定時器比較輸出值。

COUNT_MODE: 定時器工作模式,分為向上計數、向下計數和中心計數三種模式,這是和STM32的三種模式保持一致。

TRIG_ENABLE:中斷輸出是否使能,當計數器計數到CCR寄存器值的時候,是否輸出一個中斷信號。

PWM_OUT: PWM輸出,分為三種模式,其一是不輸出,其二是只輸出一路PWM,其三是輸出互補兩路PWM。

PWM_OUT_MODEL: PWM輸出的模式,也就是但計數器小于CCR的時候,是輸出高電平,還是輸出低電平。

PWM_DEATH_TIME: 死區時間,最大為10個時鐘周期,也就是50ns,加上芯片內部基本上都內置了死區補償,這個時間是夠用了的。

然后就是端口信號

sys_clk_i,sys_rst_n_i: 100Mhz系統時鐘和系統復位

pwm_clk_200M_i: PWM輸出的參考時鐘,為200Mhz,這個時鐘頻率越高,PWM的分辨率也就越高。

timer_trig_o: 中斷信號輸出

timer_pwm_o,timer_pwm_n_o: PWM信號輸出

其他:動態調整定時器的計數周期ARR和比較值CCR,從而可以調整PWM的頻率和占空比,實際使用的過程中,只會調整占空比。

2. 設計細節

PWM模塊設計原理比較簡單,其中有兩點需要注意一下,這兩點中好了 ,設計起來就毫無壓力~。

1. 跨時鐘同步: 定時器時鐘頻率為200Mhz,而系統時鐘頻率為100Mhz,模塊只會涉及到中斷信號的同步,定時器時鐘域同步到系統時鐘域下,快時鐘域同步到慢時鐘域下,也是同步場景中最為常見的一種,這里直接將脈沖信號作為使能信號,對另外一個信號進行取反,然后檢查其邊沿即可實現同步。

always@( posedge pwm_clk_200M_i or negedge sys_rst_n_i )begin

if( sys_rst_n_i ==1'b0 )

timer_trig_pluse <= 1'b0;

? ??elseif( TRIG_ENABLE ==?"ENABLE"?&& CNT == CCR_SHADOW )

? ? ? ? timer_trig_pluse <= ~timer_trig_pluse;

? ??else

? ? ? ? timer_trig_pluse <= timer_trig_pluse;

end

always@( posedge sys_clk_i or negedge sys_rst_n_i )?begin

? ??if( sys_rst_n_i ==?1'b0 ) begin

? ? ? ? timer_trig_pluse_d0 <= 1'b0;

? ? ? ? timer_trig_pluse_d1 <=?1'b0;

? ? end

? ? else begin

? ? ? ? timer_trig_pluse_d0 <= timer_trig_pluse;

? ? ? ? timer_trig_pluse_d1 <= timer_trig_pluse_d0;

? ? end

end

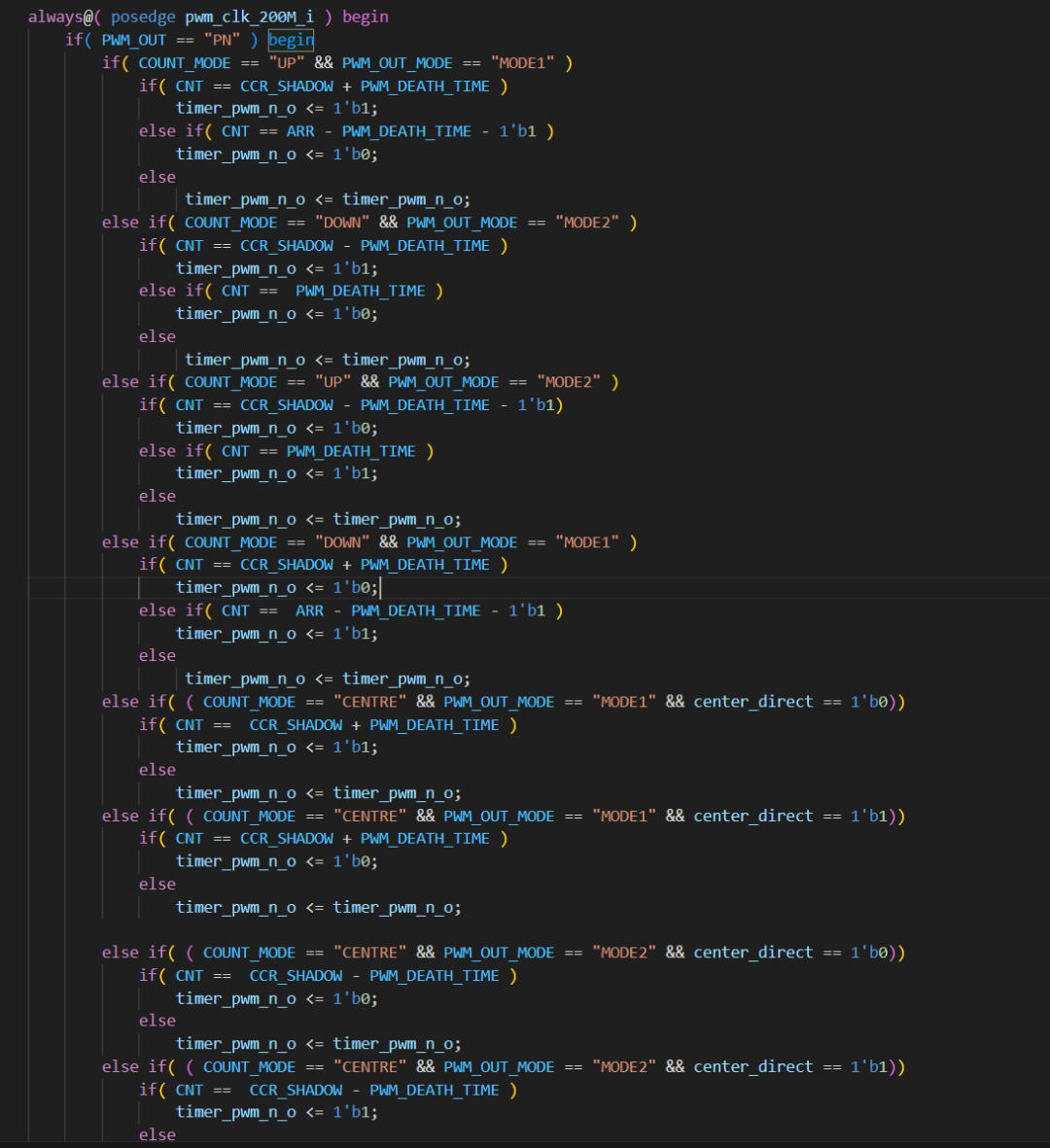

1.互補PWM輸出死區控制:死區控制的目的是為了防止短時間內兩路PWM輸出同時為高的情況發生,從而導致上下臂同時導通,了解了這個之后,就只需要將互補PWM輸出信號中,輸出為高電平的那個信號提前拉低即可,在實現的過程中要結合配置的定時器模式進行輸出,會涉及到多重判斷的情況,如下圖所示,大家可以通過多級判斷,去優化這部分時序。

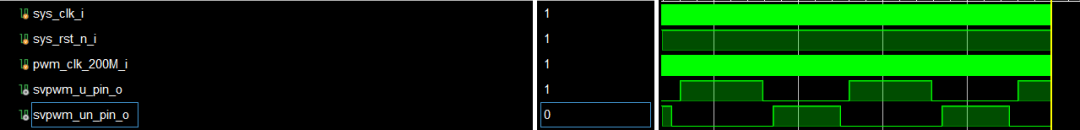

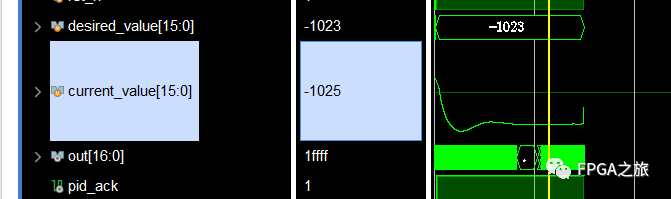

最后給大家展示一下仿真結果

來源:本文轉載自FPGA之旅公眾號

-

FPGA

+關注

關注

1645文章

22049瀏覽量

618368 -

PWM

+關注

關注

116文章

5511瀏覽量

219376 -

算法

+關注

關注

23文章

4710瀏覽量

95375 -

驅動芯片

+關注

關注

13文章

1411瀏覽量

56409

原文標題:FPGA從零到一實現FOC(一)之PWM模塊設計

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FOC 算法實現永磁同步電機調整指南

有感FOC算法學習與實現總結

STM32 Foc開源算法是什么

采用FPGA來實現SVPWM調制算法

基于FPGA 的指紋識別算法硬件實現

基于FPGA的空間矢量PWM的實現

基于FPGA的橫向LMS算法的實現

FPGA實現PID控制算法

基于FPGA實現FOC算法之PWM模塊設計

基于FPGA實現FOC算法之PWM模塊設計

評論