概述

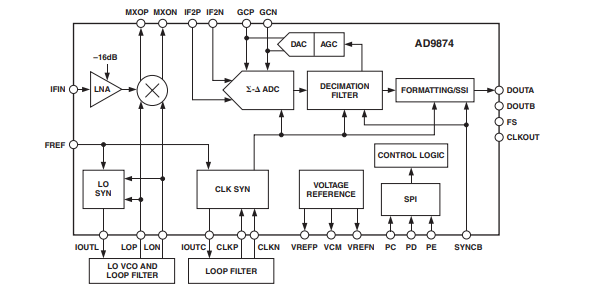

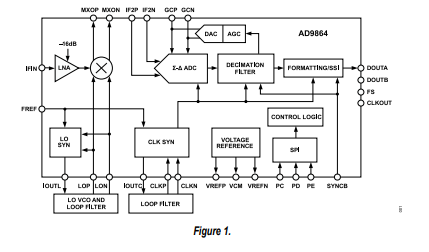

AD9874是一款通用中頻子系統,可對帶寬最高至270 kHz的低電平10至300 MHz中頻輸入信號進行數字處理。AD9874的信號鏈包括一個低噪聲放大器、混頻器、一個帶通Σ-Δ型模數轉換器以及一個具有可編程抽取系數的抽取濾波器。自動增益控制(AGC)電路提供12 dB的連續增益調整。

高動態范圍和帶通Σ-Δ型轉換器內在的抗混疊功能,使該器件能處理比目標信號強度高達95 dB的阻塞信號。除串行外設接口端口外,輔助模塊還包括時鐘和LO頻率合成器。

通過SPI端口可對AD9874的許多參數進行編程,因此該器件可針對特定應用進行優化。可編程參數包括:頻率合成器分頻比率、AGC衰減和上升/延遲時間、接收信號強度水平、抽取系數、輸出數據格式、16 dB衰減器以及所選的偏置電流。LNA和混頻器的偏置電流可以進一步降低,但電池供電應用的性能也會隨之降低。

數據表:*附件:AD9874低功耗中頻數字化子系統技術手冊.pdf

應用

特性

- 輸入頻率:10至300 MHz

- 基帶(I/Q)數字輸出

- 電源電壓:2.7 V至3.6 V

- 輸出信號帶寬:10至270 KHz

- 單邊帶噪聲系數(SSB NF):8 dB

- 三階交調截點(IIP3):+1 dBm(典型值,最大偏置)

- 動態范圍:95 dB(12 dB連續AGC范圍使能時)

- 中頻輸入:-18 dBm或-30 dBm(最大值,AGC禁用)

- LO和時鐘采樣頻率合成器

- 可編程抽取系數、輸出格式、AGC和頻率合成器設置

框圖

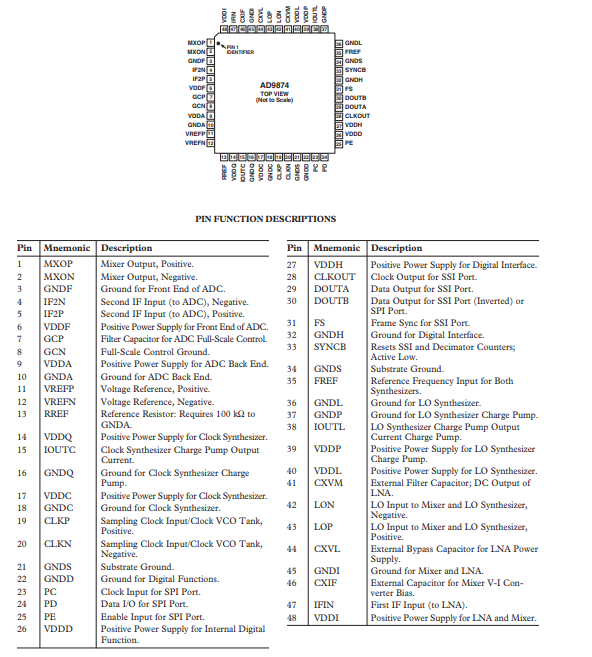

引腳配置描述

串行端口接口(SPI)

AD9874的串行端口具備三線制或四線制SPI功能,允許讀/寫訪問所有用于配置器件內部參數的寄存器。默認的三線制串行通信端口包含一個時鐘(PC)、一個主輸出從輸入(MOSI)和一個雙向數據(DT)信號。引腳PC、PE、PD默認具有一個施密特觸發器,其數字中心電壓約為0.4 V至0.5 V(由VDDH2提供)。

四線制SPI接口可通過設置輔助寄存器(Reg. 0x019,第7位)啟用,這樣輸出數據也會出現在DOUTB引腳。需要注意的是,在默認掉電狀態下,DOUTB引腳處于低電平。對于需要設置SPI輸出線以避免總線競爭的系統而言,這很有用。DOUTB引腳可通過設置輔助控制位中的第三位(Reg. 0x3B,第3位)進行三態控制,通過切換該位可訪問共享SPI輸出線。

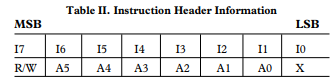

一個8位指令頭用于每次讀/寫SPI操作。只有寫操作支持自動遞增模式,允許對芯片上配置的單個寫操作進行編程。該指令頭如表II所示,包含一個讀/寫指示位、六位地址位,且不區分數據位。需要注意的是,數據位和指令位在地址位之后立即出現,且地址和數據均以最高有效位(MSB)在前的方式給出。

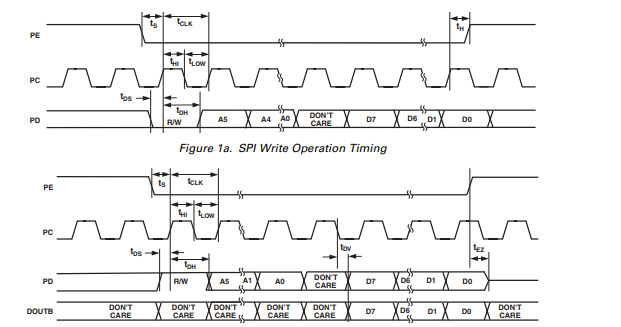

圖1a展示了向SPI端口進行寫操作的時序要求。在使能引腳(PE)信號變低后,數據(PD)與指令相關的部分在時鐘(PC)的上升沿被鎖存。要啟動寫操作,讀/寫位必須設置為低電平。發送完指定指令頭后,在接下來八個時鐘周期的上升沿,數據會移入數據引腳(PD)。PE保持低電平,直到操作完成并在第八個時鐘周期結束時變高。如果在第八個時鐘周期過去后,PE仍為低電平,則操作將再進行八個時鐘周期。

如果設置了額外的八個時鐘周期,目標地址會遞增,另外八個數據位會再次移入。此時,應忽略當前字節的其余部分,通過這種隱式尋址模式可進行整個芯片的配置操作。已確定用于控制頻率更新的寄存器,即那些與電源控制和AGC操作相關的寄存器,已被分配了相鄰地址,以盡量減少多字節寄存器(最高有效字節為最低地址)更新時所需的時間,并且在寫入最低有效字節時會進行更新。

圖1b展示了SPI端口讀操作的時序。盡管AD9874不需要讀操作來實現正確操作,但在產品開發階段或系統調試時,了解回讀數據非常有用。注意,回讀使能位(Register 0x3A,第3位)必須置位才能進行讀操作,且必須在使能引腳(PE)信號變低之前設置,數據(PD)與指令相關的部分在時鐘(PC)的上升沿被鎖存。如果讀/寫指示位為高電平,則會進行讀操作。發送完指令頭后,目標地址寄存器中的八個數據位會在接下來八個時鐘周期的下降沿出現在數據引腳(PD)上。如果啟用了四線制SPI接口,八個數據位也會出現在DOUTB引腳上,其與最后一位數據的關系與出現在PD引腳上的情況相同。在最后一位數據移出后,用戶應在讀操作完成后將PE拉高,使其恢復到正常的非選通輸入狀態。

由于自動遞增模式不支持讀操作,因此每個寄存器讀操作都需要指令頭。在讀操作完成且PE拉高之前,下一個讀操作無法啟動。

-

增益

+關注

關注

3文章

452瀏覽量

37162 -

子系統

+關注

關注

0文章

114瀏覽量

12674 -

中頻

+關注

關注

0文章

51瀏覽量

22311

發布評論請先 登錄

中頻數字化基帶硬件電路設計

AD9874,pdf datasheet (IF Digit

基于AD6623的多路中頻數字化直擴通信系統的設計與實現

發射機中頻數字化的設計與實現

基于軟件無線電的短波通信中頻數字化

中頻數字化正交解調結構介紹

AD6644做中頻數字處理模塊及接口的設計

AD9874 低功耗中頻數字化子系統

AD9864 中頻數字化子系統

AD9864中頻數字化子系統技術手冊

AD9874低功耗中頻數字化子系統技術手冊

AD9874低功耗中頻數字化子系統技術手冊

評論