概述

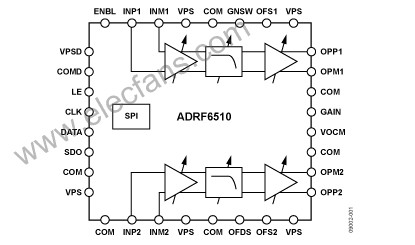

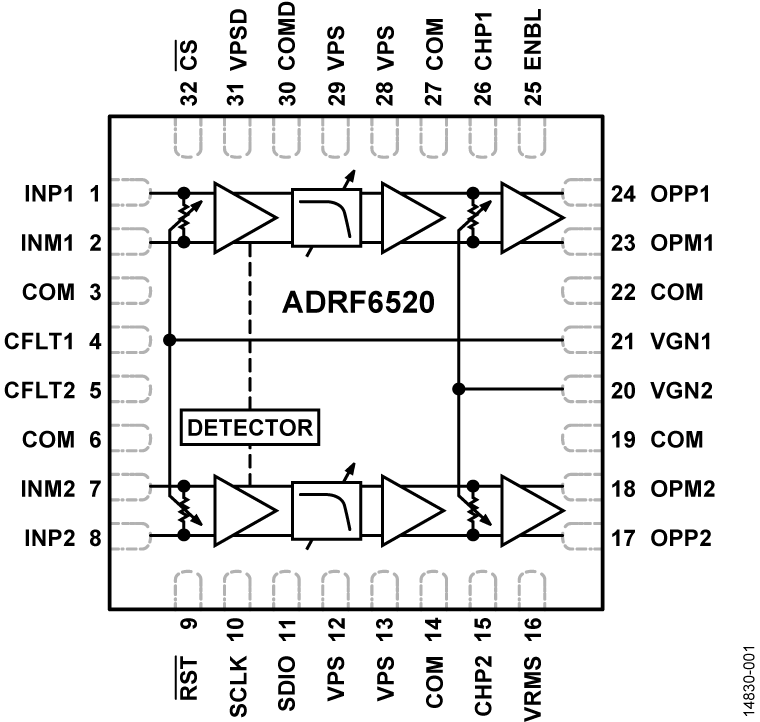

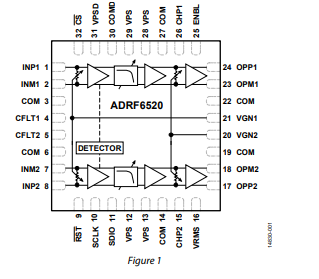

ADRF6520包括一對匹配的完全差分低噪聲、低失真可編程濾波器和可變增益放大器(VGA)。每個通道都能夠抑制較大的帶外干擾信號,同時忠實(shí)放大所需信號,因而模數(shù)轉(zhuǎn)換器(ADC)的帶寬和分辨率要求得以降低。兩個通道匹配出色,而且在所有增益和帶寬設(shè)置下都具有很高的無雜散動態(tài)范圍,因此ADRF6520非常適合具有密集星座圖、多個載波并存在鄰近干擾的正交(IQ)通信系統(tǒng)。可通過串行端口接口(SPI)編程濾波器轉(zhuǎn)折頻率、使能和直流失調(diào)校正環(huán)路使能特性。

數(shù)據(jù)表:*附件:ADRF6520 針對μW無線電2GHz通道間隔的雙通道可編程濾波器和VGA技術(shù)手冊.pdf

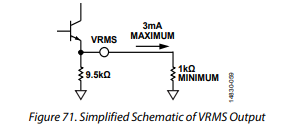

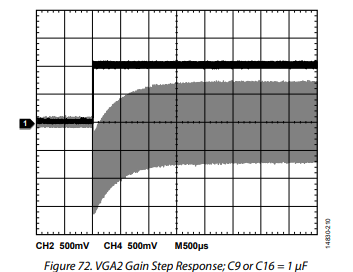

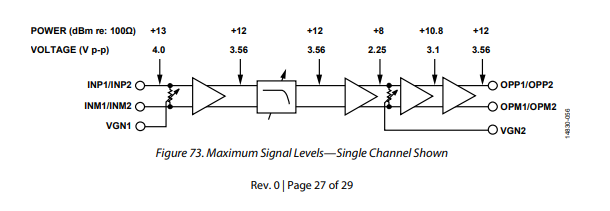

濾波器之前的第一個VGA提供27 dB的連續(xù)增益控制以及18 dB的最大增益,并設(shè)置差分輸入阻抗為100 Ω。濾波器提供4極點(diǎn)巴特沃茲響應(yīng),具有1.0 dB轉(zhuǎn)折頻率:36、72、144、288、432、576和720 MHz。對于超出720 MHz的工作頻率,可禁用并完全旁路濾波器,從而將-1 dB帶寬擴(kuò)展到1.25 GHz。提供寬帶RMS檢波器,用于監(jiān)控濾波器輸入端的信號。濾波器之后緊跟6 dB固定增益放大器。后置濾波器VGA提供27 dB的連續(xù)增益控制以及21 dB的最大增益。輸出緩沖器提供額外的9 dB增益并提供20 Ω的差分輸出阻抗。它們能夠以優(yōu)于55 dBc的HD3驅(qū)動1.5 V p-p至100 Ω負(fù)載。如果希望進(jìn)行完全直流耦合操作,可以通過SPI禁用單個通道上獨(dú)立的內(nèi)置直流失調(diào)校正環(huán)路。高通轉(zhuǎn)折頻率由引腳CHP1和CHP2引腳上的外部電容和后置濾波器VGA增益確定。

ADRF6520采用3.15 V至3.45 V電源供電,最大功耗為410 mA。完全禁用時,功耗低于5 mA。ADRF6520采用先進(jìn)的硅-鍺BiCMOS工藝制造,提供32引腳、裸露焊盤LFCSP封裝,額定溫度范圍為?40°C至+85°C。

應(yīng)用

特性

- 匹配VGA和可編程濾波器

- 連續(xù)增益控制范圍:54 dB

- 濾波器旁路模式I或Q帶寬(BW)

- ±1 dB增益平坦度:>1250 Hz

- 4極點(diǎn)巴特沃茲濾波器I或Q帶寬:36 MHz至720 MHz

- RMS檢波器

- IMD3:>55 dBc(1.5 V p-p復(fù)合輸出)

- HD2、HD3: >55 dBc(1.5 V p-p輸出)

- 噪聲系數(shù):10.4 dB(最大增益時)

- NF < 11 dB(VGA2增益回退:12 dB)

- 100Ω差分輸入、低阻抗輸出

- 可選直流輸出失調(diào)校正

- SPI可編程濾波轉(zhuǎn)折頻率和增益步進(jìn)

- 3.3 V單電源,具有關(guān)斷特性

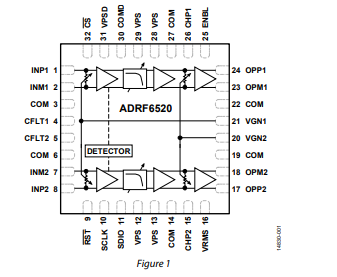

功能框圖

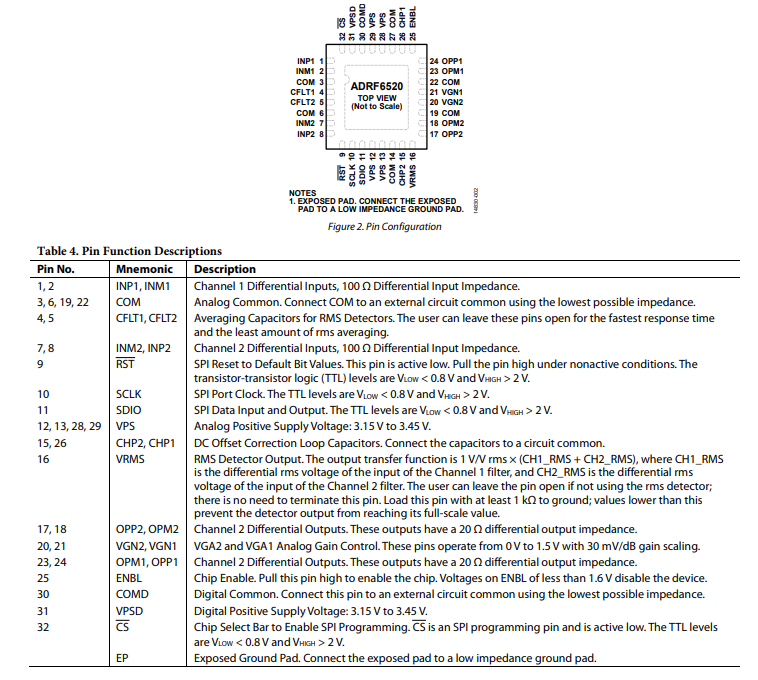

引腳配置描述

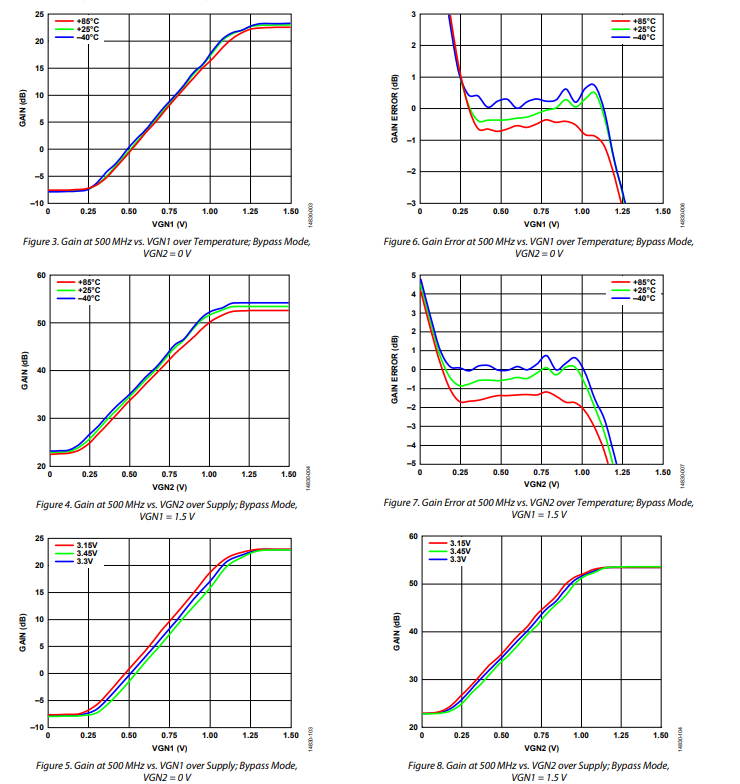

典型性能特征

應(yīng)用信息

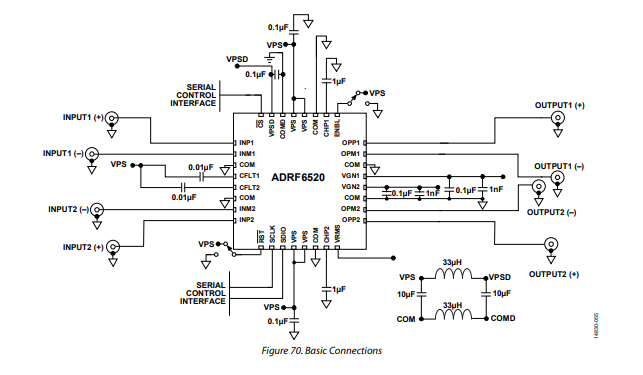

基本連接

圖70展示了典型ADRF6520應(yīng)用的基本連接。

電源去耦

向電源引腳VPS和VPSD施加3.3V的標(biāo)稱電源電壓。電源電壓不得超過3.45V或降至3.15V以下。分別對VPS和VPSD引腳進(jìn)行去耦,將至少一個低電感、表面貼裝的0.1μF陶瓷電容盡可能靠近ADRF6520器件放置到地。

ADRF6520有兩個獨(dú)立電源:一個模擬電源和一個數(shù)字電源。使用33μH的大尺寸表面貼裝電感分離模擬電源和數(shù)字電源。然后分別通過一個10μF電容將每個電源引腳去耦到各自的地。

輸入信號路徑

每個信號路徑都有一個通過INP1、INM1、INP2和INM2引腳接入的可變增益放大器(VGA),這些引腳設(shè)置了100Ω的差分輸入阻抗。

輸入可以是直流耦合或交流耦合,但交流耦合更為推薦。由于無法改變共模電壓,因此如果用戶想要進(jìn)行耦合,之前的電壓必須與ADRF6520輸入共模電壓1.375V相匹配。

輸出信號路徑

低阻抗(20Ω)輸出緩沖器旨在驅(qū)動100Ω阻抗負(fù)載,并且可以驅(qū)動較大的電阻負(fù)載。

輸出引腳(OOPP、OOMP、OOP2和OOMP2)在1.65V的標(biāo)稱共模電壓下工作。輸出可以是直流耦合或交流耦合,但交流耦合更為推薦。由于無法改變輸出共模電壓,因此如果用戶想要進(jìn)行直流耦合,共模電壓必須與ADRF6520輸出共模電壓1.65V相匹配。

直流失調(diào)補(bǔ)償環(huán)路啟用

當(dāng)通過SPI寄存器的位B5啟用直流失調(diào)補(bǔ)償環(huán)路時,ADRF6520可以消除輸出差分直流電平。通過將位B5設(shè)置為1來啟用環(huán)路。失調(diào)補(bǔ)償環(huán)路會產(chǎn)生一個高通截止頻率,該頻率與連接到CHP1和CHP2引腳至地的電容值成正比。有關(guān)設(shè)置高通截止頻率的更多信息,請參見直流失調(diào)補(bǔ)償環(huán)路部分。

串行端口連接

ADRF6520有一個SPI端口,用于控制濾波器帶寬、芯片使能和直流失調(diào)補(bǔ)償環(huán)路。數(shù)據(jù)可以寫入內(nèi)部24位寄存器并從寄存器中讀取。建議在SPI線上放置一個低通RC濾波器,以濾除任何高頻振鈴。有關(guān)低通RC濾波器的示例,請參見ADRF6520 - EVALZ用戶評估板原理圖。

應(yīng)用信息

基本連接

圖70展示了典型ADRF6520應(yīng)用的基本連接。

電源去耦

向電源引腳VPS和VPSD施加3.3V的標(biāo)稱電源電壓。電源電壓不得超過3.45V或降至3.15V以下。分別對VPS和VPSD引腳進(jìn)行去耦,將至少一個低電感、表面貼裝的0.1μF陶瓷電容盡可能靠近ADRF6520器件放置到地。

ADRF6520有兩個獨(dú)立電源:一個模擬電源和一個數(shù)字電源。使用33μH的大尺寸表面貼裝電感分離模擬電源和數(shù)字電源。然后分別通過一個10μF電容將每個電源引腳去耦到各自的地。

輸入信號路徑

每個信號路徑都有一個通過INP1、INM1、INP2和INM2引腳接入的可變增益放大器(VGA),這些引腳設(shè)置了100Ω的差分輸入阻抗。

輸入可以是直流耦合或交流耦合,但交流耦合更為推薦。由于無法改變共模電壓,因此如果用戶想要進(jìn)行耦合,之前的電壓必須與ADRF6520輸入共模電壓1.375V相匹配。

輸出信號路徑

低阻抗(20Ω)輸出緩沖器旨在驅(qū)動100Ω阻抗負(fù)載,并且可以驅(qū)動較大的電阻負(fù)載。

輸出引腳(OOPP、OOMP、OOP2和OOMP2)在1.65V的標(biāo)稱共模電壓下工作。輸出可以是直流耦合或交流耦合,但交流耦合更為推薦。由于無法改變輸出共模電壓,因此如果用戶想要進(jìn)行直流耦合,共模電壓必須與ADRF6520輸出共模電壓1.65V相匹配。

直流失調(diào)補(bǔ)償環(huán)路啟用

當(dāng)通過SPI寄存器的位B5啟用直流失調(diào)補(bǔ)償環(huán)路時,ADRF6520可以消除輸出差分直流電平。通過將位B5設(shè)置為1來啟用環(huán)路。失調(diào)補(bǔ)償環(huán)路會產(chǎn)生一個高通截止頻率,該頻率與連接到CHP1和CHP2引腳至地的電容值成正比。有關(guān)設(shè)置高通截止頻率的更多信息,請參見直流失調(diào)補(bǔ)償環(huán)路部分。

串行端口連接

ADRF6520有一個SPI端口,用于控制濾波器帶寬、芯片使能和直流失調(diào)補(bǔ)償環(huán)路。數(shù)據(jù)可以寫入內(nèi)部24位寄存器并從寄存器中讀取。建議在SPI線上放置一個低通RC濾波器,以濾除任何高頻振鈴。有關(guān)低通RC濾波器的示例,請參見ADRF6520 - EVALZ用戶評估板原理圖。

-

放大器

+關(guān)注

關(guān)注

145文章

14099瀏覽量

216254 -

增益放大器

+關(guān)注

關(guān)注

2文章

152瀏覽量

29470 -

VGA

+關(guān)注

關(guān)注

5文章

572瀏覽量

64184

發(fā)布評論請先 登錄

請教關(guān)于濾波器ADRF6520問題

ADRF6510: 30 MHz 雙通道可編程濾波器和可變

ADRF6520 針對μW無線電2 GHz通道間隔的雙通道可編程濾波器和VGA

ADRF6520:2 GHz通道間距的雙可編程濾波器和VGA,適用于μW無線電數(shù)據(jù)表

UG-1045:評估ADRF6520雙通道、可編程低通濾波器和VGA,用于微波無線電的2 GHz通道間距

ADRF6520針對μW無線電2GHz通道間隔的雙通道可編程濾波器和VGA技術(shù)手冊

HMC1023LP5E 72MHz雙通道可編程低通濾波器技術(shù)手冊

ADRF6520 針對μW無線電2GHz通道間隔的雙通道可編程濾波器和VGA技術(shù)手冊

ADRF6520 針對μW無線電2GHz通道間隔的雙通道可編程濾波器和VGA技術(shù)手冊

評論