在高速數字電路設計中,信號走線的長度是一個至關重要的考量因素。隨著數據傳輸速率的不斷提升,信號完整性、時序準確性和系統可靠性等方面的挑戰也隨之增加。本文將深入探討高速信號走線長度優化的重要性,解析為何在高速電路中,走線越短通常越有利,并提供相關的技術背景和設計指導。

一、高速信號傳輸的挑戰

在高速數字電路中,信號傳輸面臨諸多挑戰,主要包括信號衰減、信號失真、時序偏差和電磁干擾(EMI)等。這些挑戰直接影響到信號的完整性、系統的性能和可靠性。

信號衰減:高速信號在傳輸過程中,由于線路損耗、介質損耗和輻射損耗等因素,信號幅度會逐漸減小。過長的走線會增加信號衰減的可能性,導致信號質量下降。

信號失真:信號失真通常由于阻抗不匹配、信號反射和電磁干擾等因素引起。在高速電路中,較長的走線更容易受到這些因素的影響,導致信號波形變形,進而影響系統性能。

時序偏差:信號在導線中是以一定速度傳播的,線長越長,信號從發送端到接收端的延遲就越大。在高速數字電路中,這種延遲可能導致時序偏差,使得接收端無法正確識別信號,進而影響系統的正常工作。

電磁干擾:高速信號走線越長,作為天線接收外界電磁干擾的可能性就越大。這些干擾可能破壞信號的完整性,導致數據傳輸錯誤或系統失效。

二、走線長度優化的重要性

鑒于上述挑戰,優化高速信號走線長度顯得尤為重要。以下是走線長度優化帶來的主要好處:

提高信號完整性:較短的走線可以減少信號衰減和失真的可能性,從而提高信號的完整性。這有助于確保數據在傳輸過程中保持準確和可靠。

改善時序性能:較短的走線可以減少信號延遲,從而改善時序性能。這對于確保系統在高速數據傳輸下保持正常工作至關重要。

降低電磁干擾:較短的走線可以減少作為天線接收外界電磁干擾的可能性,從而降低電磁干擾對系統性能的影響。

簡化電路板設計:較短的走線有助于簡化電路板設計,減少布局和布線的復雜性。這有助于提高設計效率,降低生產成本。

三、設計指導與實踐

為了優化高速信號走線長度,以下是一些設計指導和實踐建議:

盡量縮短走線長度:在電路板設計中,應盡量縮短高速信號走線的長度,以減少信號衰減、失真和延遲等問題。

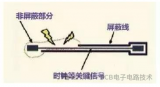

采用差分信號傳輸:差分信號傳輸可以有效地抑制共模噪聲和電磁干擾,提高信號的抗干擾能力。在高速電路設計中,應優先考慮采用差分信號傳輸方式。

合理控制阻抗匹配:阻抗匹配是確保信號完整性的關鍵因素之一。在高速電路設計中,應合理控制走線的阻抗,以避免信號反射和失真等問題。

采用屏蔽和接地措施:屏蔽和接地措施可以有效地降低電磁干擾對系統性能的影響。在高速電路設計中,應考慮采用屏蔽走線和接地層等措施來提高系統的抗干擾能力。

仿真與測試:在電路板設計完成后,應進行仿真和測試以驗證走線長度優化的效果。通過仿真和測試,可以發現并解決潛在的問題,確保系統在實際應用中具有優良的性能和可靠性。

審核編輯:陳陳

-

走線

+關注

關注

3文章

118瀏覽量

24198 -

高速數字電路

+關注

關注

1文章

14瀏覽量

10009 -

數字電路設計

+關注

關注

0文章

22瀏覽量

12737

發布評論請先 登錄

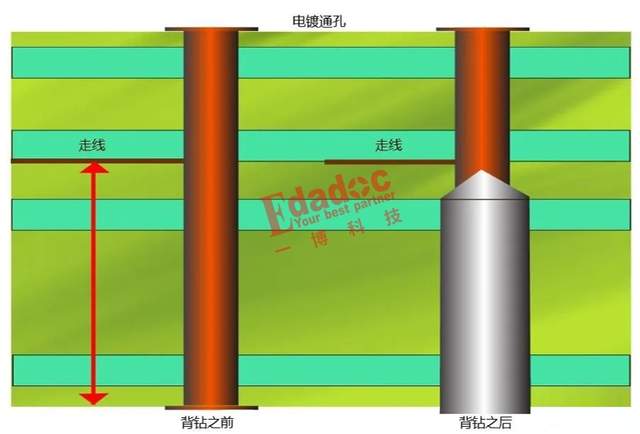

背鉆設計時要優先保證哪一項,STUB長度真的是越短越好嗎

背鉆設計時要優先保證哪一項,STUB長度真的是越短越好嗎

在進行高速信號放大設計時,往往需要用到反饋電路,是否反饋電路越短越好?

高速PCB信號走線的九大規則

高速信號走線越短越好嗎為什么

高速信號走線越短越好嗎為什么

評論