本文介紹了銅互連雙大馬士革工藝的步驟。

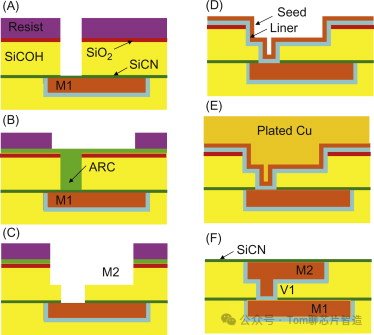

如上圖,是雙大馬士革工藝的一種流程圖。雙大馬士革所用的介質(zhì)層,阻擋層材質(zhì),以及制作方法略有差別,本文以圖中的方法為例。

(A) 通孔的形成 在介質(zhì)層(如SiCOH)上沉積光刻膠(Resist),并使用光刻工藝做出掩模圖形。通過干法刻蝕手段,得到通孔。

(B)制作溝槽所需的圖形 完成通孔的刻蝕后,通常會去除原來的光刻膠。旋涂抗反射層,并將通孔填滿,之后會再次涂布光刻膠,做出開槽所需的光刻膠圖形。

(C) 開溝槽 干法刻蝕除去多余的抗反射層,介質(zhì)層等,并去除晶圓表面光刻膠。

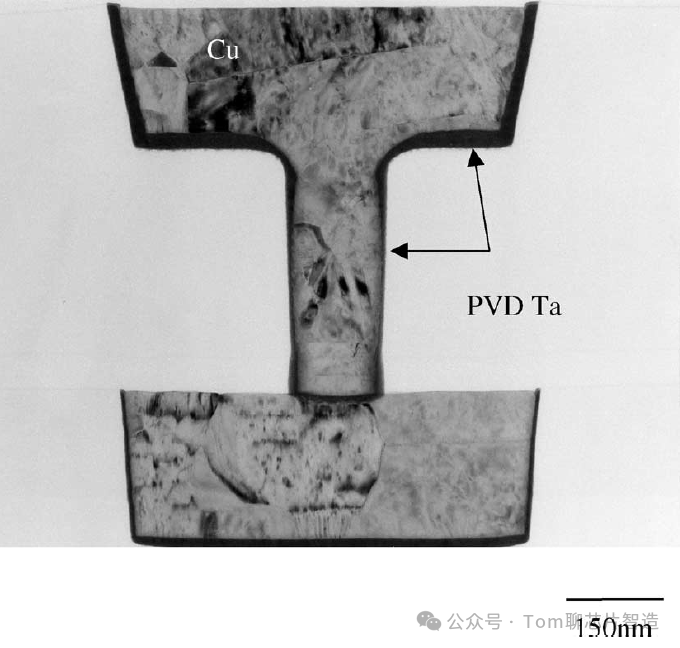

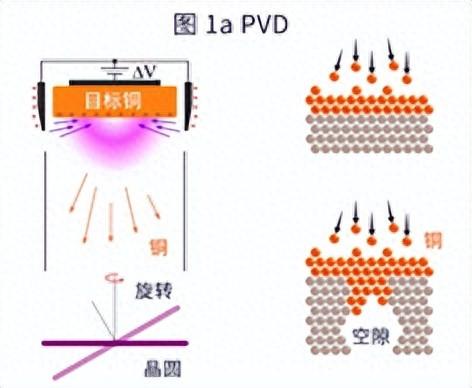

(D) 沉積種子層 在刻蝕好的溝槽和通孔內(nèi),使用PVD或CVD沉積Cu種子層和阻擋層。Cu種子層用于電鍍的導(dǎo)電材料。阻擋層主要是Ta或TaN,用于防止銅擴(kuò)散。

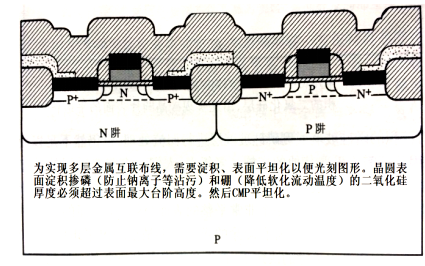

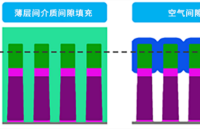

(E) 電鍍銅 使用電鍍工藝,將銅填充到通孔和溝槽中。銅完全填滿后,表面會有過量的銅。使用CMP工藝去除多余的銅和種子層,只保留通孔和溝槽中的銅。

(F)cmp拋光 cmp拋光后,在表面覆蓋阻擋層。

-

電鍍銅

+關(guān)注

關(guān)注

0文章

26瀏覽量

9237 -

光刻工藝

+關(guān)注

關(guān)注

1文章

34瀏覽量

1942 -

銅

+關(guān)注

關(guān)注

0文章

3瀏覽量

1765

原文標(biāo)題:銅互連雙大馬士革工藝步驟

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

一文詳解銅大馬士革工藝

鐵匠鋪鍛打大馬士革花紋鋼酸洗之后花紋確實(shí)夠漂亮鍛打?鐵匠?大馬士革? #硬聲創(chuàng)作季

如何采用銅互連單大馬士革工藝制作超厚金屬銅集成電感的概述

12吋晶圓集成電路芯片制程工藝與工序后端BEOL的詳細(xì)資料說明

實(shí)現(xiàn)3nm技術(shù)節(jié)點(diǎn)需要突破哪些半導(dǎo)體關(guān)鍵技術(shù)

華進(jìn)半導(dǎo)體專利再次獲評優(yōu)秀獎(jiǎng)

鋁/銅互連工藝與雙鑲嵌法(AL/Cu Interconnect and Dual Damascenes)

什么是銅互連?為什么銅互連非要用雙大馬士革工藝?

半大馬士革集成中引入空氣間隙結(jié)構(gòu)面臨的挑戰(zhàn)

通過工藝建模進(jìn)行后段制程金屬方案分析

降低半導(dǎo)體金屬線電阻的沉積和刻蝕技術(shù)

金屬層1工藝的制造流程

半大馬士革工藝:利用空氣隙減少寄生電容

大馬士革銅互連工藝詳解

銅互連雙大馬士革工藝的步驟

銅互連雙大馬士革工藝的步驟

評論