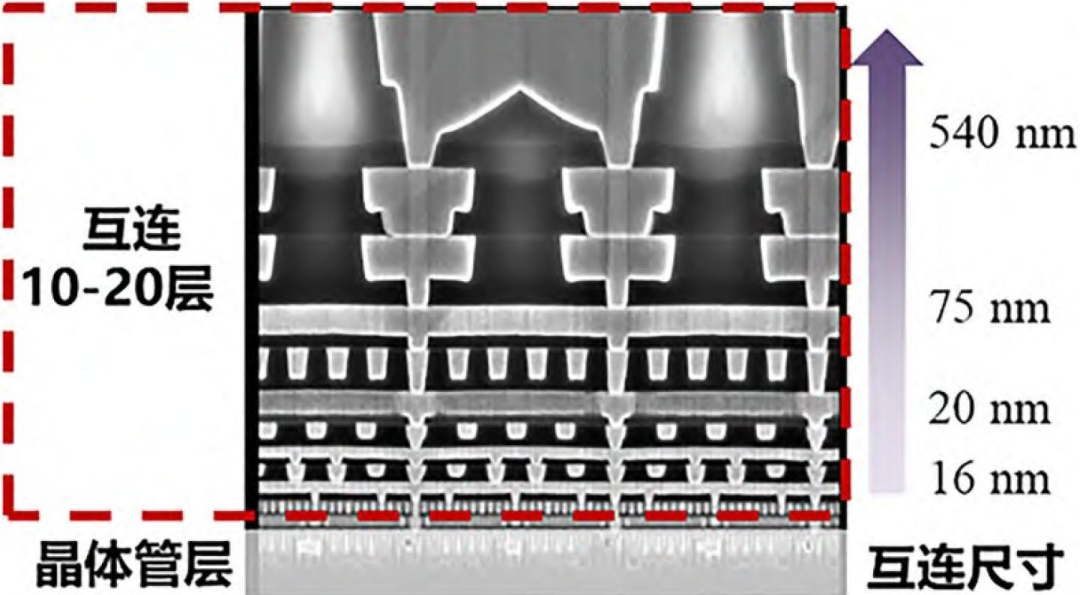

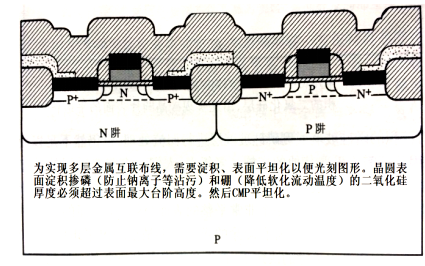

芯片制造可分為前段(FEOL)晶體管制造和后段(BEOL)金屬互連制造。后段工藝是制備導線將前段制造出的各個元器件串連起來連接各晶體管,并分配時鐘和其他信號,也為各種電子系統組件提供電源和接地。

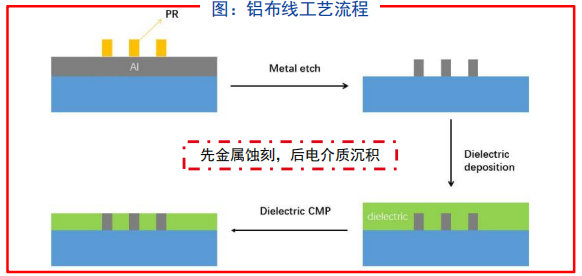

第一代互連技術通常采用鋁和鋁合金作為導體材料。鋁通常采用干法刻蝕中的反應離子刻蝕工藝進行布線。至0.18微米技術節點以下時,鋁作為金屬材料的缺點逐漸顯示出來。銅因具有良好的導電性、較高的熔點以及較好的抗電遷移性能,成為鋁之后金屬互連材料首選。

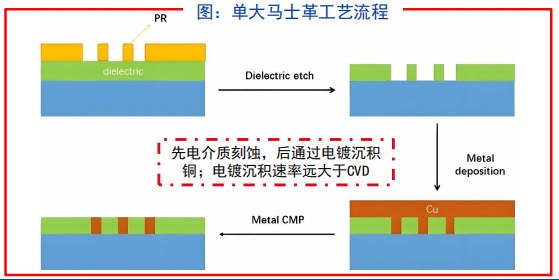

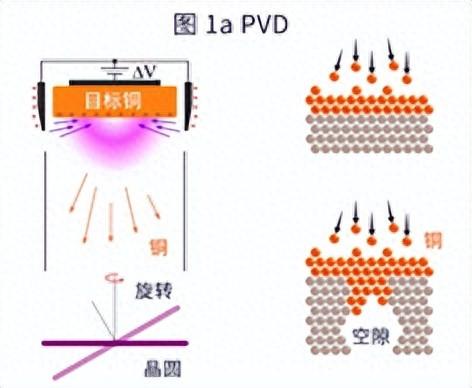

銅屬于穩定金屬,反應時不易產生揮發性物質,因此干法刻蝕不再適用于銅布線。1997年IBM公司提出大馬士革工藝,通過沉積銅實現布線,互連技術進入銅互連時代。

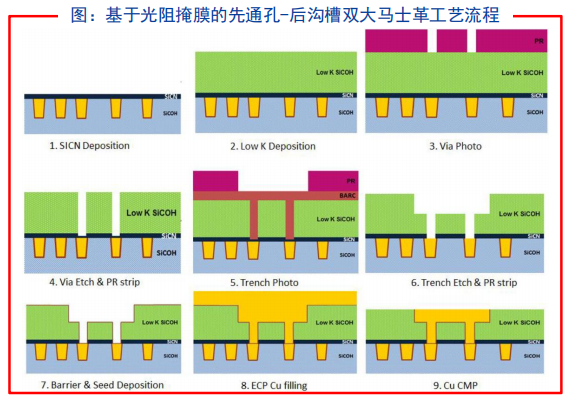

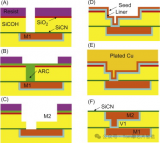

大馬士革工藝可分為單大馬士革工藝和雙大馬士革工藝,兩者的區別在于互連引線溝槽與互連通孔是否同時淀積填充銅金屬。單大馬士革工藝通過一次刻蝕和填充工藝來形成,即僅包含溝槽或僅包含通孔,具有更高的分辨率。通常第一金屬銅層(M1)用單大馬士革工藝,其他層用雙大馬士革工藝。雙大馬士革工藝可一次形成通孔和溝槽,較單大馬士革工藝可減少約20%的工藝流程,可分為先通孔-后溝槽和先溝槽-后通孔兩類。

先通孔-后溝槽:65nm及以上技術節點多采用基于光阻掩膜的先通孔工藝,原因是先形成溝槽會導致表面不平整,而通孔關鍵尺寸小于溝槽,為了在不平整的溝槽上光刻形成達到要求的通孔,對光刻膠的要求較高,要求光刻膠較厚且景深較大。

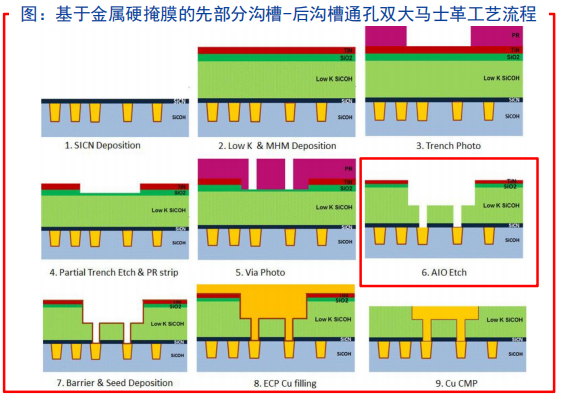

先溝槽-后通孔:金屬硬掩模一體化刻蝕(Metal Mard Mask All-in-One Etch)因更好的CD控制和更少的介質損傷,成為45nm及以下技術節點后段金屬溝槽/通孔刻蝕的主流,采用的是先溝槽的雙大馬士革工藝。

來源:半導體材料與工藝

-

元器件

+關注

關注

113文章

4807瀏覽量

94296 -

工藝

+關注

關注

4文章

667瀏覽量

29244 -

晶體管

+關注

關注

77文章

9977瀏覽量

140621 -

芯片制造

+關注

關注

10文章

673瀏覽量

29505 -

互連技術

+關注

關注

0文章

25瀏覽量

10499

原文標題:大馬士革銅互連工藝

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文詳解銅大馬士革工藝

如何采用銅互連單大馬士革工藝制作超厚金屬銅集成電感的概述

12吋晶圓集成電路芯片制程工藝與工序后端BEOL的詳細資料說明

實現3nm技術節點需要突破哪些半導體關鍵技術

華進半導體專利再次獲評優秀獎

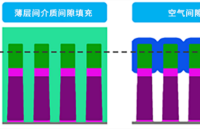

半大馬士革集成中引入空氣間隙結構面臨的挑戰

通過工藝建模進行后段制程金屬方案分析

降低半導體金屬線電阻的沉積和刻蝕技術

半大馬士革工藝:利用空氣隙減少寄生電容

大馬士革銅互連工藝詳解

大馬士革銅互連工藝詳解

評論