虛擬半導體工藝建模是研究金屬線設計選擇更為經濟、快捷的方法

作者:泛林集團 Semiverse Solutions 部門半導體工藝與整合部高級經理 Daebin Yim

l 由于阻擋層相對尺寸及電阻率增加問題,半導體行業正在尋找替代銅的金屬線材料。

l 在較小尺寸中,釕的性能優于銅和鈷,因此是較有潛力的替代材料。

隨著互連尺寸縮減,阻擋層占總體線體積的比例逐漸增大。因此,半導體行業一直在努力尋找可取代傳統銅雙大馬士革方案的替代金屬線材料。

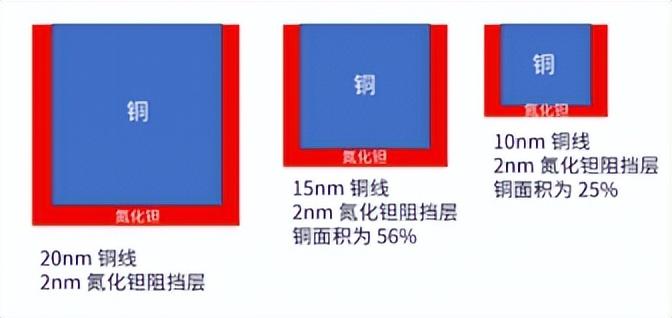

相比金屬線寬度,阻擋層尺寸較難縮減(如圖1)。氮化鉭等常見的阻擋層材料電阻率較高,且側壁電子散射較多。因此,相關阻擋層尺寸的增加會導致更為顯著的電阻電容延遲,并可能影響電路性能、并增加功耗。

圖1:銅微縮與阻擋層線結構圖

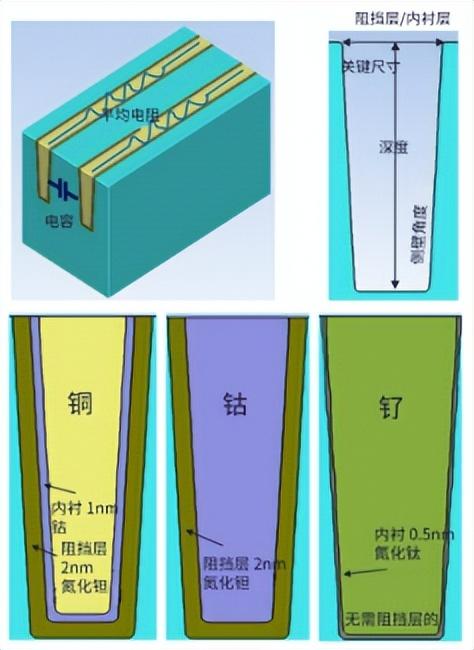

工程師們已經注意到釕和鈷等新的替代金屬線,并對其進行了測試,這些材料可以緩解線寬較窄和面積較小時的電阻率升高問題。工藝建模可用于比照分析不同溝槽深度和側壁角度下,釕、鈷和銅等其他金屬在不同關鍵尺寸的大馬士革工藝中的性能(圖2)。

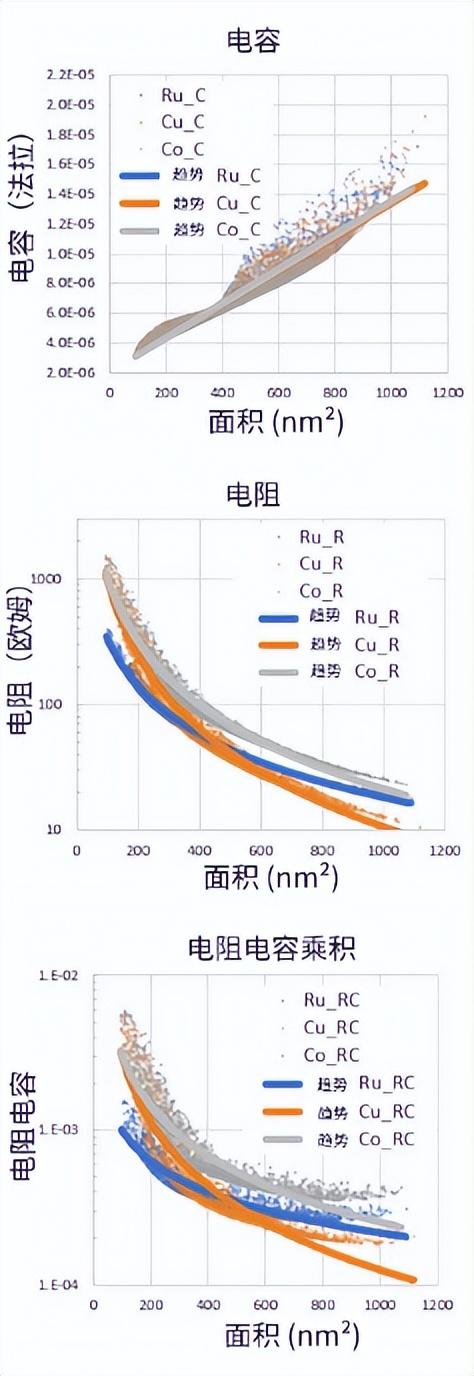

通過建模,可以提取總導體橫截面區域的平均線電阻、線間電容和電阻電容乘積值;隨后,可比較銅、釕、鈷金屬方案的趨勢。

圖2:(上)用于提取電阻和電容的兩條金屬線 3D 結構圖;(下)不同金屬和阻擋層材料的三種情況圖

為系統性地探究使用不同金屬的設計和材料影響,我們通過對三個變量(關鍵尺寸、深度和側壁角度)使用蒙特卡羅均勻分布,進行了包含 1000 次虛擬運行的實驗設計。

圖3:電阻電容實驗設計結果(點:實驗設計數據;線:趨勢曲線)從上至下:電容與面積、電阻與面積、電阻電容乘積與面積

圖 3 突出顯示了每種金屬的電阻與電阻電容乘積的交叉點,并表明在較小尺寸上,無需阻擋層的釕方案優于其他兩種金屬材料。這一情況分別在線關鍵尺寸值約為 20nm 和面積值約為 400nm2 時出現。這也表明,無需阻擋層的釕線電阻在線關鍵尺寸小于約 20nm 時最低; 當線關鍵尺寸值小于 20nm 時,2nm 氮化鉭阻擋層的電阻率占據了銅和鈷線電阻的主要部分,造成電阻急劇增加。當線關鍵尺寸縮減時,也在側壁和晶界出現額外散射,并導致電阻升高。溝槽刻蝕深度和側壁角度與電阻之間呈線性關系;電阻與線橫截面面積成反比例關系。

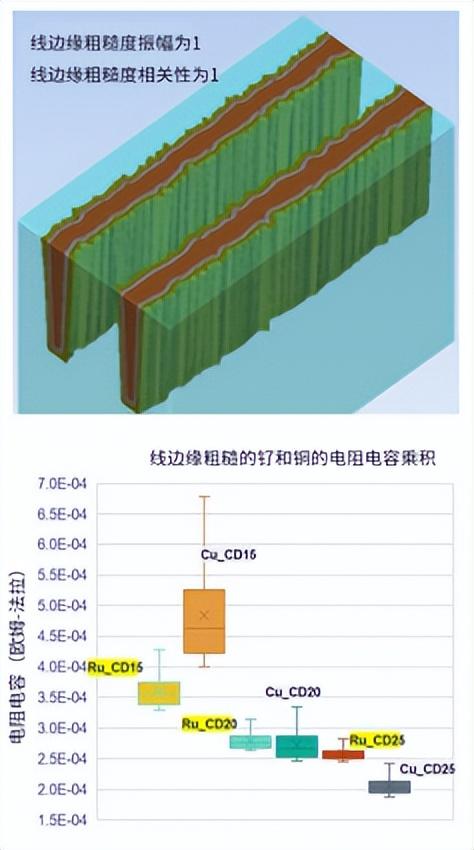

我們也分析了線邊緣粗糙度對電阻的影響。

圖4:(上)當線邊緣粗糙度振幅為 1 且相關性為 1 時,關鍵尺寸為 20nm 的銅線模型圖;(下)釕和銅線(關鍵尺寸分別為 15nm、20nm、25nm)實驗設計結果的箱形圖

在圖 4(下)中,由于無需阻擋層的結構,線關鍵尺寸為 15nm 時,釕線電阻電容值對線邊緣粗糙度振幅的敏感性遠低于銅,而銅由于高阻力的氮化鉭阻擋層非常易受電阻電容乘積變化的影響。

結論

傳統的微縮工藝要求阻擋層/內襯厚度低至極小的 2-3nm,極大壓縮了現代先進邏輯節點上銅線的空間。無需阻擋層的釕等新金屬在滿足電磁可靠性需求的同時,已躋身為有希望替代銅的材料。

該研究表明,釕的電阻電容延遲顯著低于其他材料,因此可能是先進節點上優秀的金屬候選材料。通常,許多晶圓實驗都需要完成這類金屬方案路徑探索。虛擬半導體工藝建模是研究金屬線設計選擇更為經濟、快捷的方法。

參考資料:

1. Liang Gong Wen et al., "Ruthenium metallization for advanced interconnects," 2016 IEEE International Interconnect Technology Conference / Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 2016, pp. 34-36, doi: 10.1109/IITC-AMC.2016.7507651.

2. M. H. van der Veen et al., "Damascene Benchmark of Ru, Co and Cu in Scaled Dimensions," 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 2018, pp. 172-174, doi: 10.1109/IITC.2018.8430407

審核編輯 黃宇

-

半導體

+關注

關注

335文章

28563瀏覽量

232303

發布評論請先 登錄

后段刻蝕工藝(BEOL ETCH)詳解

大馬士革銅互連工藝詳解

通過工藝建模進行后段制程金屬方案分析

通過工藝建模進行后段制程金屬方案分析

評論