本文介紹了半大馬士革工藝:利用空氣隙減少寄生電容。

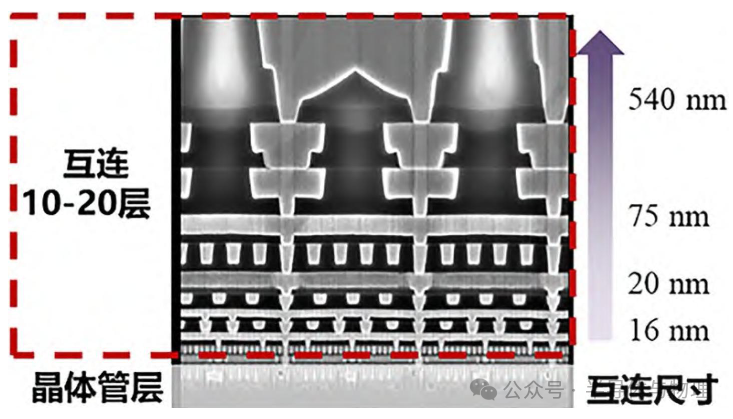

隨著半導體技術的不斷發展,芯片制程已經進入了3納米節點及更先進階段。在這個過程中,中道(MEOL)金屬互聯面臨著諸多新的挑戰,如寄生電容等問題。為了應對這些挑戰,人們提出了大馬士革(semi-damascene)工藝,特別是在使用釕(Ru)作為互連材料時,這種工藝顯示出了顯著的優勢,尤其是通過引入空氣隙來減少寄生電容。

傳統銅互連的問題

在傳統的銅互連工藝中,隨著制程節點的不斷縮小,寄生電容和電阻問題變得日益嚴重,導致信號延遲增加,性能下降。為了解決這些問題,研究人員開始尋找替代材料和技術。

釕(Ru)作為互連材料

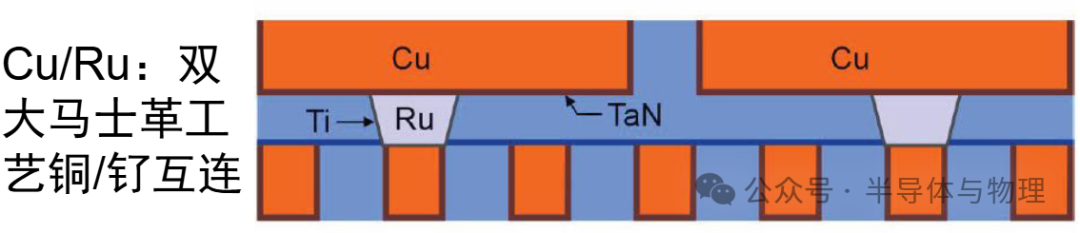

釕(Ru)作為一種低電阻、高可靠性的金屬,成為了下一代互連材料的有力候選。釕具有以下優點: 低電阻:釕的電阻率遠低于鈷(Co),接近于銅(Cu),即使在極小尺寸下,其電阻增長速度也較慢。 高可靠性:釕具有出色的抗電遷移能力和高可靠性,特別適合未來的5納米及更先進節點。 惰性和硬度:釕具有很高的惰性和硬度,不易通過化學機械拋光(CMP)去除,這使得傳統的雙大馬士革工藝在CMP過程中容易對低k介質造成損傷,導致成品率下降。

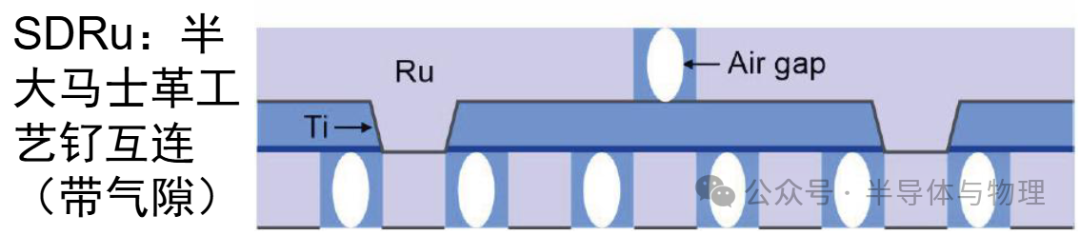

空隙的重要性

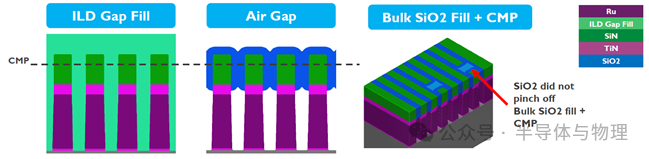

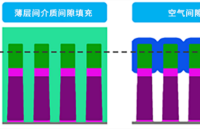

空隙(airgap)在半大馬士革工藝中起到了關鍵作用,它可以顯著降低金屬線間的寄生電容,從而減少RC延時。具體來說,空氣隙的引入可以: 減少電容:空氣隙的介電常數接近于1,遠低于傳統介質材料(如二氧化硅,介電常數約為3.9),因此可以顯著降低寄生電容。 提高性能:通過減少寄生電容,可以提高信號傳輸速度,減少信號延遲,從而提升整體性能。 降低功耗:減少寄生電容還可以降低信號傳輸過程中的能量損失,從而降低功耗。

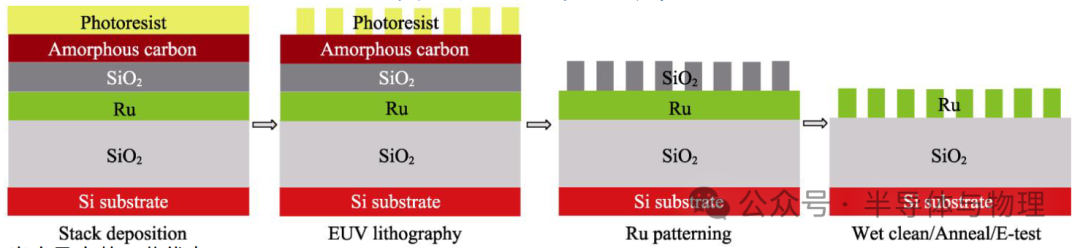

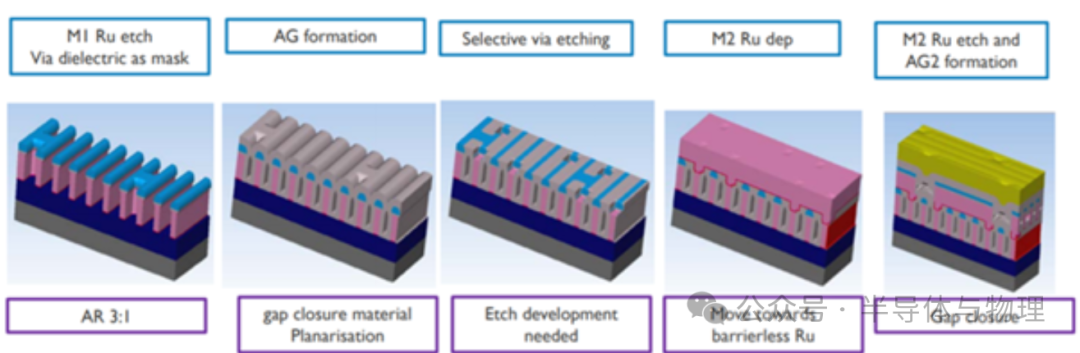

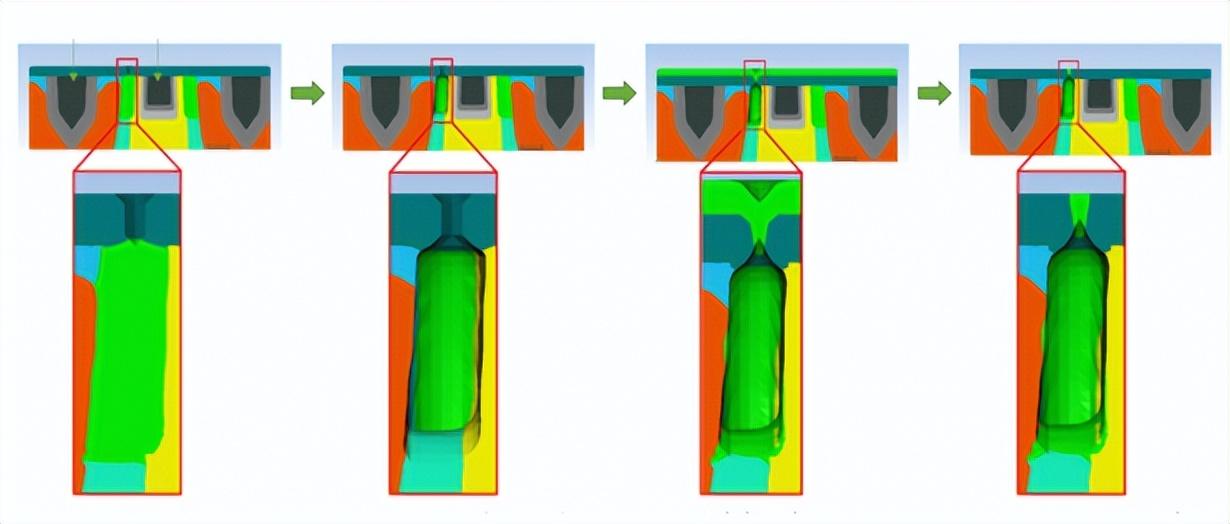

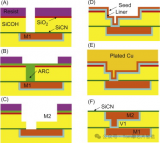

半大馬士革工藝流程

M1 Ru刻蝕:使用介質作為掩模,刻蝕出M1層的釕金屬線圖案。 空氣隙形成:使用ALD沉積一層絕緣層,在M1層的釕金屬線之間形成空氣隙,以減少寄生電容。 選擇性通孔刻蝕:刻蝕出通孔,以便連接上下層金屬線。 M2 Ru沉積:在通孔和M2層的圖案上沉積釕金屬。 M2 Ru刻蝕和空氣隙形成:刻蝕出M2層的釕金屬線圖案,并在M2層的釕金屬線之間形成空氣隙。

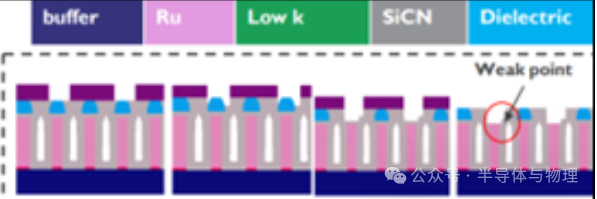

空隙的挑戰與解決方案

盡管空氣隙在減少寄生電容方面具有顯著優勢,但在實際應用中仍面臨一些挑戰,例如空氣隙閉合的控制、平面化的要求等。研究人員通過仿真和實驗,逐步解決了這些挑戰,確保了工藝的穩定性和可靠性。

空氣隙閉合控制:在M1層的釕金屬線之間形成空氣隙后,需要精確控制空氣隙的閉合,以確保空氣隙不會在后續工藝步驟中意外打開。這需要高精度的刻蝕和沉積工藝。 平面化:空氣隙形成后,需要進行平面化處理,以確保介質層的表面平整,不影響后續工藝步驟。這通常通過化學機械拋光(CMP)實現。 材料選擇:選擇合適的空氣隙閉合材料(如SiCN)和刻蝕工藝,以確保空氣隙的穩定性和可靠性。

-

電容

+關注

關注

100文章

6227瀏覽量

153195 -

寄生電容

+關注

關注

1文章

297瀏覽量

19652

原文標題:半大馬士革工藝:利用空氣隙減少寄生電容

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB寄生電容的影響 PCB寄生電容計算 PCB寄生電容怎么消除

CAN通信節點多時,如何減少寄生電容和保障節點數量?

一文詳解銅大馬士革工藝

如何采用銅互連單大馬士革工藝制作超厚金屬銅集成電感的概述

實現3nm技術節點需要突破哪些半導體關鍵技術

什么是寄生電容_寄生電容的危害

引入空氣間隙以減少前道工序中的寄生電容

引入空氣間隙以減少前道工序中的寄生電容

什么是銅互連?為什么銅互連非要用雙大馬士革工藝?

半大馬士革集成中引入空氣間隙結構面臨的挑戰

半大馬士革工藝:利用空氣隙減少寄生電容

半大馬士革工藝:利用空氣隙減少寄生電容

評論