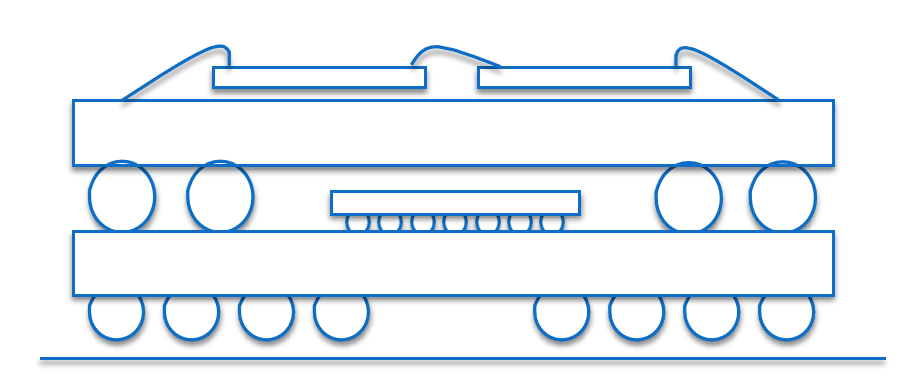

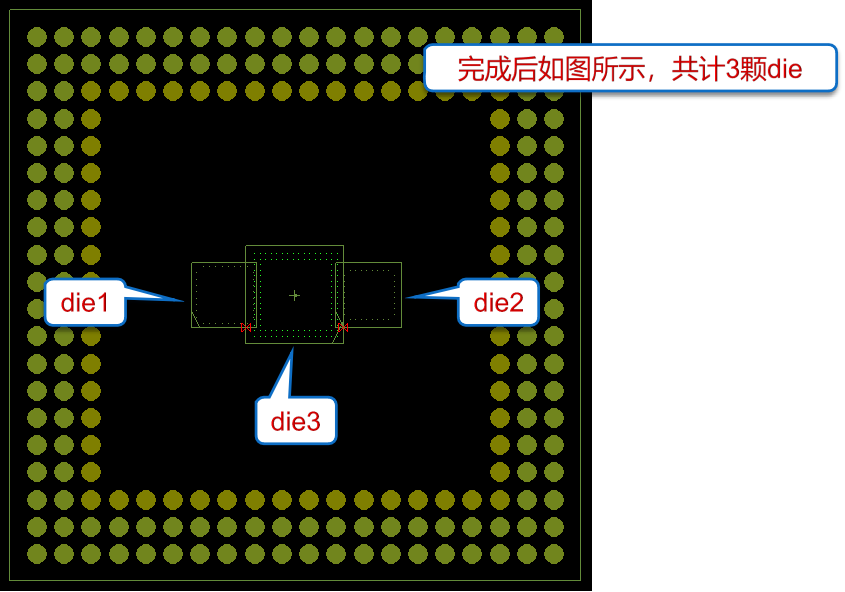

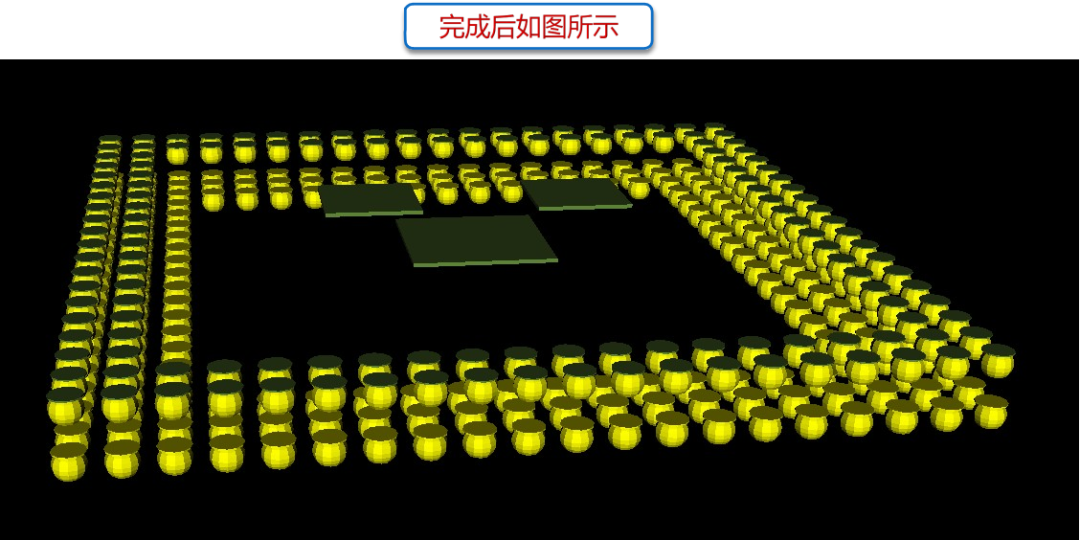

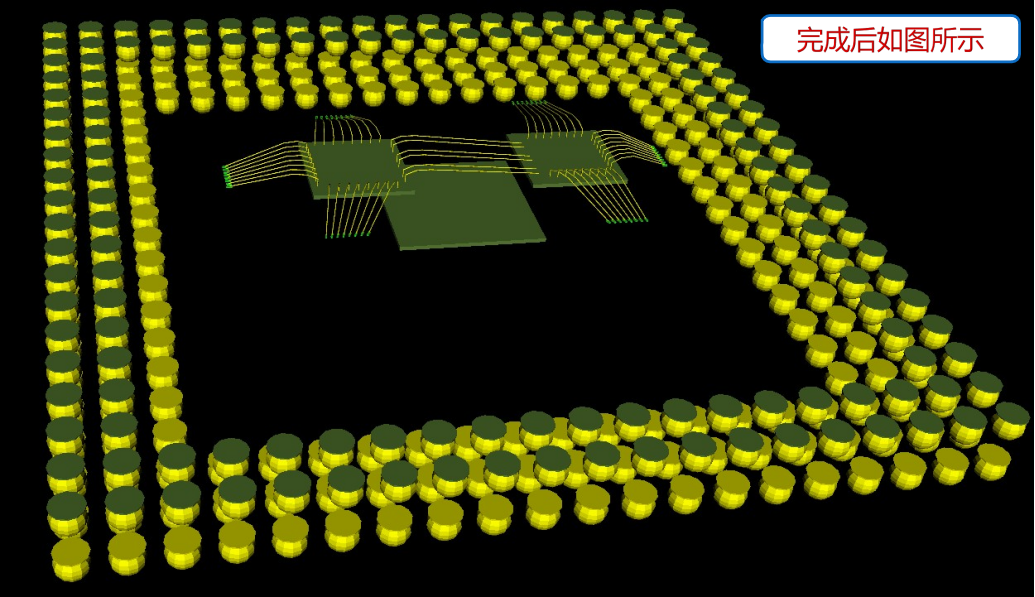

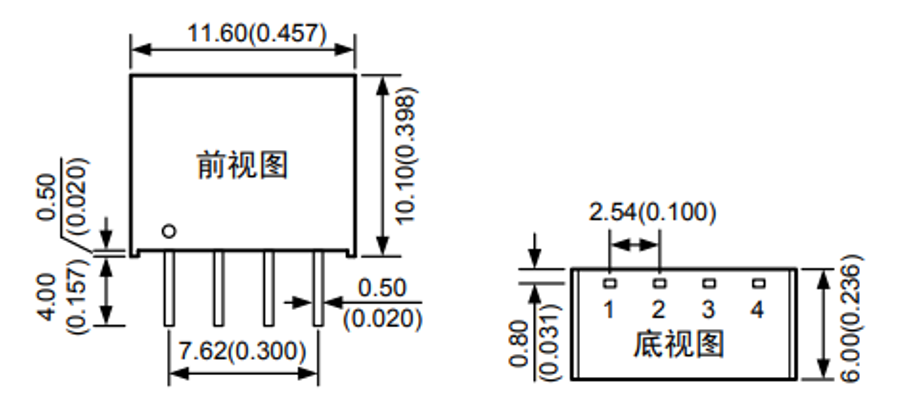

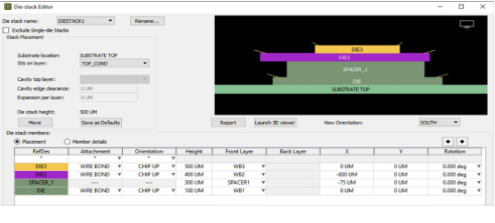

PoP封裝結(jié)構(gòu)

將要?jiǎng)?chuàng)建的元件參數(shù)如下:

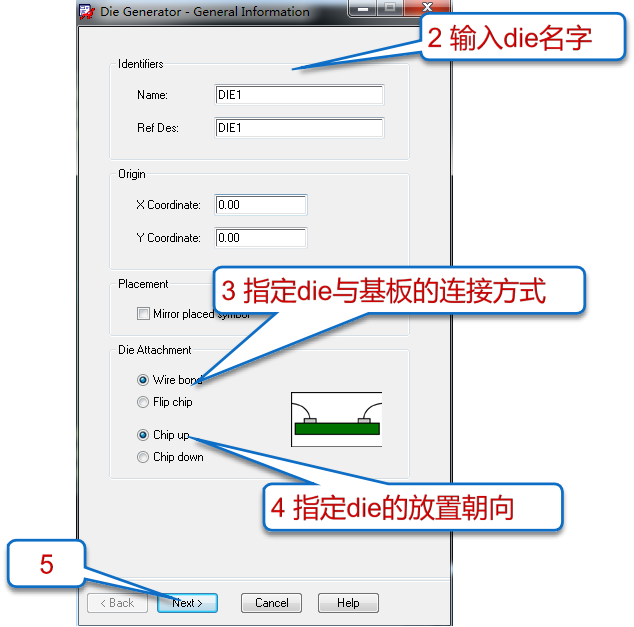

1、共有3顆die,上面封裝基板正面放置2顆, Wireband連接形式;下面封裝基板正面放置1顆,F(xiàn)lipchip連接形式;

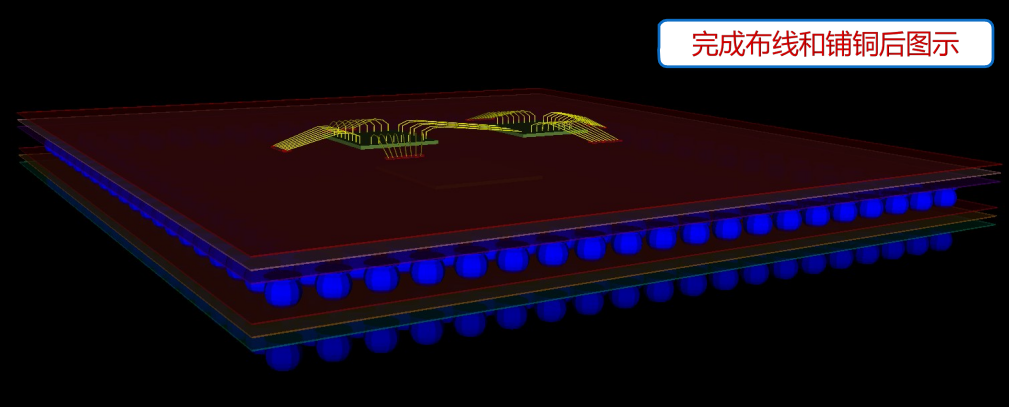

2、共有兩個(gè)封裝堆疊,各有1塊基板,均為BGA形式,層數(shù)均為4層;

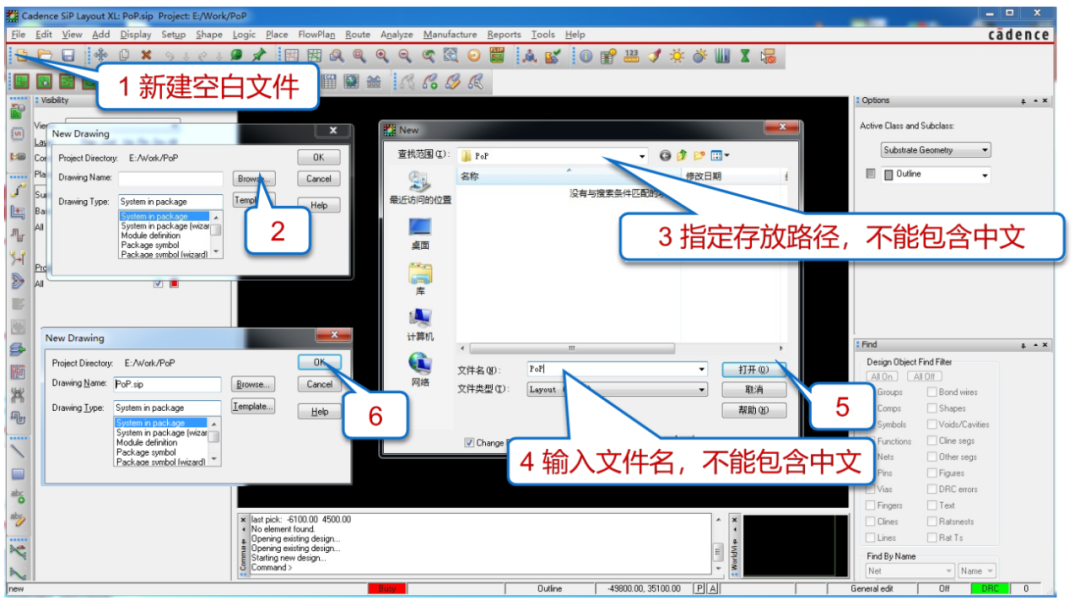

建立空白設(shè)計(jì)文件

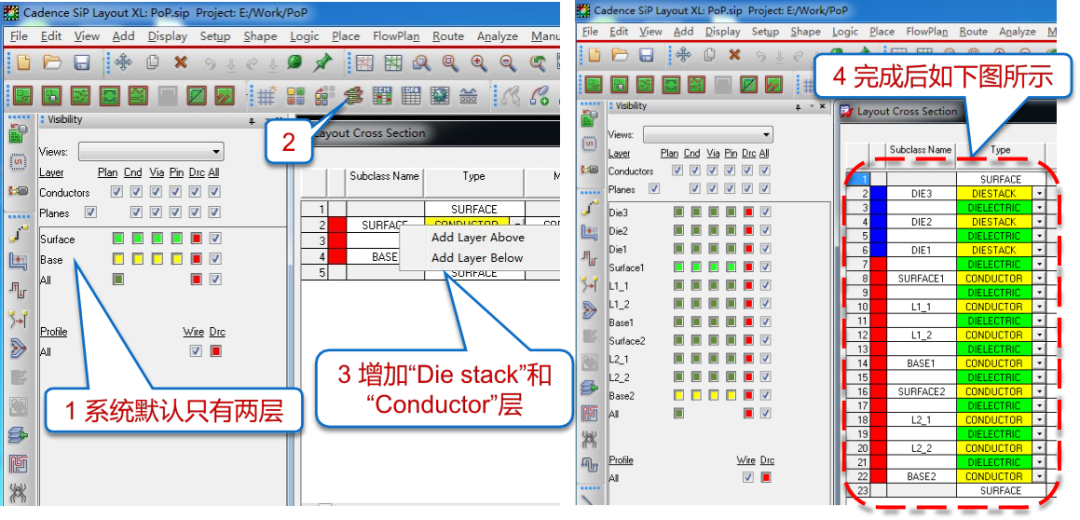

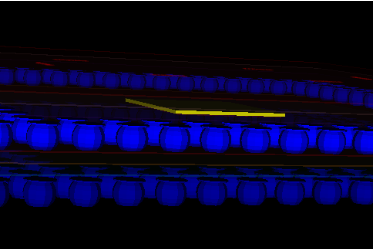

創(chuàng)建基板疊層結(jié)構(gòu)

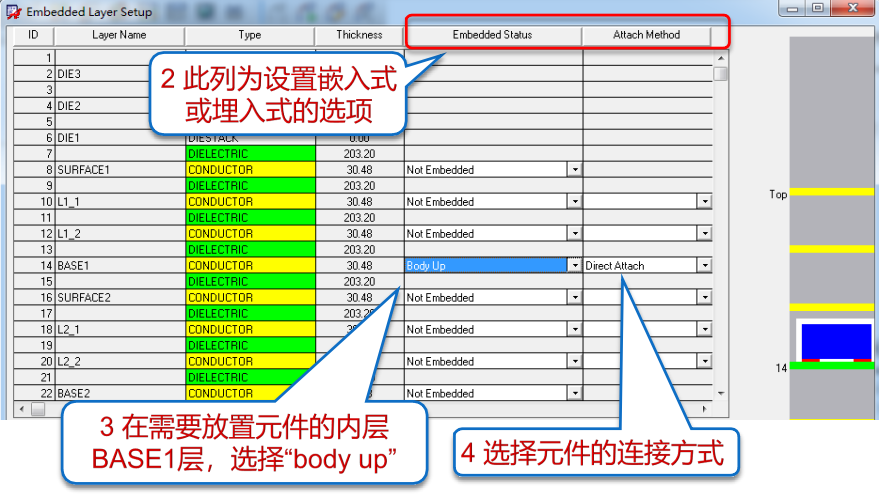

設(shè)置可放置埋入式元件的層

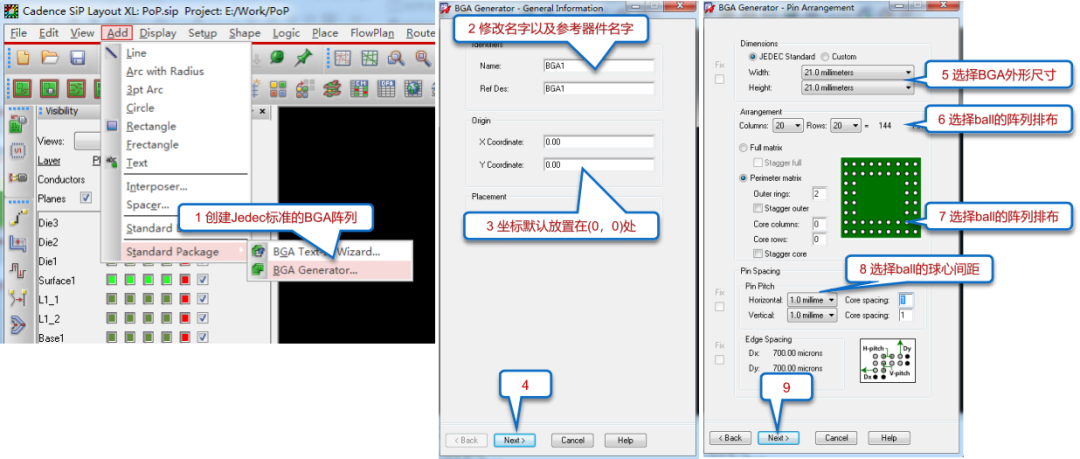

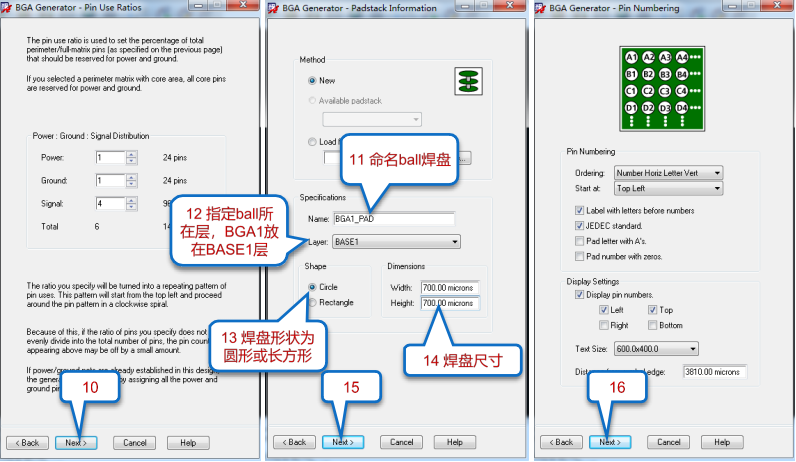

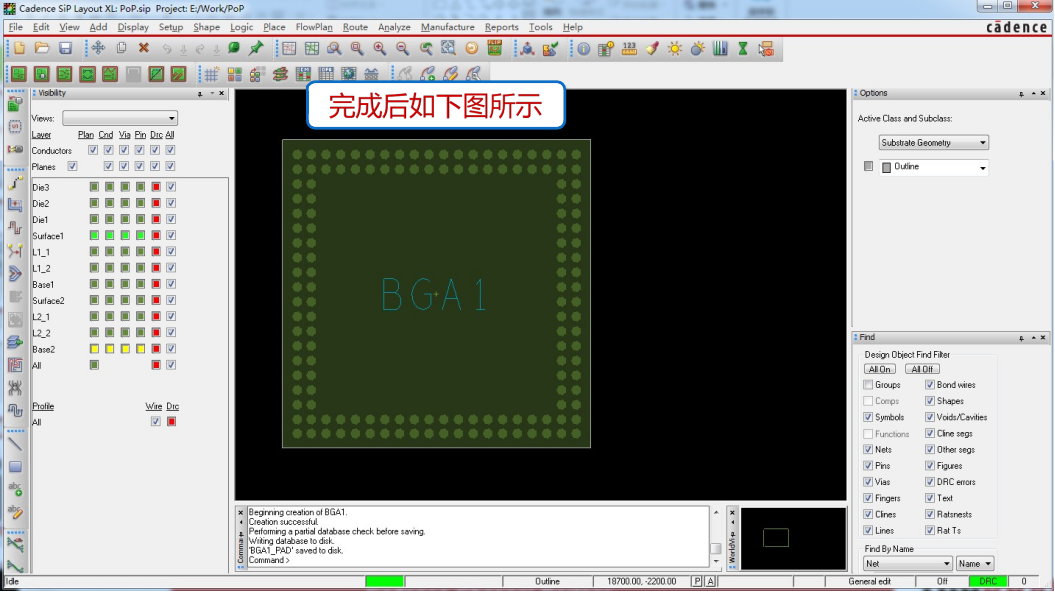

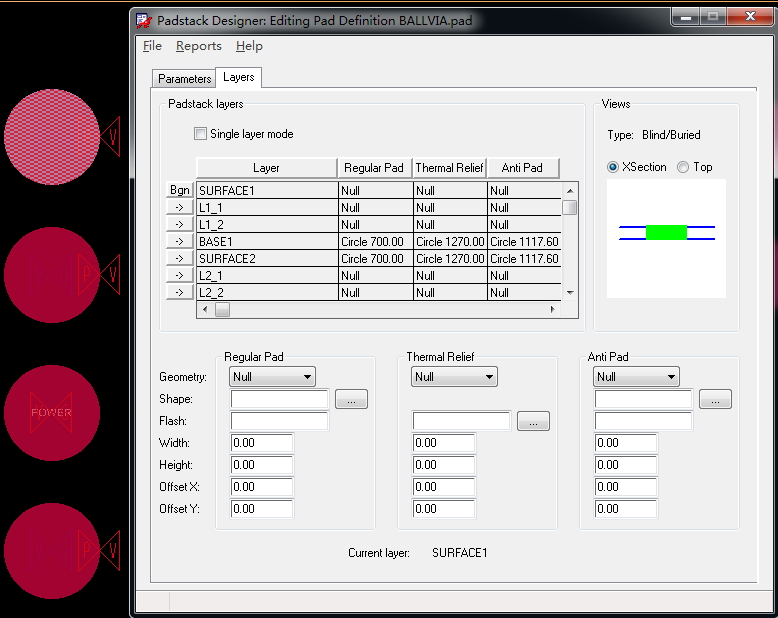

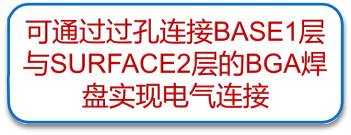

導(dǎo)入BGA

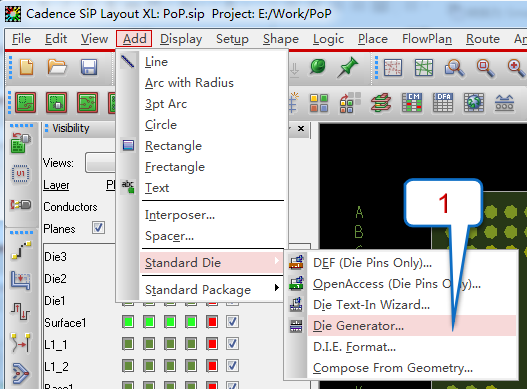

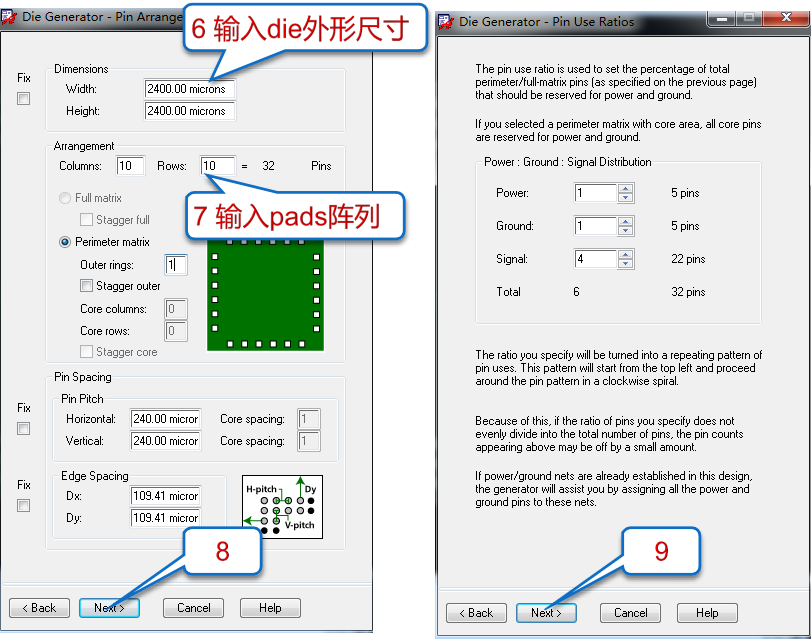

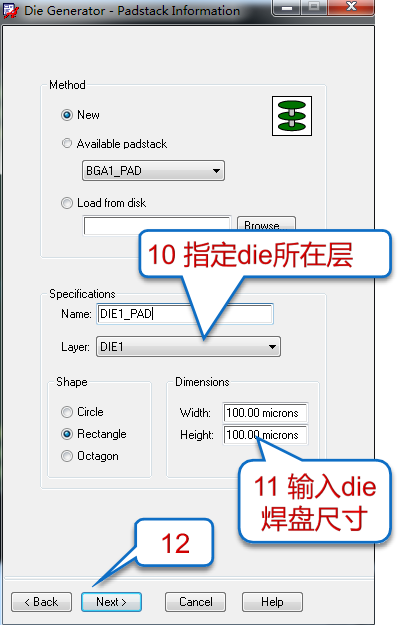

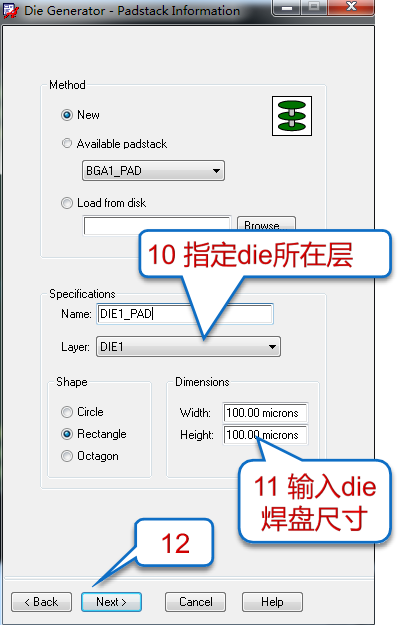

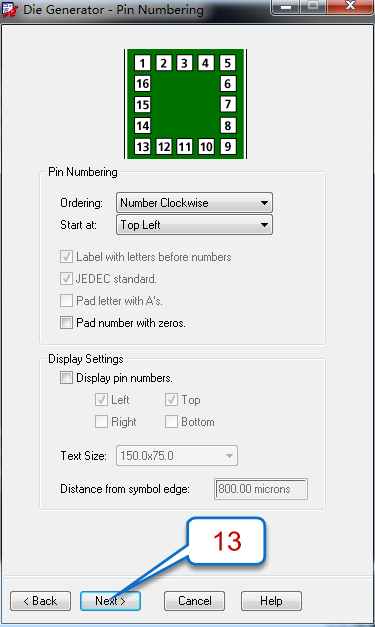

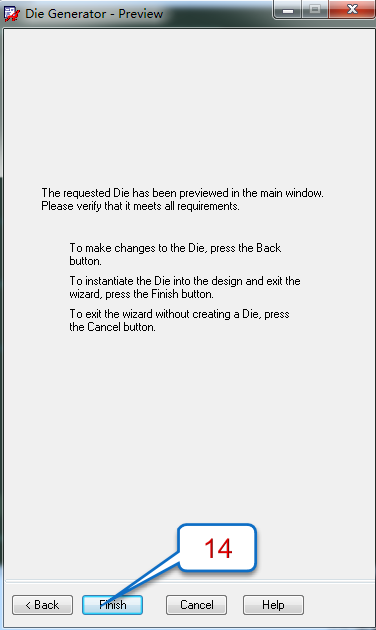

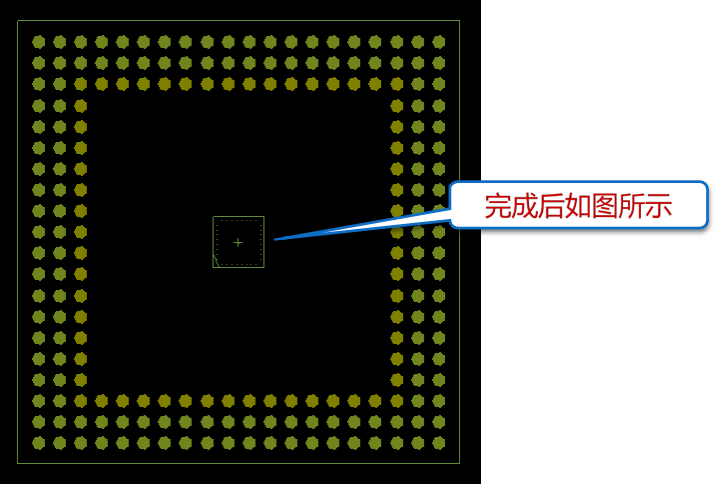

導(dǎo)入Die(DieGenerator方式)

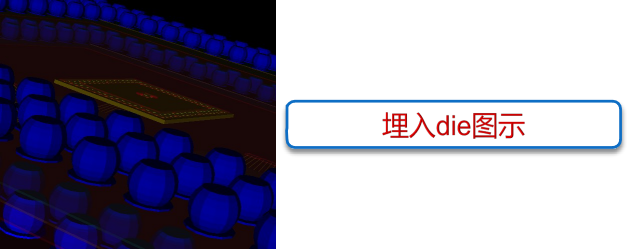

將Die調(diào)整為嵌入式

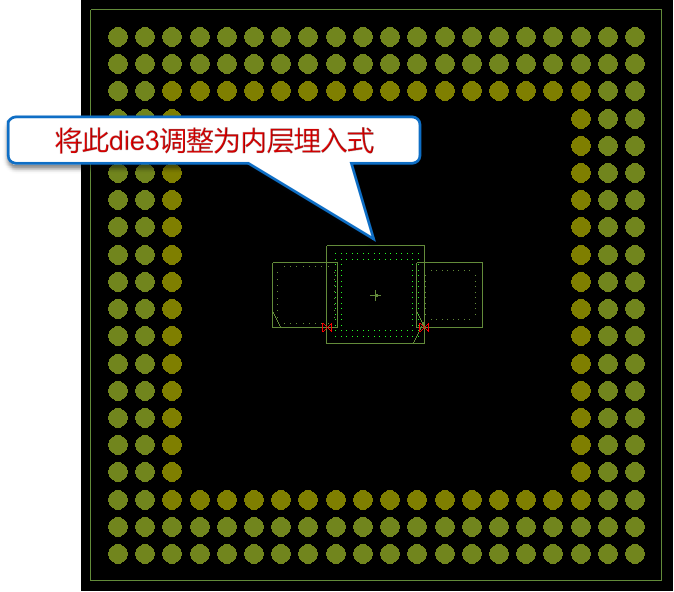

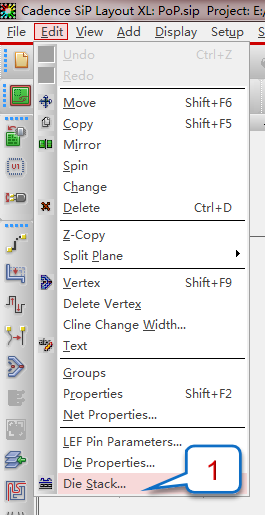

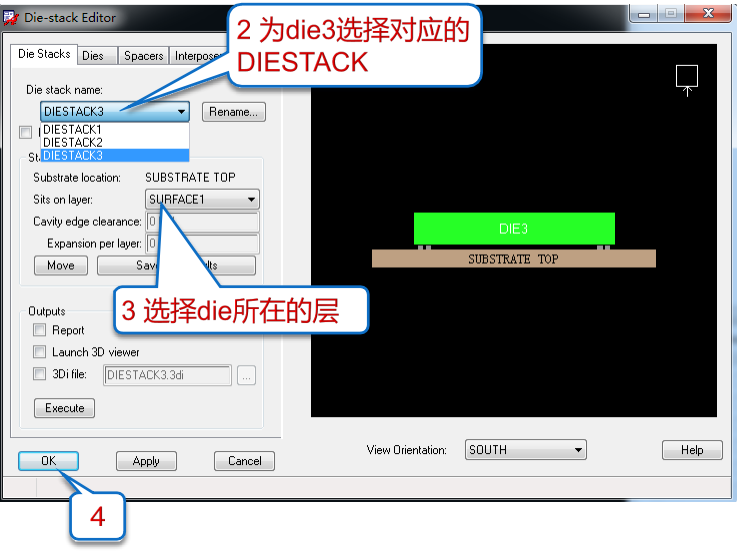

將Die3調(diào)整為內(nèi)層埋入式

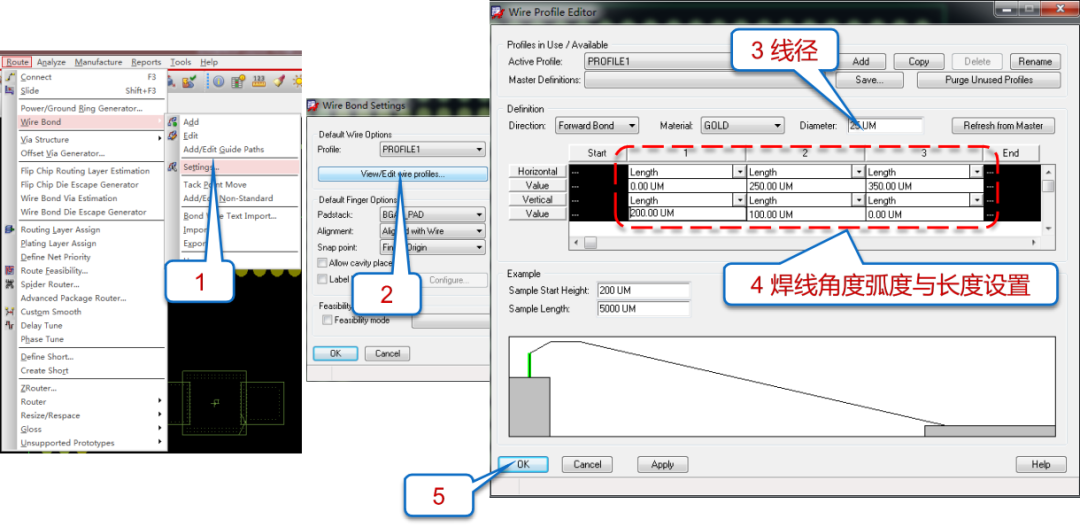

設(shè)置wirebond profile

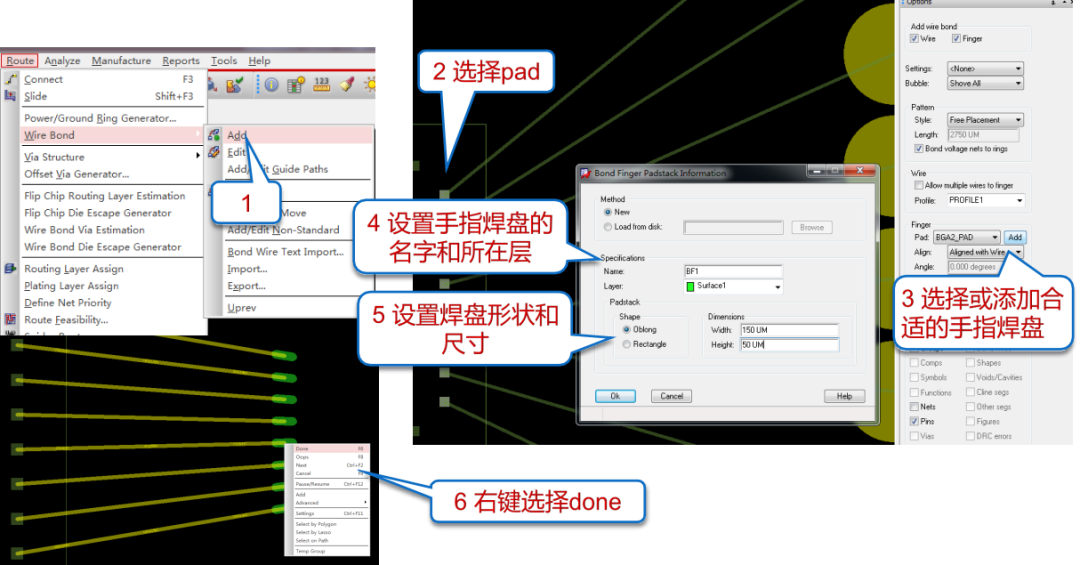

增加標(biāo)準(zhǔn)式焊線(Standard)

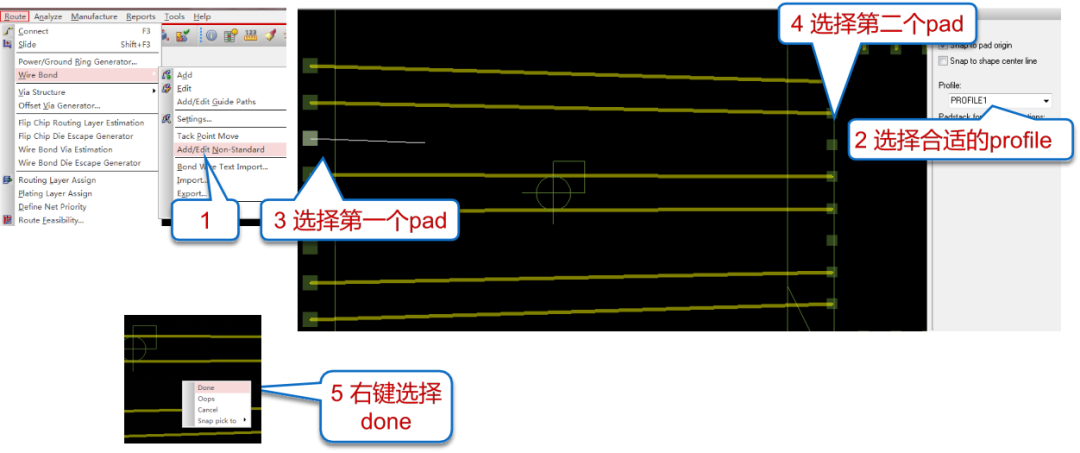

增加非標(biāo)準(zhǔn)式焊線(Non-Standard)--適合pad to pad或多根焊線連接

-

SiP

+關(guān)注

關(guān)注

5文章

523瀏覽量

106137 -

Layout

+關(guān)注

關(guān)注

15文章

412瀏覽量

62808 -

POP封裝

+關(guān)注

關(guān)注

0文章

6瀏覽量

5088

原文標(biāo)題:【技術(shù)指南】如何使用 SIP Layout 建立 PoP 封裝結(jié)構(gòu)

文章出處:【微信號(hào):封裝與高速技術(shù)前沿,微信公眾號(hào):封裝與高速技術(shù)前沿】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

一文看懂SiP封裝技術(shù)

第一次發(fā)帖。這種三維封裝堆疊用SIP Layout模塊要怎么畫呢?求個(gè)教程或者手冊(cè)什么的。

系統(tǒng)級(jí)封裝(SiP)的發(fā)展前景(上)

嵌入式存儲(chǔ)封裝技術(shù)SiP/SOC/MCP/PoP的區(qū)別是什么

SIP(封裝系統(tǒng)),SIP(封裝系統(tǒng))是什么意思

SIP封裝和采用SiP工藝的DFN封裝是什么

陶瓷封裝SiP腔體結(jié)構(gòu)介紹

傳統(tǒng)SIP封裝中的SIP是什么?

SiP主流的封裝結(jié)構(gòu)形式

淺談SiP系列之常用軟件工具

單列直插式封裝(SIP)原理

如何使用SIP Layout建立PiP封裝結(jié)構(gòu)

利用SIP Layout工具構(gòu)建PoP封裝結(jié)構(gòu)的方法

利用SIP Layout工具構(gòu)建PoP封裝結(jié)構(gòu)的方法

評(píng)論