AMD的Instinct MI300X以及英偉達的B200 GPU是否屬于巨型產品?據報道,臺積電在最近的北美技術研討會上透露其正在研發新的CoWoS封裝技術,進一步擴大SiP的體積和功耗。知情人士稱,新封裝將采用超大規模的120x120毫米設計,功耗預計高達數千瓦。

新版CoWoS技術使得臺積電能制造出面積超過光掩模(858平方毫米)約3.3倍的硅中介層。因此,邏輯電路、8個HBM3/HBM3E內存堆棧、I/O及其他小芯片最多可占據2831平方毫米的空間。而最大基板尺寸則為80×80毫米。值得注意的是,AMD的Instinct MI300X和英偉達的B200均采用了這項技術,雖然英偉達的B200芯片體積大于AMD的MI300X。

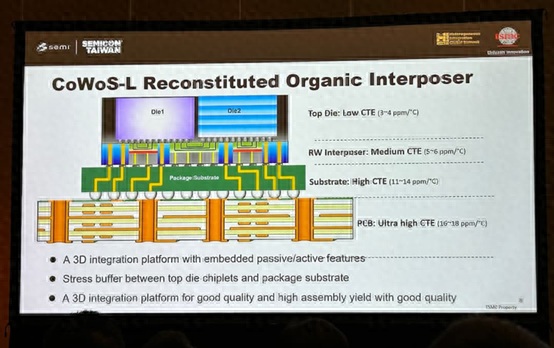

預計2026年推出的CoWoS_L將能實現中介層面積接近光罩尺寸的5.5倍(雖不及去年宣布的6倍,但仍屬驚人之舉)。這意味著4719平方毫米的空間可供邏輯電路、最多12個HBM內存堆棧及其他小芯片使用。然而,由于這類SiP所需基板較大,臺積電正考慮采用100x100毫米的設計。因此,這類芯片將無法兼容OAM模塊。

此外,臺積電表示,至2027年,他們將擁有一項新的CoWoS技術,該技術將使中介層面積達到光罩尺寸的8倍甚至更高,從而為Chiplet提供6864平方毫米的空間。臺積電設想的一種設計方案包括四個堆疊式集成系統芯片 (SoIC),搭配12個HBM4內存堆棧和額外的I/O芯片。如此龐大的設備無疑將消耗大量電力,且需配備先進的散熱技術。臺積電預計此類解決方案將采用120x120毫米的基板。

值得一提的是,今年早些時候,博通展示了一款定制AI芯片,包含兩個邏輯芯片和12個HBM內存堆棧。盡管我們尚未得知該產品的詳細規格,但從外觀上看,它似乎比AMD的Instinct MI300X和英偉達的B200更為龐大,盡管尚未達到臺積電2027年計劃的水平。

-

邏輯電路

+關注

關注

13文章

502瀏覽量

43187 -

臺積電

+關注

關注

44文章

5740瀏覽量

168988 -

CoWoS

+關注

關注

0文章

154瀏覽量

10968

發布評論請先 登錄

臺積電超大版CoWoS封裝技術:重塑高性能計算與AI芯片架構

臺積電先進封裝大擴產,CoWoS制程成擴充主力

臺積電CoWoS封裝A1技術介紹

臺積電計劃2027年推出超大版CoWoS封裝

臺積電CoWoS產能將提升4倍

臺積電封裝,新規劃

臺積電新版CoWoS封裝技術拓寬系統級封裝尺寸

臺積電新版CoWoS封裝技術拓寬系統級封裝尺寸

評論