《RVfpga:理解計算機體系結構》(以下簡稱“《RVfpga》”)是Imagination推出的完整RISC-V計算機體系結構課程,該課程針對本科教學設計,包含一整套豐富的教學資料和實踐練習,可幫助學生了解處理器架構中的關鍵要素,包括多個IP 內核,修改RISC-V 內核的方法,以及IP 內核的微架構。

2020年4月我們發布了《RVfpga》中文版1.0,2022年5月《RVfpga》中文版2.0 上線,此次是《RVfpga》3.0 版本。新的部分基于 VeeR EL2 核心,相比之前使用的 EH1 更為精簡。這使得原始的練習可以在成本較低的FPGA平臺上運行,如 Digilent 的 Basys3 和 Real Digital 的“Boolean Board”。許多大學的實驗室以及學生和愛好者已經擁有這些開發板,因此更多用戶可以通過《RVfpga》學習計算機體系結構。此外,《RVfpga》3.0 還添加了對 Imagination 擁有的 IDE - Catapult SDK 的支持,同時也支持 PlatformIO。

《RVfpga》3.0 更新細節:

☆添加對 VeeR EL2 的支持,該核比 VeeR EH1 更為精簡。基于 VeeR EH1 核和 VeeRwolf SoC 的課程材料也包含在此版本中。

☆增加對低成本開發板的支持,如 Real Digital 的 Boolean Board 和 Digilent 的 Basys 3 Board。☆添加對新的仿真工具的支持:RVfpga-ViDBo("Virtual Development Board虛擬開發開發板")和 RVfpga-Pipeline。☆為每個新增配置(Basys3 和 Boolean Boards,以及原始的 Nexys A7/Nexys 4 Boards,包括使用和不使用 DDR 存儲器的情況)添加入門指南和實驗室。☆添加對 Catapult SDK 的支持(僅限于 VeeR EL2)。☆創建了一個安裝了所有工具且已準備好使用的 Ubuntu 22.04 虛擬機(下載需要14GB 內存 )。

-

計算機

+關注

關注

19文章

7628瀏覽量

90173 -

imagination

+關注

關注

1文章

597瀏覽量

62005 -

RISC-V

+關注

關注

46文章

2482瀏覽量

48266

發布評論請先 登錄

睿創微納AI芯片技術登上國際計算機體系結構領域頂級會議

【「RISC-V體系結構編程與實踐」閱讀體驗】-- SBI及NEMU環境

寄存器間接尋址和寄存器尋址的區別

計算機主機內部結構

CPU時鐘周期與主頻的關系和區別

CPU時鐘周期的組成和作用

新手如何學單片機

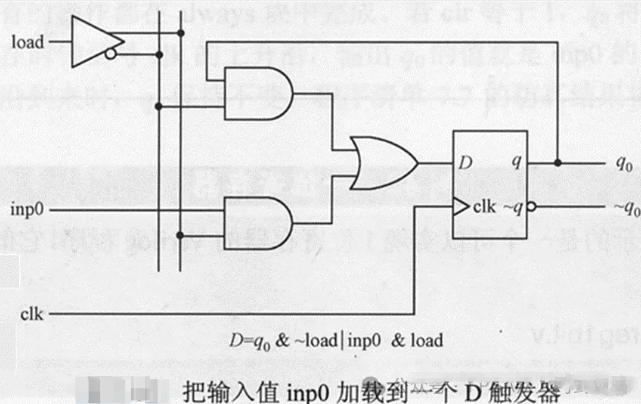

寄存器是什么意思?寄存器是如何構成的?

《RVfpga:理解計算機體系結構》3.0 版本更新上線

《RVfpga:理解計算機體系結構》3.0 版本更新上線

評論