這里只討論內核的軟件復位方式。像STM32的備份域復位里面也有軟件復位,則不在本文討論范圍。額外提一句,上電復位是完整復位芯片所有東西,包括內核、debug部分、外設、中間邏輯電路狀態(模塊外部的邏輯電路狀態,如果沒有復位,也會影響到下次運行),因此需要確保做完全復位時候,應該使用上電復位。

一、cortex-m3

圖1來自cortex m3編程手冊

該位只復位內核,不復位debug部分

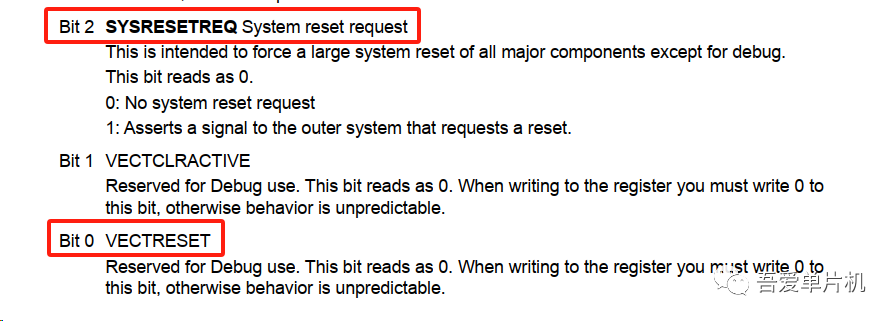

(2)SCB_AIRCR寄存器,SYSRESETREQ位

該位一般叫做系統復位,該位定義為會復位內核,不復位debug部分,至于是否復位其他部分,比如外設,則由具體的芯片來實現

圖1

二、cortex-m0

圖2來自cortex m0編程手冊

(1)SCB_AIRCR寄存器,VECTRESET位

cortex-m0沒有提供這個位,也即cortex-m0沒有提供單獨復位內核的定義

(2)SCB_AIRCR寄存器,SYSRESETREQ位

參考cortex-m3

圖2

三、其他參考

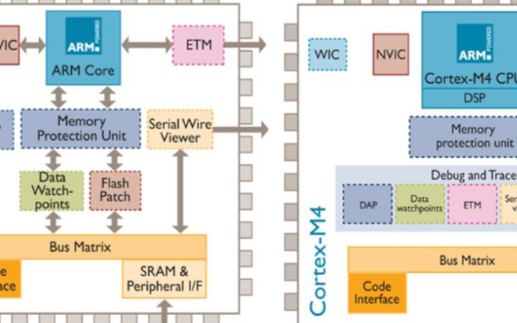

以下圖3 圖4來自 Cortex-M3-Definitive-Guide-EN.pdf

圖3

圖4

-

寄存器

+關注

關注

31文章

5421瀏覽量

123324 -

內核

+關注

關注

3文章

1410瀏覽量

41095 -

STM32

+關注

關注

2289文章

11012瀏覽量

362365 -

Cortex-M

+關注

關注

2文章

230瀏覽量

30224 -

軟件復位

+關注

關注

0文章

10瀏覽量

3023

發布評論請先 登錄

Cortex-M內核使用FreeRTOS特別注意事項

ARM Cortex-M內核的相關資料推薦

Cortex-M內核的MPU內存保護單元

軟復位操作《Cortex?-M0+等內核通用》

Cortex-M內核的軟件復位方式

Cortex-M內核的軟件復位方式

評論