PLL對于VCO有什么要求?如何設計VCO輸出功率分配器?

PLL對于VCO的要求:

1. 頻率穩定性:VCO的輸出頻率需要具有較高的穩定性和準確度。對于PLL系統來說,VCO的輸出頻率與參考信號頻率的比例決定了鎖定的頻率倍數,因此對于VCO的頻率穩定性要求比較高。

2. 延遲:VCO的輸出延遲對于PLL系統的工作非常重要。如果VCO的輸出延遲太大,則可能會導致鎖定時間變長或者無法鎖定。

3. 噪聲:VCO的輸出噪聲會影響PLL系統的性能和穩定性。因此,要求VCO的輸出噪聲較小。

4. 相位噪聲:VCO的相位噪聲對于PLL系統的性能也非常重要。較低的相位噪聲可以提高系統的鎖定范圍和穩定性。

5. 帶寬:VCO需要具有足夠的帶寬來支持PLL系統的頻率范圍。此外,VCO的帶寬還需要與整個PLL系統的帶寬匹配以保持良好的穩定性。

VCO輸出功率分配器的設計:

VCO輸出功率分配器將VCO的輸出信號分配到各個接收器或負載上,以滿足系統的需求。其主要設計思路是將VCO輸出的信號分配到各個接收器上時,能夠盡可能保持信號的幅度一致,相位匹配以及最小的回波損耗。

設計VCO輸出功率分配器需要考慮以下幾個方面:

1. 分配比例:VCO輸出信號需要按照系統的需求分配到各個接收器上。根據不同的系統要求,VCO輸出功率分配器可以采用不同的分配比例。在實際設計中,通常采用分配比例相等或基于頻率的方式進行分配。

2. 最小反射損耗:為了盡可能減小信號的反射損耗,VCO輸出功率分配器需要考慮匹配網絡和阻抗適配,以確保信號的幅度和相位在各個負載之間保持一致。

3. 穩定性:在設計過程中,需要保證功率分配器的穩定性。可以通過添加穩定電路來實現。

4. 相位匹配:為了保證VCO輸出信號的相位在各個接收器上保持一致,需要在設計過程中考慮相位匹配。可以采用相位器、延遲線等相位調節電路。

5. 功率分配網絡:功率分配器需要采用合適的功率分配網絡,以實現信號的分配和匹配。

在實際設計過程中,需要充分考慮VCO和功率分配器的各種要求和限制,并根據具體的系統需求選擇合適的設計方案來實現功率分配器的設計。

-

pll

+關注

關注

6文章

880瀏覽量

136030 -

VCO

+關注

關注

13文章

311瀏覽量

69970 -

功率分配器

+關注

關注

0文章

25瀏覽量

8819

發布評論請先 登錄

802-4-0.252,N型母頭功率分配器/合路器MECA

AD9518-4 6路輸出時鐘發生器,集成1.6GHz VCO技術手冊

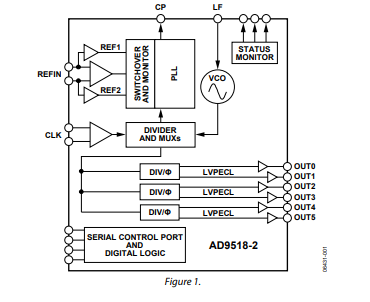

AD9518-2 6路輸出時鐘發生器,集成2.2GHz VCO技術手冊

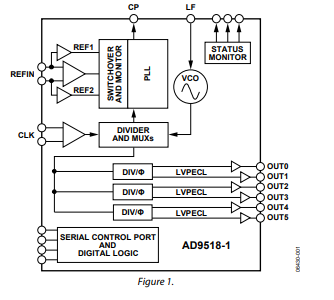

AD9518-1 6路輸出時鐘發生器,集成2.5GHz VCO技術手冊

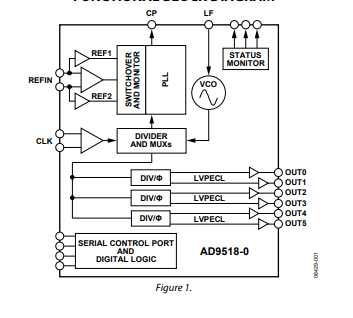

AD9518-0 6路輸出時鐘發生器,集成2.8GHz VCO技術手冊

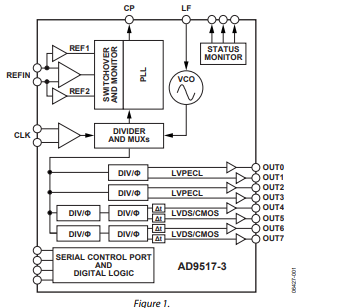

AD9517-3 12路輸出時鐘發生器,集成2.0GHz VCO技術手冊

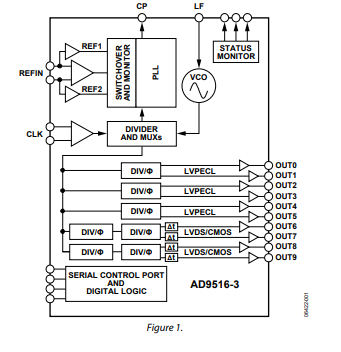

AD9516-3 14路輸出時鐘發生器,集成2.0GHz VCO技術手冊

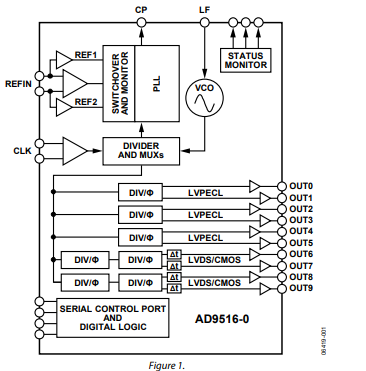

AD9516-0 14路輸出時鐘發生器,集成2.8 GHz VCO技術手冊

PLL對于VCO有什么要求?如何設計VCO輸出功率分配器?

PLL對于VCO有什么要求?如何設計VCO輸出功率分配器?

評論