點擊上方藍字關注我們

1 概述

1.1 FPGA的特點及其發展趨勢

嵌入式系統是一個面向應用、技術密集、資金密集、高度分散、不可壟斷的產業,隨著各個領域應用需求的多樣化,嵌入式設計技術和芯片技術也經歷著一次又一次的革新。雖然ASIC的成本很低,但設計周期長、投入費用高、風險較大,而可編程邏輯器件(Programmable Logical Device)設計靈活、功能強大,尤其是高密度現場可編程邏輯器件(Field Programmable Gate Array)其設計性能已完全能夠與ASIC媲美,而且由于FPGA的逐步普及,其性能價格比已足以與ASIC抗衡。因此,FPGA在嵌入式系統設計領域已占據著越來越重要的地位。

FPGA的基本結構由以下幾個部分構成:

·可編程邏輯功能模塊CLB(Configurable Logic Blocks)

·可編程輸入輸出模塊IOB(Input/Output Blocks)

·可編程內部互連資源PI(Programmable Interconnection)

隨著工藝的進步和應用系統需求,一般在FPGA中還包含以下可選資源:

·存儲器資源(Block RAM和Select RAM)

·數字時鐘管理單元(分頻/倍頻、數字延遲)

·I/O多電平標準兼容(Select I/O)

·算數運算單元(乘法器、加法器)

·特殊功能模塊(MAC等硬IP核)

以FPGA為核心的PLD產品是近幾年集成電路中發展得最快的產品。隨著FPGA性能的高速發展和設計人員自身能力的提高,FPGA將進一步擴大可編程芯片的領地,將復雜專用芯片擠向高端和超復雜應用。目前FPGA的發展趨勢主要體現在以下幾個方面:

·向更高密度、更大容量的千萬門系統級方向邁進

·向低成本、低電壓、微功耗、微封裝和綠色化發展

·IP資源復用理念將得到普遍認同并成為主要設計方式

·MCU、DSP、MPU等嵌入式處理器IP將成為FPGA應用的核心

隨著處理器以IP的形式嵌入到FPGA中,ASIC和FPGA之間的界限將越來越模糊,未來的某些電路版上可能只有這兩部分電路:模擬部分(包括電源)和一塊FPGA芯片,最多還有一些大容量的存儲器。Xilinx等公司最新一代FPGA:Spartan II/E、Virtex II Pro及其相關IP Core的推出,使我們有理由相信,可編程片上系統(System on Programmable Chip)的時代已經離我們不遠了。

1.2可編程片上系統(SOPC)的基本特征

可編程片上系統(SOPC)是一種特殊的嵌入式系統:首先它是片上系統(SOC),即由單個芯片完成整個系統的主要邏輯功能;其次,它是可編程系統,具有靈活的設計方式,可裁減、可擴充、可升級,并具備軟硬件在系統可編程的功能。

SOPC結合了SOC和FPGA各自的優點,一般具備以下基本特征:

·至少包含一個嵌入式處理器內核

·具有小容量片內高速RAM資源

·豐富的IP Core資源可供選擇

·足夠的片上可編程邏輯資源

·處理器調試接口和FPGA編程接口

·可能包含部分可編程模擬電路

·單芯片、低功耗、微封裝

SOPC設計技術實際上涵蓋了嵌入式系統設計技術的全部內容,除了以處理器和實時多任務操作系統(RTOS)為中心的軟件設計技術、以PCB和信號完整性分析為基礎的高速電路設計技術以外,SOPC還涉及目前以引起普遍關注的軟硬件協同設計技術。由于SOPC的主要邏輯設計是在可編程邏輯器件內部進行,而BGA封裝已被廣泛應用在微封裝領域中,傳統的調試設備,如:邏輯分析儀和數字示波器,已很難進行直接測試分析,因此,必將對以仿真技術為基礎的軟硬件協同設計技術提出更高的要求。同時,新的調試技術也已不斷涌現出來,如Xilinx公司的片內邏輯分析儀Chip Scope ILA就是一種價廉物美的片內實時調試工具。

2 IP資源復用理念與IP Core設計

2.1 IP資源復用理念

由于芯片設計的復雜性和產品面市時間對于保證終端市場的成功率至關重要,設計師不斷尋求縮短設計周期的方法,以及更有效的設計方式。隨著我們步入系統級芯片時代,利用IP內核和可編程邏輯進行設計復用顯得日趨重要。

IP資源復用(IP Reuse)是指在集成電路設計過程中,通過繼承、共享或購買所需的智力產權內核,然后再利用EDA工具進行設計、綜合和驗證,從而加速流片設計過程,降低開發風險。IP Reuse已逐漸成為現代集成電路設計的重要手段,在日新月異的各種應用需求面前,超大規模集成電路設計時代正步入一個IP整合的時代。

IP Reuse不僅僅應用于專用集成電路設計,對基于FPGA的嵌入式系統設計領域而言,更是具有舉足輕重的地位。FPGA在采用IP內核方面走在了市場的前面,其原因有以下幾個方面:

·FPGA具有極高的靈活性和面市時間短的特點,這使得多項設計迭代可以在數小時而不是數周內完成

·由于FPGA密度達到了百萬門甚至是千萬門,越來越多的設計師傾向于使用IP內核保持和提高產品的產量

·可編程邏輯價格低廉,可以作為切實可行的生產工具以及最佳原型設計,而且不許要昂貴的EDA設計工具,大大降低了設計門檻

2.2 IP Core設計方法:編碼風格與項目模板

IP Core是IP Reuse的載體和核心內容,基于應用需求、規范協議和行業標準的不同,IP Core的內容也是千差萬別的。但是,為了使IP Core易于訪問和易于集成,其設計必須遵循一定的規范和準則。

在IP Core的開發方面,許多開放性的團體都付出了巨大的努力來推動各種IP Core的開發和IP Reuse理念的推廣,其中比較著名的是Open Cores開發組織(http://www.opencores.org)。他們不僅開發了許多開放源代碼的IP Core,涵蓋了處理器IP、處理器外設控制器IP、算術運算單元IP、DSP算法IP等方面,而且編寫了詳細的IP Core編碼風格和項目模板,并倡導了一種總線標準wishbone,用于規范各種IP Core的接口標準。國內開放性團體IP Core開發小組(http://www.IPcore.com.cn)也在IP Core開發和IP Reuse理念的推廣和普及方面進行了不懈的努力。

編碼風格(Coding Style)是基于HDL的IP Core源碼編寫的指導性文檔,其可讀性直接關系到IP Core的易于訪問和易于集成性。編碼風格一般包含幾個方面的約定:文件頭和版本說明、聯機注釋、命名規則、可綜合編碼等。

項目模板則規定了完成一個IP Core設計包含的主要內容及所需提供的文檔,項目模板內容及其文檔直接關系到IP Core的易于集成特性,一個IP Core必須是完整的、經過全面驗證的,才能順利地集成到應用項目中去。項目模板一般包含幾個方面的內容:項目定義、接口說明、系統結構和模塊、設計文檔說明、測試驗證報告、約束和實現、版本說明、試用評價以及參考文獻等。

編碼風格和項目模板詳細文檔的英文版和中文版可分別從上述兩個網站獲得。

2.3 IP Core驗證:仿真、測試與評估板

IP Core設計在完成編碼階段以后,對其功能的測試驗證是一項非常重要的內容,因為這直接關系到IP Core資源的可用性。僅僅通過功能仿真、時序仿真和測試向量驗證的IP Core是不完備的,它必須通過實際系統的驗證。國際上各大公司通常采用的辦法是評估板驗證,也即構建一個與實際系統IP Core應用一致的硬件環境,通過下載FPGA配置使其具備相應的邏輯功能,并進行實物仿真。

另外,由于IP Core的許可成本較高,用戶也通常希望在購買IP Core之前,對其功能進行充分的驗證以確定是否適合于目標系統,從而降低投資風險,(當然,內核和源代碼的知識產權是加了保護措施的),Xilinx公司的Sing Once和Altera公司的Open Core均提供了這樣的平臺。

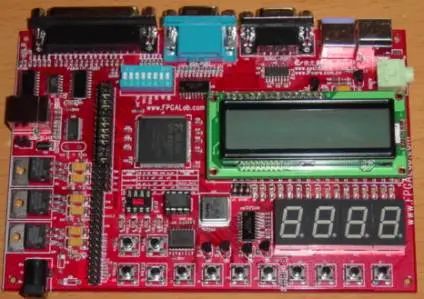

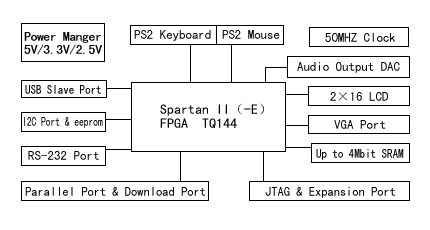

Xilinx公司和Altera公司均提供了許多用于評估IP Core的FPGA評估板,如USB、MAC、IEEE1394等等。許多第三方設計中心,如Insight,還開發了用于SOPC系統集成的Virtex II MicroBlaze評估板和Virtex II Pro PPC405評估板等等。Xilinx FPGA的國內專業設計公司長沙依元素科技(http://www.eestd.com)還開發了用于測評各類基本IP Core以及學習培訓用途的數字刀劍?系列 (DigitalSword?Series Kit)評估板,如圖1所示,該系列評估板提供了VGA、LCD、音頻、鍵盤鼠標、串口、并口、USB Slave、I2C等電平接口,并提供了標準擴展總線以及豐富的子板功能模塊支持。

圖1(a) 數字刀劍 系列之火龍刀

圖1(b) 數字刀劍?系列FPGA評估板結構框圖

3 基于Xilinx FPGA的嵌入式系統設計

3.1 FPGA基本開發流程與開發工具

FPGA基本開發流程主要包括設計輸入(Design Entry);設計仿真(Simulation);設計綜合(Synthesize);布局布線(Place & Route);配置(Configuration)五個主要步驟。

設計輸入主要有原理圖輸入和HDL輸入兩種方式,一般開發商都同時支持兩種輸入方式。有些熟悉硬件設計的工程師開始喜歡利用原理圖進行設計,這種方法非常直觀,但基于可移植性和規范化方面的考慮,絕大部分深入FPGA設計和ASIC設計的工程師最終都將統一到HDL平臺上來。

設計仿真包含功能仿真和時序仿真兩項主要內容,功能仿真忽略了綜合和布局布線導致的時延等因素,僅僅從邏輯上進行仿真,這對設計思路的驗證是有幫助的,但必須通過時序仿真作進一步驗證,發現并修正時序問題。

設計綜合將HDL語言生成用于布局布線的網表和相應的約束。綜合效果直接導致設計的性能和邏輯門的利用效率,因此,許多可編程邏輯器件開發商都支持第三方綜合和仿真工具,著名的有:Synplicity、Synopsys和ModelSim等。

布局布線工具利用綜合生成的網表,在FPGA內部進行布局布線,并生成可用于配置的比特流文件。布局布線工具與可編程邏輯器件工藝及其布線資源密切相關,一般由可編程邏輯器件開發商直接提供。

隨著可編程邏輯器件容量的不斷增大和設計性能要求的不斷提高,對傳統的FPGA開發工具提出了挑戰。以Xilinx公司為例,應IP Core開發和集成的需要,開發了IP Core使用工具Core Generator和IP Core包裝工具IP Capture;提供了模塊化設計工具Modular Design用于超大規模設計的團隊項目開發;用片內邏輯分析儀ChipScope ILA進行片內邏輯調試;Xpower則用于設計功耗分析并得出相應的解決方案;還有System Generator結合Simulink甚至可以簡單地實現數字信號處理模型(如FIR濾波器和FFT等)的FPGA硬件實現。此外,一些有爭議的設計工具,如基于C語言的FPGA開發工具DK1等為超大容量FPGA設計和復雜邏輯設計提供了值得嘗試的途徑。

3.2 處理器IP Core:Micro Blaze與PPC405

將處理器IP Core嵌入到可編程邏輯器件是基于FPGA的嵌入式系統設計的前提條件,目前,國內外許多單位已成功的將51單片機、ARM和PPC等處理器內核嵌入各種可編程邏輯器件并進行了應用系統的設計,其中最著名的要數Xilinx公司的Micro Blaze和Altera公司的Nois了。Xilinx從Pico Blaze到Micro Blaze,再到PPC405,完成了從8位單片機到32位微處理器的逐步完善和性能提升。

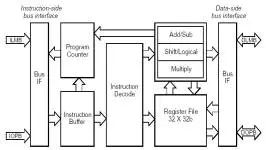

Micro Blaze 是一個專門為Xilinx FPGA優化的RISC嵌入式軟處理器,符合IBM Core Connect標準,能夠與PPC405系統無縫連接,Micro Blaze軟處理器內核的結構如圖2所示,

圖2 Micro Blaze IP Core結構框圖

它具備以下基本特征:

·32個32bit通用寄存器

·硬件乘法器(僅限Virtex II系列)

·32bit地址總線和32bit數據總線

·三操作數32bit指令字,兩種尋址模式

·獨立的片內程序32bit總線和數據總線

·片內總線遵循OPB(On-chip Peripheral Bus)標準

·通過LMB(Local Memory Bus)訪問片內Block RAM

Micro Blaze是一個非常簡化,但有具有較高性能的軟處理器內核,他可以在性價比很高的Spartan II(-E)系列FPGA上實現,系統時鐘頻率為75MHZ,僅占用400個Slice資源,相當于10萬門FPGA容量的三分之一,而10萬門的Spartan II系列FPGA的批量目標市場價格僅為10美元左右,非常適合消費類嵌入式產品應用需求。

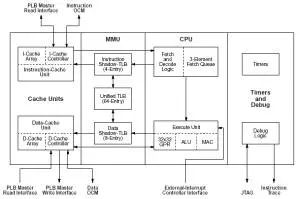

在Xilinx最新一代FPGA Virtex II Pro中,嵌入了IBM公司的PPC405 RISC結構硬處理器(如圖3所示),

圖3 PPC405 IP Core結構框圖

該處理器內核具備以下基本特征:

·32位、Harvard結構,300MHZ以上工作頻率

·支持IBM Core Connect總線標準

·符合PowerPC UISA標準

·低功耗:0.9mW/MHZ

·硬件乘法和除法單元

·32個32bit通用寄存器

·16KB雙端口程序緩存

·16KB雙端口數據緩存

·內存管理單元(MMU)支持

·獨立的調試和跟蹤接口

PPC405硬處理器內核性能上與現有的EPPC Core完全一致,含有PPC405 Core 的Virtex II Pro系列FPGA還附加了Gbit收發器和18×18硬件乘法器以及龐大的可編程邏輯資源,非常適合于通信、圖像信號處理以及復雜應用系統的設計,并提供了更加靈活的設計模式。

3.3 基于Micro Blaze和PPC405 Core的SOPC軟硬件開發

基于嵌入式處理器內核的SOPC系統開發是一個軟硬件協同設計的過程,一方面,它極大地提高了系統設計的靈活性和快速的設計迭代周期,使整個開發過程變得更加可控;另一方面,一些新的調試和設計問題,如邏輯分析儀和數字示波器的接入等,對調試設備和調試手段提出了更高的要求,為了盡可能避免問題的產生,要求有更好的設計工具和集成開發環境,保證IP Core資源的可用性和設計實現的一致性,讓設計工程師從煩瑣的內部時序調試中解放出來。

Xilinx提供了針對Micro Blaze Core應用系統開發的集成開發環境MDK,該開發環境包含了用于硬件描述和系統生成的Platform Generator、用于軟件設計和編譯的Micro Blaze IDE,GDB調試可通過FPGA配置JTAG接口進行,無需任何附加的調試硬件,配合Foundation ISE4.2和FPGA目標板即可進行全功能開發,MDK還包含了UART、GPIO、Watchdog、Timer/Counter、EMC和中斷控制等基本處理器外設庫,用戶可以添加兼容OPB總線標準的任意IP Core。Insight和依元素科技均提供了功能全面的Micro Blaze Core評估工具。

PPC405 Core是一個高性能的處理器內核,它具有獨立于FPGA JTAG的調試端口和更加復雜的調試功能,我們甚至可以將基于PPC405 Core的SOPC調試直觀地理解為基于IBM PPC405處理器和大容量FPGA的單板機調試,只不過這個單板機無需進行傳統的PCB設計和調試,設計迭代過程全部在計算機上進行。PPC405 Core的軟件集成開發環境支持傳統的IBM PPC405開發環境,Xilinx提供了相應的系統集成開發環境和GNU軟件開發工具包支持。第三方軟件開發商Wind River和Montvisa已分別宣布其VxWorks和HardHat Linux實時操作系統(RTOS)及其集成開發環境支持Virtex II Pro 系列FPGA,Insight和Avnet已開始銷售含有Virtex II Pro FPGA的高端評估板。依元素科技也推出了用于開發PowerPC系列處理器的GNU集成開發工具和利刃?系列調試工具,以及含有PowerPC處理器的原型評估板。

4 基于Internet可重配置邏輯(IRL)

4.1 IRL技術的基本特征與應用

Internet Reconfigurable Logic (IRL)是Xilinx倡導的一種新的FPGA設計理念,其核心是通過Internet對遠程設備的硬件設計和軟件程序進行升級、重構、調試和監控,這種設計理念伴隨著嵌入式Internet技術的蓬勃發展必將對嵌入式設備的設計模式產生深遠的影響。

IRL包括三個方面的基本要素:

·含有配置bit流或應用程序的主機

·含有配置功能的目標系統

·Internet或遠程訪問介質

在Internet環境下,可通過Web Browser訪問遠程目標機,通過HTTP、FTP協議、Java Applet和CGI等功能實現數據、文件傳輸和交互控制功能。在某些特殊環境下,遠程訪問介質可以是PSTN、無線網絡或其它特殊媒介,這在某些工業控制場合以及軍事應用中是常見的。

IRL技術可以應用于許多場合,諸如:在部分功能沒有完成全面測試之前就可以先將產品投放市場;故障設備的遠程維護;遠程修復產品使用過程中發現的Bug;對已售出的產品升級新的功能;對新出現的標準和協議予以支持等等。總而言之,采用IRL技術將帶給我們的產品三個明顯的優勢:縮短產品上市時間;減少產品維護費用;延長產品生命周期。

4.2 IRL技術的設計實現

在基于Web Browser的條件下,主機端的應用程序將達到最簡化,主機端無需安裝任何特殊應用程序就可完成對遠程設備的操作,這種簡化對用戶而言是必要的。這樣,目標機的設計就是IRL技術實現的全部內容。

一般而言,目標機端IRL模塊應實現以下功能:

·以太網或Modem接入

·TCP/IP或TCP/IP+PPP協議棧

·Http Web Server

·支持CGI、ASP或Java Script

·FPGA配置時序,至少支持JTAG配置模式

·足夠的存儲空間和配置故障恢復功能

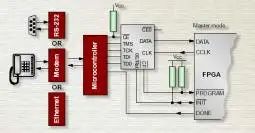

在嵌入式Internet技術和處理器的支持下,這些功能的實現已經不是技術上的瓶頸了,圖4給出了依元素科技也開發的IRL評估模塊原理框圖,

圖4 基于Rabbit2000的IRL模塊原理框圖

該這種實現方式是一種基于單片機或專用處理器的IRL實現方式。Avnet推出了基于PowerPC和PMC總線的高端IRL技術評估板。

在本文研究的SOPC設計技術的基礎上,FPGA甚至能夠通過內部嵌入式處理器內核(如Micro Blaze和PPC405)及其軟件支持,實現對自身的重構和升級。

5 結束語

隨著可編程邏輯器件工藝的不斷進步和開發工具的不斷增強,FPAG將更加廣泛的應用在各個領域,FPGA的將在更廣泛的范圍普及,成本和價格將不再成為我們拒絕在設計中采用FPGA的理由。我們有理由相信,SOPC、IRL等設計理念將會對我們的設計方式產生新的變革,也必將給每一位嵌入式工程師帶來有益的思路和更加寬廣的創意空間。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:基于Xilinx FPGA的嵌入式系統設計

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1643文章

21960瀏覽量

614061

原文標題:基于Xilinx FPGA的嵌入式系統設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于Xilinx FPGA的嵌入式系統設計

基于Xilinx FPGA的嵌入式系統設計

評論