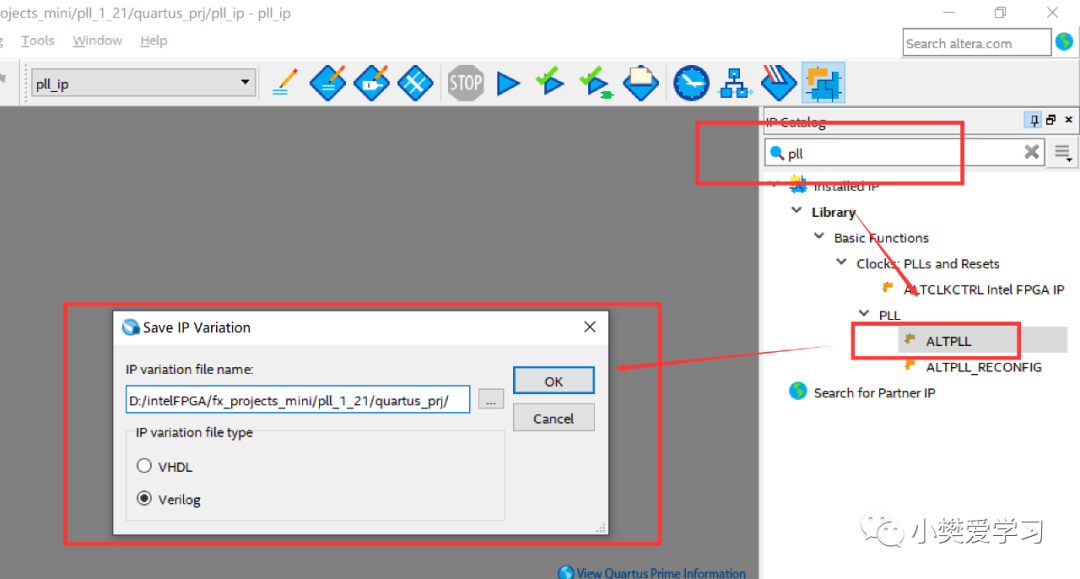

1.在ip目錄里搜索pll,選擇ALTPLL,點擊打開后設置名稱并自動保存在目錄中。

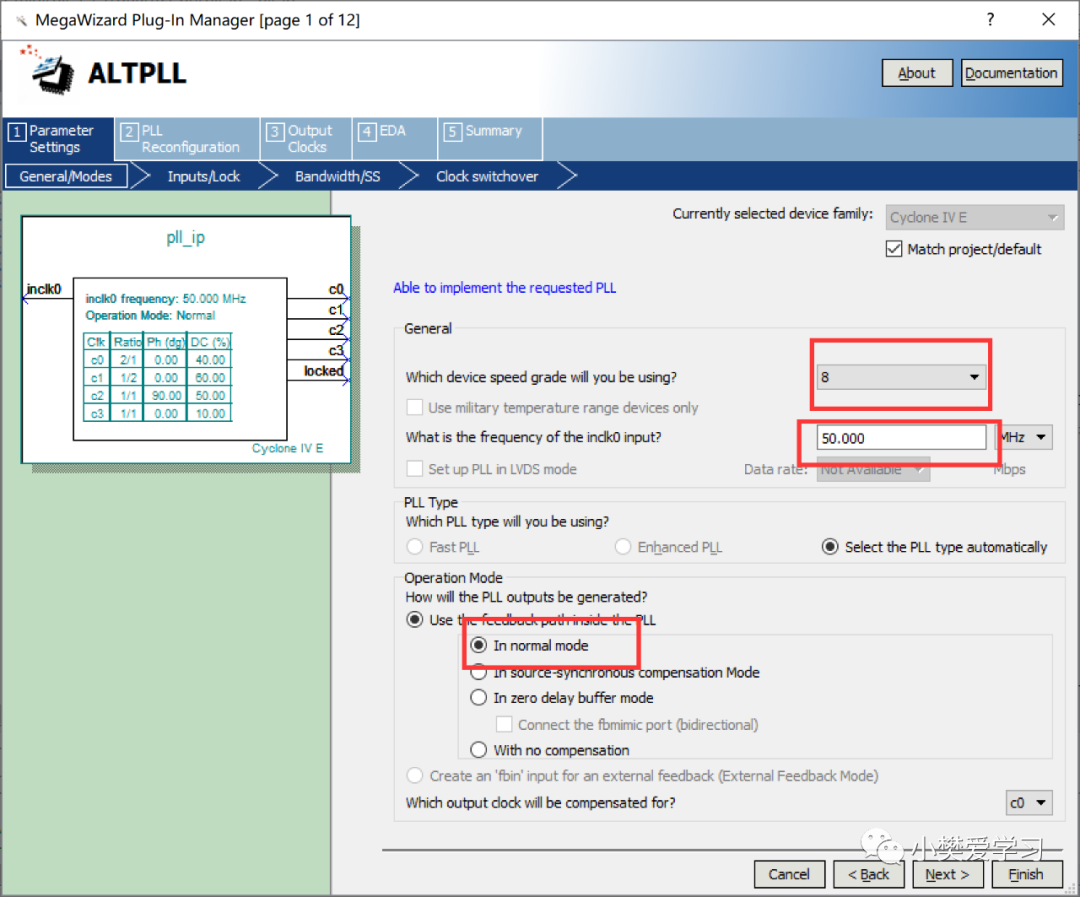

2.在打開彈窗內設定如下三個位置的內容,其中50Mhz是板載的外部時鐘的頻率,下方選擇的模式是默認。

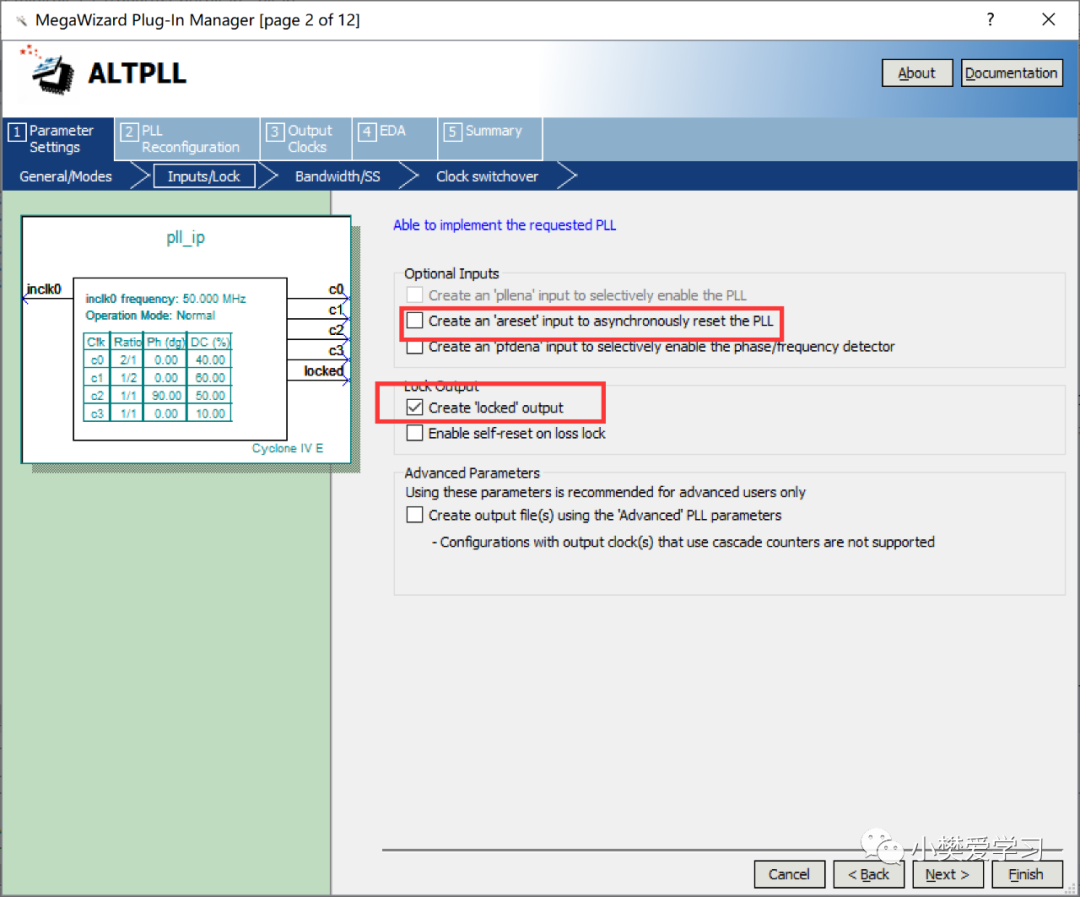

3.選擇第二個小選項卡,取消勾選areset,這個一般用不到,而且使用了容易出錯。勾選locked,這個輸出信號的輸出為高電平時,說明輸出的時鐘有效,否則無效,方便查看。

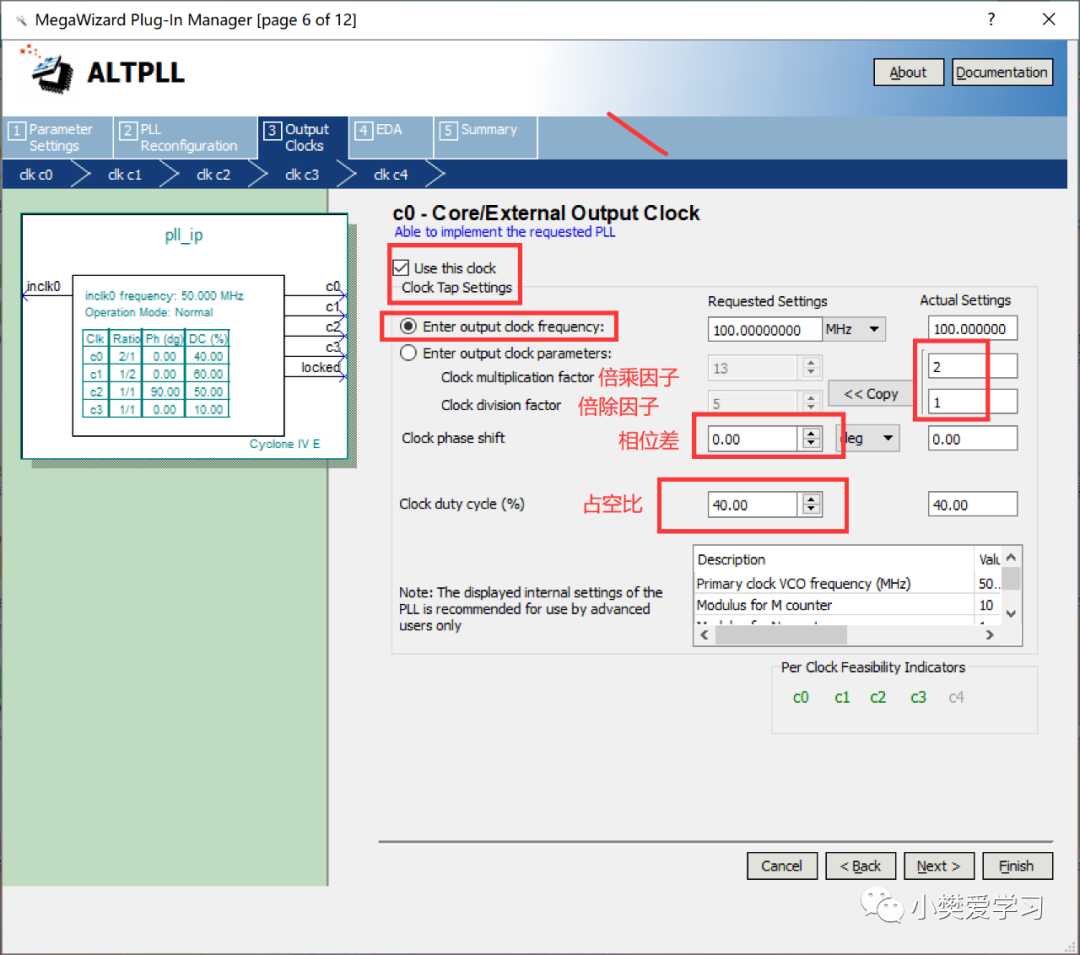

4.選擇輸出時鐘地選項卡,下方有clk0~4,最多可以有五個輸出,勾選上第一個紅框就是使用該輸出時鐘。接著勾選上第二個紅框,就可以在右方輸入需要輸出的時鐘,這里選擇100Mhz,此時右方會自動顯示倍乘因子和倍除因子的值,輸入的50Mhz÷1×2=100Mhz。也可以勾選第二個紅框下方的選項,自行根據所需要的輸出時鐘的頻率修改倍乘因子和倍除因子的值,下方剩下兩個紅框中對應相位差和占空比的調節。這里我用了四個輸出,具體參數可以看左方的框圖內顯示。

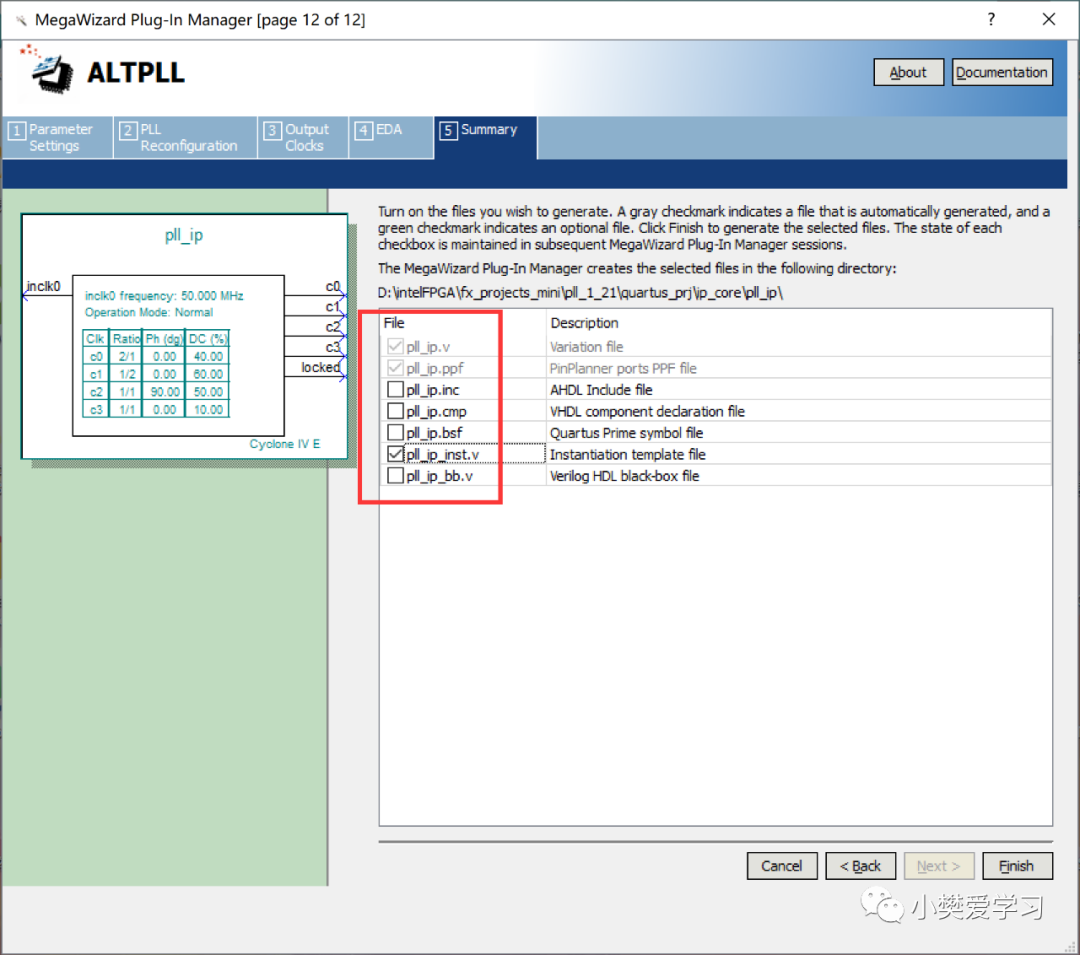

5.在最后一個選項卡中勾選如下圖的設置,這些文件的區別我也不懂,記就完事了。其它的選項卡都是高級設置,暫時用不到,全部默認即可,點擊生成。

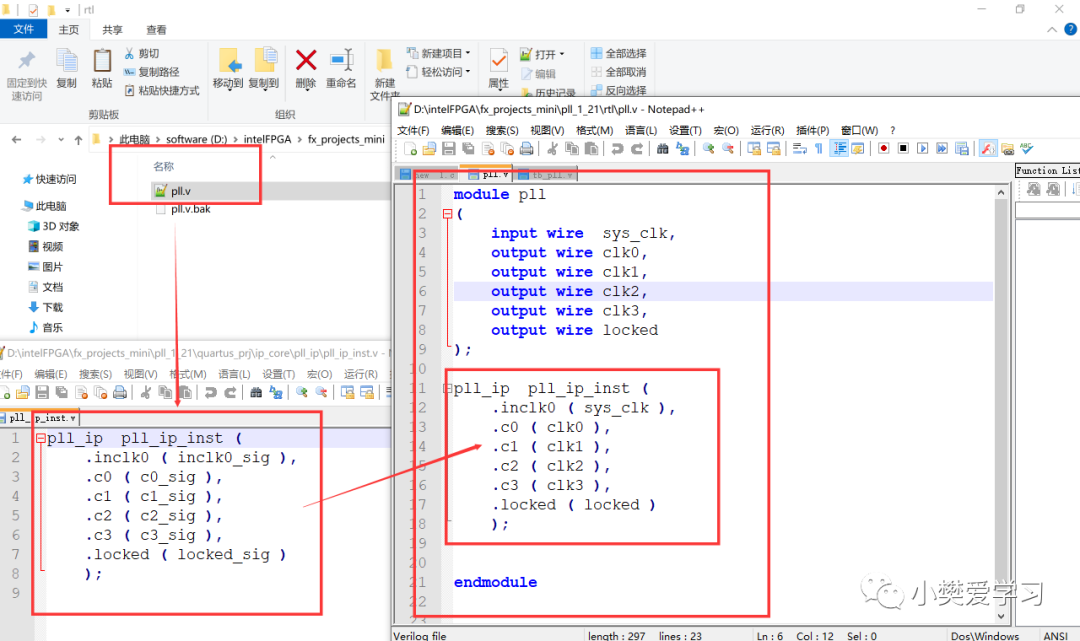

6.在rtl文件夾(用戶代碼文件夾)里新建一個頂層文件(pll.v文件),將pll_ip實例化,即在頂層文件中調用,再打開quartus軟件,添加頂層文件,全編譯。

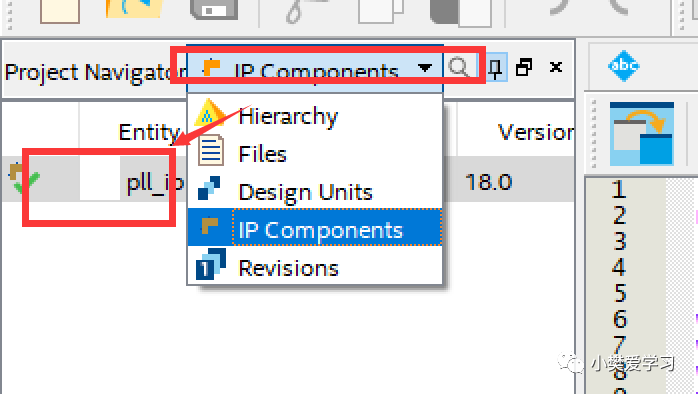

7.如果需要再修改pll_ip的內容,只要在此處點擊即可,到此該內容已經結束,下面跑一下仿真。

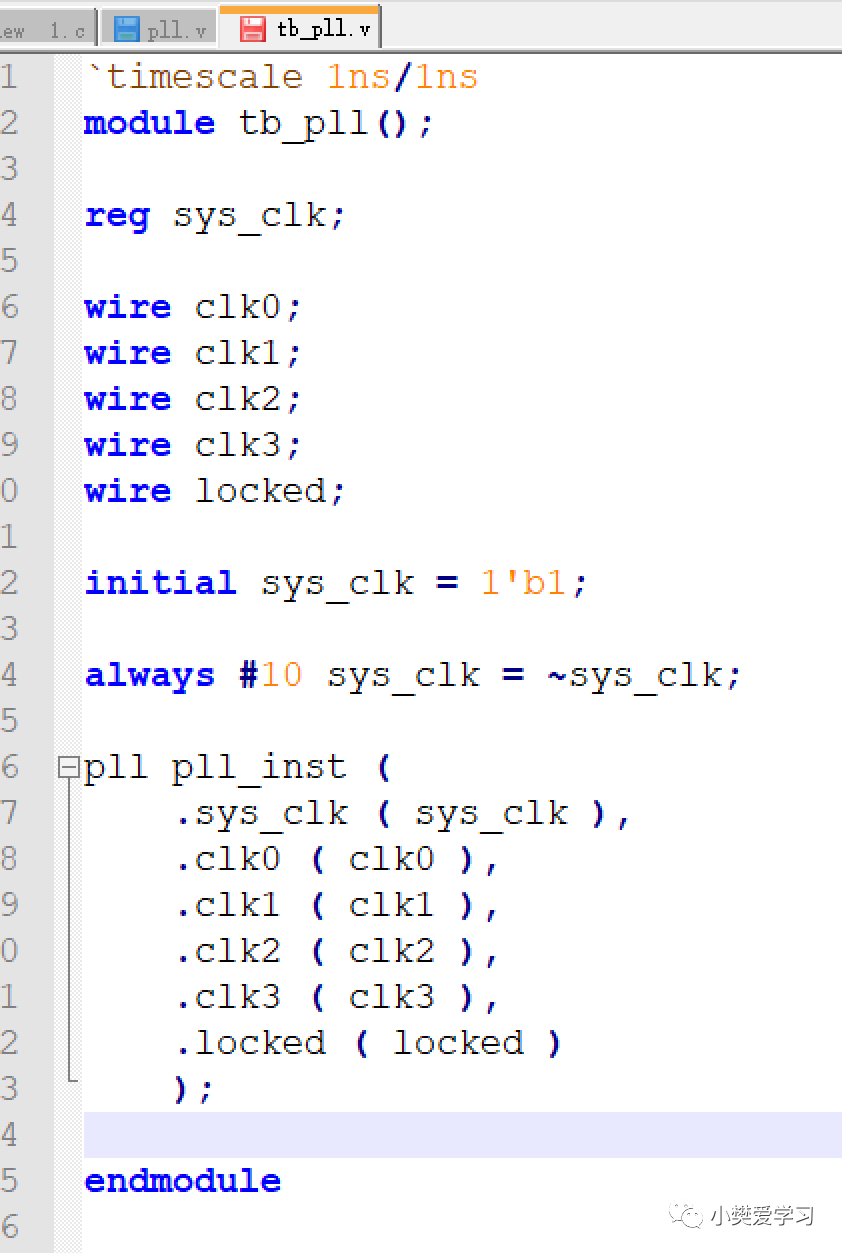

8.新建一個仿真文件,如下圖。

9.在quartus軟件中添加該仿真文件,全編譯。這里補充一個modelsim的安裝和破解方法(我的電腦跑仿真一直會有問題,嘗試過網上很多方式都不成功,這里放一個我自己電腦能成功的方法)

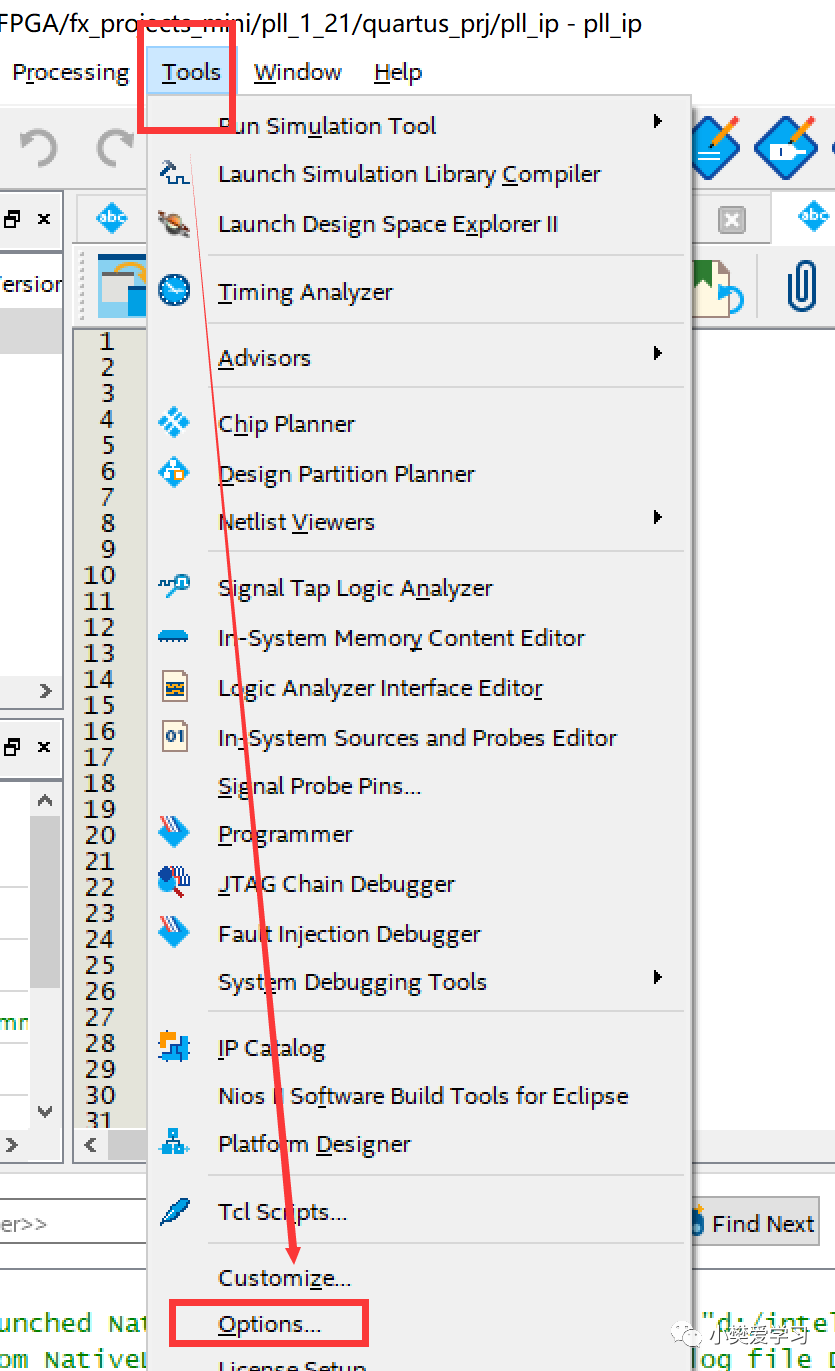

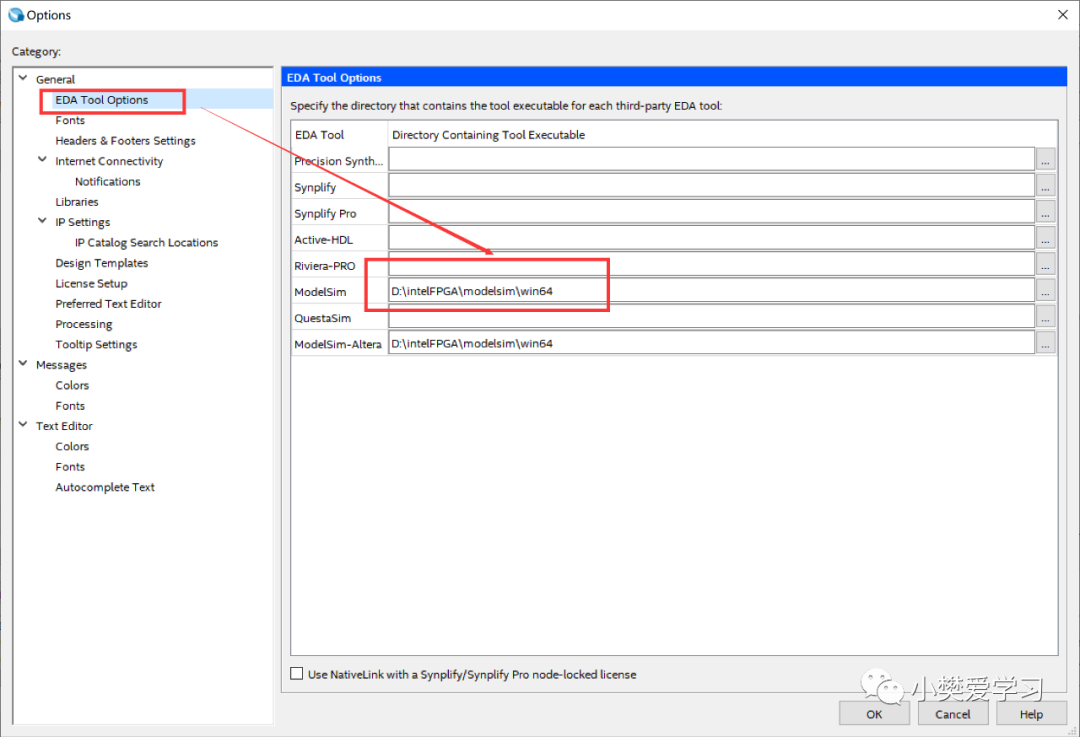

10.破解安裝完成后,可以自己點擊modelsim軟件,能正常打開應該就是成功了。如果和我一樣,在quartus運行時去安裝并破解modelsim,需要重新啟動quartus,否則會失敗。接著按照下圖的操做進行設置,打開tool—>options,在彈窗內選擇EDA Tool Options,在右方紅框內選擇modelsim的安裝目錄,要定位到win32或win64。下方有個modelsim_altera ,好像是quartus自帶的仿真,但是我嘗試配置,一直沒成功過,可以忽略。

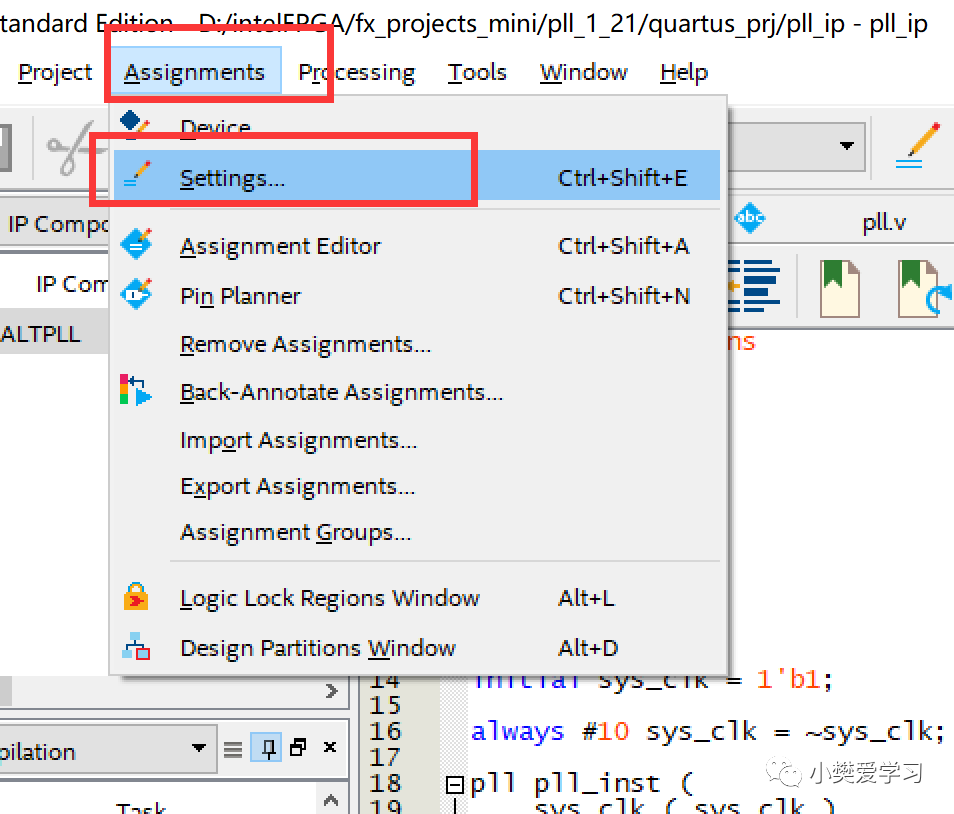

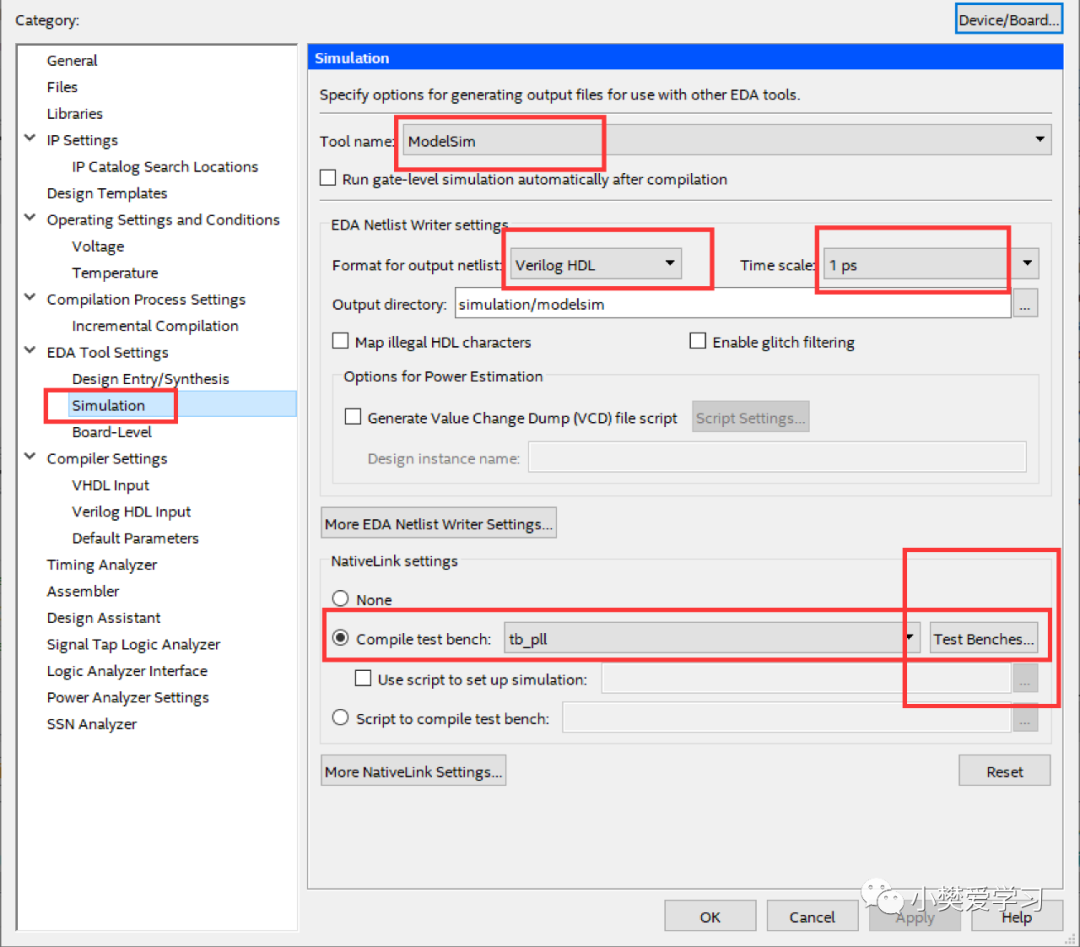

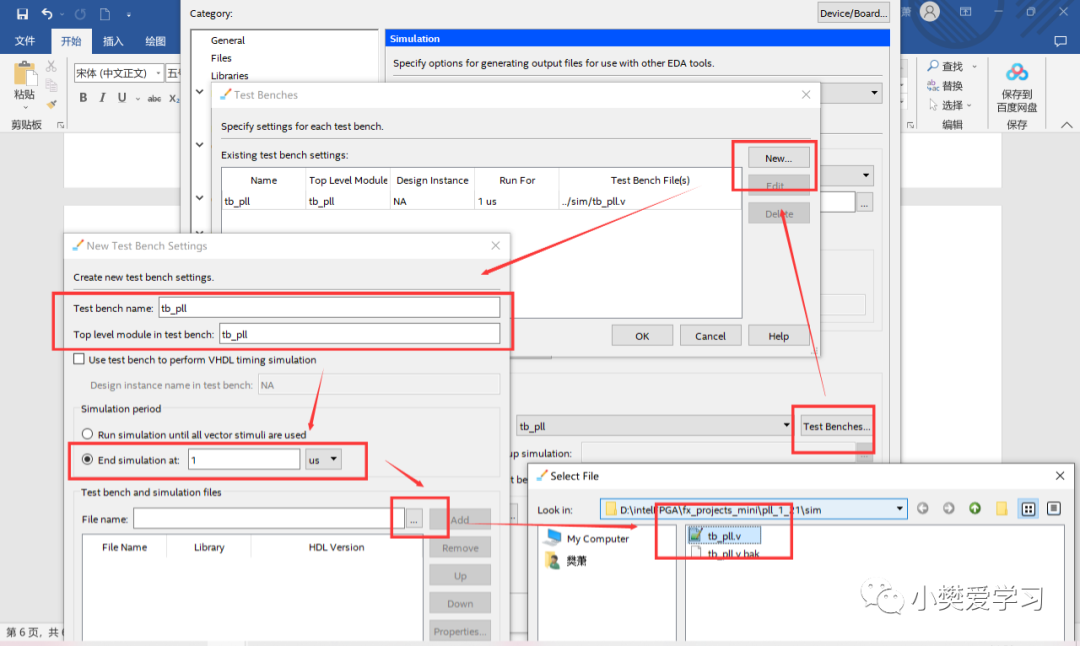

11.仿真軟件目錄配置完成后,在assignments里選擇settings,再按照下方圖片內容配置,大部分都是默認的,點擊test benches,按下方箭頭順序操做,新建一個仿真,自己命名,然后設置結束時間是1us,最后將寫好的仿真文件(tb_pll.v文件)添加進去即可。

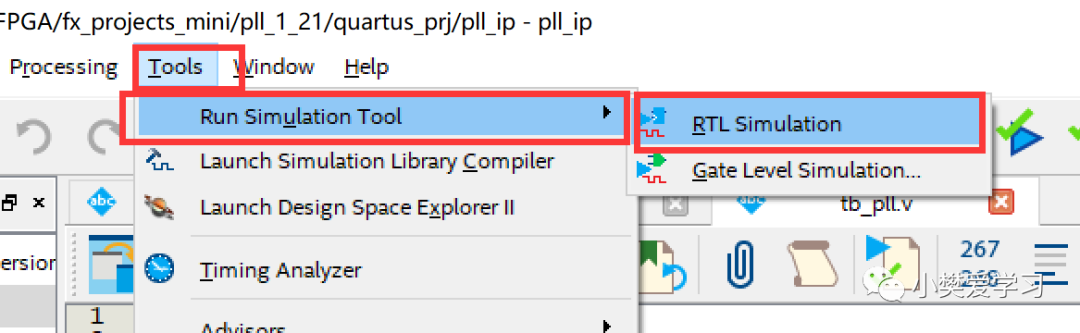

12.點擊如下圖按鈕,開始仿真。

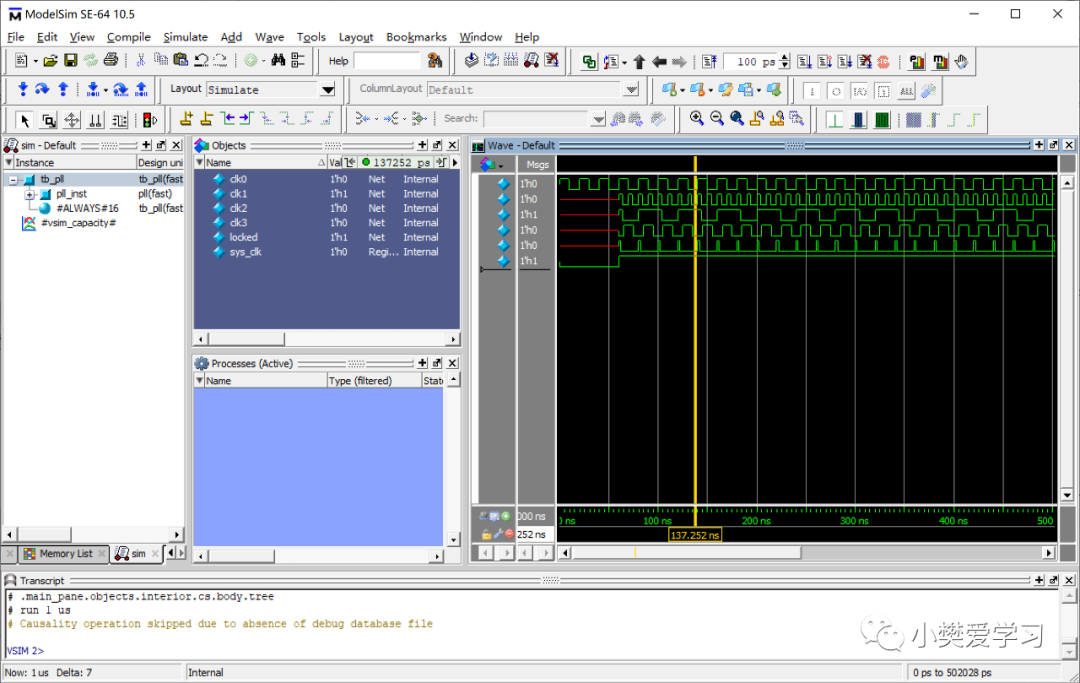

13.仿真結束,出現波形。可以看到波形和之前我在pll_ip核的設定一樣,不同的頻率,相位,占空比,pll_ip核的調用到此結束。

-

EDA工具

+關注

關注

4文章

272瀏覽量

32585 -

時鐘頻率

+關注

關注

0文章

50瀏覽量

20615 -

高電平

+關注

關注

6文章

198瀏覽量

21898 -

MODELSIM仿真

+關注

關注

0文章

15瀏覽量

7459 -

PLL電路

+關注

關注

0文章

92瀏覽量

6714

發布評論請先 登錄

XILINX FPGA IP之MMCM PLL DRP時鐘動態重配詳解

【鋯石A4 FPGA試用體驗】IP核之PLL(一)新建IP核

xilinx FPGA的FFT IP核的調用

勇敢的芯伴你玩轉Altera FPGA連載63:PLL IP核創建于配置

【正點原子DFPGL22G開發板體驗】內置IP核使用體驗-PLL之呼吸燈

QUARTUS II中IP核的調用方法(圖文詳解)

Xilinx Vivado的使用詳細介紹(3):使用IP核

lattice DDR3 IP核的生成及調用過程

PLL_IP核的調用流程詳解

PLL_IP核的調用流程詳解

評論