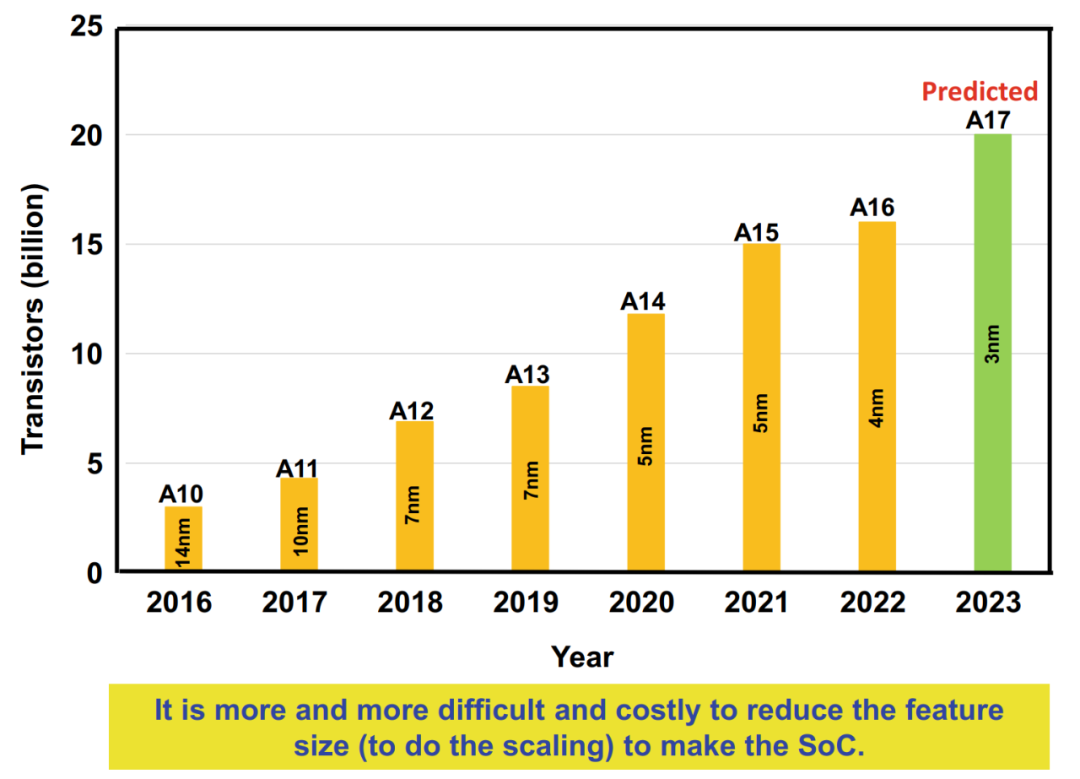

摩爾定律描述了集成電路上晶體管數(shù)量大約每?jī)赡攴环慕?jīng)驗(yàn)規(guī)律,它對(duì)計(jì)算技術(shù)進(jìn)步來(lái)說(shuō)至關(guān)重要,比如處理速度或計(jì)算機(jī)價(jià)格。早在1965年,戈登·摩爾(Gordon Moore)就曾指出:“用單獨(dú)封裝和互連的較小功能構(gòu)建大型系統(tǒng)可能會(huì)更經(jīng)濟(jì)。”

幾十年來(lái),晶圓廠成功實(shí)現(xiàn)了數(shù)字能力和晶體管密度的指數(shù)級(jí)增長(zhǎng)。今天,芯粒(又稱Chiplet)等新的工藝技術(shù)與先進(jìn)封裝方案不僅沒有違反摩爾定律,反而還在為延續(xù)摩爾定律,繼續(xù)實(shí)現(xiàn)數(shù)字縮放進(jìn)步而賦能。

雖然Chiplet近年來(lái)越來(lái)越流行,將推動(dòng)晶體管規(guī)模和封裝密度的持續(xù)增長(zhǎng),但從設(shè)計(jì)、制造、封裝到測(cè)試,Chiplet和異構(gòu)集成也面臨著多重挑戰(zhàn)。因此,進(jìn)一步通過(guò)減少缺陷逃逸率,降低報(bào)廢成本,優(yōu)化測(cè)試成本通過(guò)設(shè)計(jì)-制造-測(cè)試閉環(huán)實(shí)現(xiàn)良率目標(biāo)已成為當(dāng)務(wù)之急。

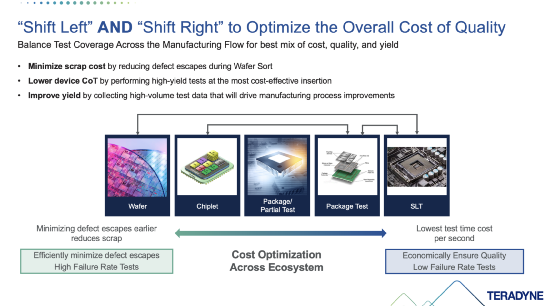

總體質(zhì)量成本優(yōu)化策略至關(guān)重要

當(dāng)我們處理更復(fù)雜的測(cè)試流程時(shí),比如KGD(Known Good Die)測(cè)試、最終測(cè)試和系統(tǒng)級(jí)測(cè)試,優(yōu)化總體質(zhì)量成本的策略仍然至關(guān)重要。策略背后的關(guān)鍵點(diǎn)包括以下幾個(gè)方面:

在設(shè)計(jì)過(guò)程的初期,新產(chǎn)品導(dǎo)入或大批量生產(chǎn)之前,設(shè)計(jì)人員和測(cè)試工程師需要進(jìn)行充分協(xié)作,利用通用工具進(jìn)行芯片驗(yàn)證和故障調(diào)試;

將某些測(cè)試流程轉(zhuǎn)移到整個(gè)流程的早期,以減少KGD集成之前的早期缺陷;

將一些測(cè)試推遲到制造過(guò)程的后期,以降低測(cè)試成本,進(jìn)一步優(yōu)化成本;

隨著制造過(guò)程的成熟和穩(wěn)定,對(duì)這些過(guò)程進(jìn)行大數(shù)據(jù)分析,以便調(diào)整制造過(guò)程中的測(cè)試流程,從而優(yōu)化總體質(zhì)量成本。

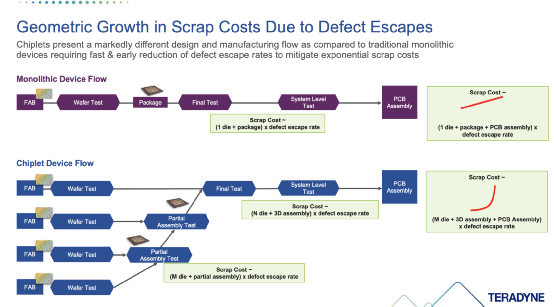

缺陷逃逸導(dǎo)致報(bào)廢成本呈幾何級(jí)數(shù)增長(zhǎng)

與傳統(tǒng)單片器件相比,Chiplet的設(shè)計(jì)和制造流程明顯不同,與制造傳統(tǒng)單片半導(dǎo)體器件相關(guān)聯(lián)的報(bào)廢成本實(shí)際上是線性的,包括單芯片成本、封裝和組裝成本。Chiplet或3D先進(jìn)封裝的制造流程在廢料成本的積累方面有很大不同。具體講,從制造到組裝,報(bào)廢成本呈幾何級(jí)數(shù)增加,因?yàn)槠渲邪硕鄠€(gè)管芯、多芯片部分組件或全3D封裝的報(bào)廢成本。

雖然3D封裝是摩爾定律繼續(xù)向前的的推動(dòng)者,不過(guò)這種方法的經(jīng)濟(jì)可行性在于,需要能夠在制造流程的早期減少缺陷逃逸率,從而降低報(bào)廢成本。

“左移”還是“右移”?

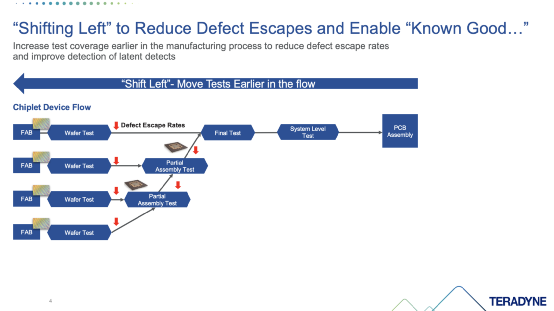

“左移”是一種在制造流程早期降低缺陷逃逸率降低報(bào)廢成本,從而3D組件的總體制造成本降至最低的策略。“左移”是在制造過(guò)程的早期增加測(cè)試覆蓋率,以降低缺陷逃逸率并改進(jìn)潛在檢測(cè)的能力。

減少缺陷逃逸的方法之一是啟用“Known Good”。為減少缺陷逃逸生產(chǎn)“Known Good”的器件,需要在包括晶圓檢測(cè)和部分封裝的階段,即制造流程的早期,提高測(cè)試覆蓋范圍,同樣,還可以在流程中增加額外的測(cè)試,以識(shí)別新的故障類型或故障模式,例如通過(guò)邊界掃描的測(cè)試覆蓋發(fā)現(xiàn)與部分組件相關(guān)的互連問題。

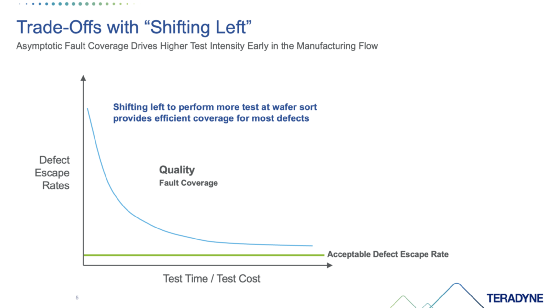

當(dāng)然,作為實(shí)現(xiàn)“Known Good”的手段,“左移”也需要進(jìn)行權(quán)衡。例如,在制造流程的早期增加測(cè)試強(qiáng)度,可以大大降低缺陷逃逸率。然而,“左移”在逐漸接近可接受的缺陷逃逸率時(shí),會(huì)導(dǎo)致測(cè)試成本持續(xù)增加,而缺陷逃逸率降低的帶來(lái)的報(bào)廢成本的減少則會(huì)遞減。

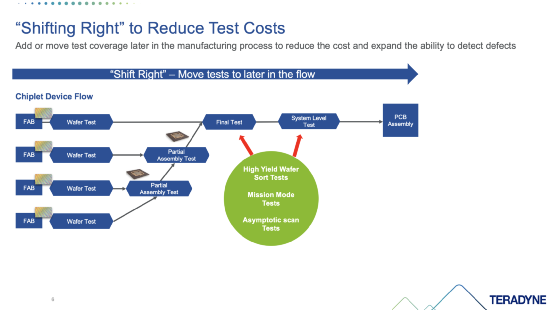

“右移”是增加制造流程后期的測(cè)試覆蓋率,擴(kuò)大檢測(cè)缺陷的能力,在降低成本同時(shí)確保質(zhì)量水平的可行手段。

通常,晶圓測(cè)試良率較高的測(cè)試項(xiàng)、任務(wù)模式測(cè)試或需要較長(zhǎng)測(cè)試時(shí)間掃描測(cè)試的高良率測(cè)試是“右移”的理想候選者。這些測(cè)試可以轉(zhuǎn)移到最終測(cè)試或系統(tǒng)級(jí)測(cè)試階段,或者在兩者之間靈活管理,在實(shí)現(xiàn)質(zhì)量目標(biāo)的前提下進(jìn)一步降低成本。

不管是“左移”還是“右移”,都是為了在整個(gè)制造流程中、質(zhì)量和良率的最佳組合,最終優(yōu)化整體質(zhì)量成本。具體的策略包括:通過(guò)降低晶圓檢測(cè)過(guò)程中的缺陷逃逸率,最大限度地降低報(bào)廢成本;以最高效的方式實(shí)現(xiàn)量產(chǎn)測(cè)試,從而降低芯片的測(cè)試成本;通過(guò)大數(shù)據(jù)推動(dòng)整個(gè)制造工藝的閉環(huán)和改進(jìn),從而提高良率。

那么在生產(chǎn)中,要選擇將測(cè)試“左移”還是“右移”呢?

兩者兼而有之是問題的答案。為了管理整體質(zhì)量成本,有必要“左移”和“右移”。左移提供了一種在制造流程早期降低缺陷逃逸率的方法,而右移則可以實(shí)現(xiàn)在可控測(cè)試成本的同時(shí)達(dá)到需要的產(chǎn)品質(zhì)量水平。

“左移”增加了晶圓檢測(cè)的覆蓋率,通過(guò)高故障率的結(jié)構(gòu)、參數(shù)、掃描及壓力測(cè)試,為工藝改進(jìn)和優(yōu)化提供有價(jià)值的信息;“右移”為檢測(cè)“難以找到”或需要長(zhǎng)時(shí)間掃描的測(cè)試或壓力測(cè)試提供了一種經(jīng)濟(jì)的手段。

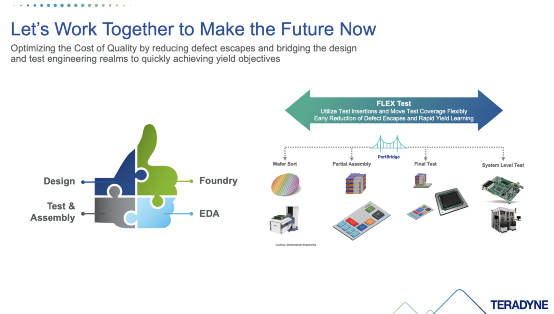

在面對(duì)“左移”還是“右移”的選擇中,優(yōu)化測(cè)試策略是一個(gè)動(dòng)態(tài)和持續(xù)的過(guò)程。大數(shù)據(jù)為測(cè)試策略的決策提供了依據(jù)。泰瑞達(dá)靈活測(cè)試方案和工具組合,可以在整個(gè)芯片制造流程中靈活調(diào)整測(cè)試策略,持續(xù)優(yōu)化制造成本和保障質(zhì)量。

彌合從設(shè)計(jì)到測(cè)試的差距

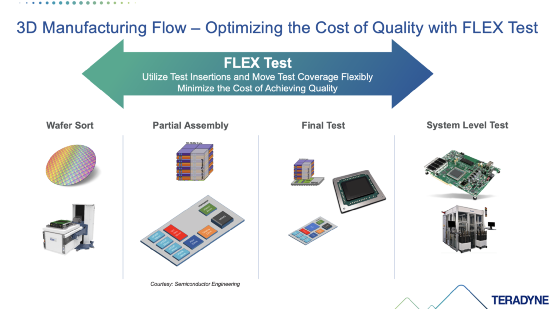

Chiplet是先進(jìn)封裝中的組成單元,而3D是先進(jìn)封裝的工藝手段。利用靈活測(cè)試可以優(yōu)化3D制造流程的質(zhì)量成本。靈活測(cè)試可以移動(dòng)測(cè)試覆蓋范圍,包括晶圓檢測(cè)、部件裝配、最終測(cè)試、系統(tǒng)級(jí)測(cè)試,最大限度地降低實(shí)現(xiàn)質(zhì)量的成本。

事實(shí)上,在制造流程的早期,最大限度地降低缺陷逃逸并不是一個(gè)靜態(tài)問題。學(xué)習(xí)、工藝改進(jìn)和新技術(shù)都為實(shí)現(xiàn)整個(gè)制造流程中測(cè)試覆蓋率的平衡提供了機(jī)會(huì)。因此,在制造流程中靈活地“左移”或“右移”測(cè)試覆蓋范圍的能力很重要。這種靈活性將有助于應(yīng)對(duì)制造過(guò)程不斷發(fā)展的成熟度,并對(duì)質(zhì)量成本的持續(xù)優(yōu)化做出響應(yīng)。

事實(shí)上,減少缺陷逃逸并非事情的全部,還需要考慮良率如何。

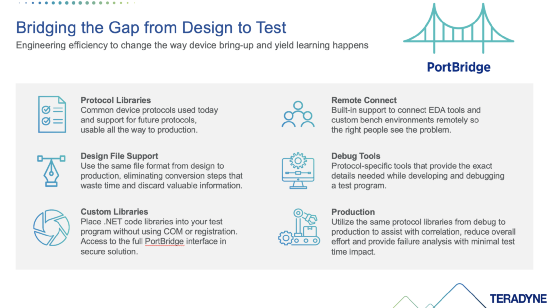

為了實(shí)現(xiàn)這一點(diǎn),就要彌合從設(shè)計(jì)到測(cè)試的差距,提升工程效率,以改變器件的調(diào)試(debug)和良率學(xué)習(xí)(yield learning)方式。新的工作流程需要設(shè)計(jì),制造和測(cè)試工程團(tuán)隊(duì)無(wú)縫合作的方式,以加快器件的開發(fā)并產(chǎn)生學(xué)習(xí)效果。不僅需要在SLT和ATE測(cè)試系統(tǒng)上啟用EDA和JTAG工具,還需要通過(guò)一組通用的庫(kù)和調(diào)試工具,讓設(shè)計(jì)和DFT工程師可以無(wú)縫合作,同時(shí)共享關(guān)鍵見解,從而加速芯片開發(fā)并縮短學(xué)習(xí)時(shí)間。

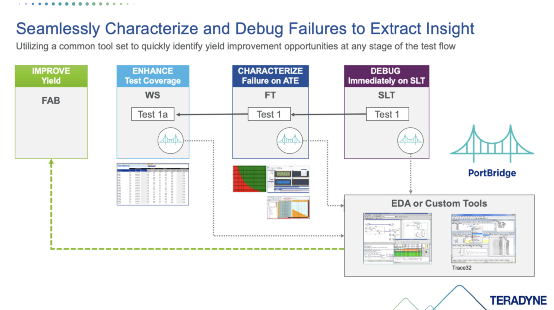

值得一提的是,通用的工具集可以彌合設(shè)計(jì)和測(cè)試之間的差距,它可以在制造流程的任何階段部署,以識(shí)別、實(shí)施和驗(yàn)證提高良率的機(jī)會(huì)。例如,該工具集可以在系統(tǒng)級(jí)測(cè)試中調(diào)試故障,在最終測(cè)試插入中對(duì)故障進(jìn)行更深入的驗(yàn)證,在晶圓檢測(cè)中增強(qiáng)的測(cè)試覆蓋率,以減少缺陷逃逸,并揭示生產(chǎn)流程中的“秘密”,以改進(jìn)器件或工藝,完全消除缺陷并提高良率。

設(shè)計(jì)和測(cè)試攜手創(chuàng)造未來(lái)

快速識(shí)別是在制造過(guò)程早期經(jīng)濟(jì)地降低缺陷逃逸率的關(guān)鍵。靈活的測(cè)試流程,加上設(shè)計(jì)和測(cè)試工程領(lǐng)域能力的整合,將有助于快速識(shí)別、調(diào)試和消除故障,同時(shí)實(shí)現(xiàn)最佳的質(zhì)量成本。

與3D Fabric Alliance中的EDA、設(shè)計(jì)、代工、測(cè)試和組裝合作伙伴合作,對(duì)于充分實(shí)現(xiàn)靈活的測(cè)試流程,并收集滿足3D封裝設(shè)計(jì)的質(zhì)量目標(biāo)成本所必需的關(guān)鍵學(xué)習(xí)工具至關(guān)重要。

來(lái)自EDA公司、DFT、運(yùn)營(yíng)、晶圓代工廠、OSAT、ATE-SLT供應(yīng)商團(tuán)隊(duì)之間的合作將是成功的關(guān)鍵。讓我們一起努力創(chuàng)造未來(lái),快速實(shí)現(xiàn)良率目標(biāo)。

-

芯片

+關(guān)注

關(guān)注

459文章

52165瀏覽量

436087 -

封裝

+關(guān)注

關(guān)注

128文章

8484瀏覽量

144776 -

chiplet

+關(guān)注

關(guān)注

6文章

453瀏覽量

12863

原文標(biāo)題:Chiplet和異構(gòu)集成時(shí)代芯片測(cè)試的挑戰(zhàn)與機(jī)遇

文章出處:【微信號(hào):芯長(zhǎng)征科技,微信公眾號(hào):芯長(zhǎng)征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

全球驅(qū)動(dòng)芯片市場(chǎng)機(jī)遇與挑戰(zhàn)

板狀天線:智能時(shí)代下的挑戰(zhàn)與機(jī)遇并存

2.5D集成電路的Chiplet布局設(shè)計(jì)

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

Chiplet技術(shù)革命:解鎖半導(dǎo)體行業(yè)的未來(lái)之門

Chiplet在先進(jìn)封裝中的重要性

人工智能應(yīng)用中的異構(gòu)集成技術(shù)

高帶寬Chiplet互連的技術(shù)、挑戰(zhàn)與解決方案

異構(gòu)集成封裝類型詳解

國(guó)產(chǎn)半導(dǎo)體新希望:Chiplet技術(shù)助力“彎道超車”!

創(chuàng)新型Chiplet異構(gòu)集成模式,為不同場(chǎng)景提供低成本、高靈活解決方案

剖析 Chiplet 時(shí)代的布局規(guī)劃演進(jìn)

Chiplet和異構(gòu)集成時(shí)代芯片測(cè)試的挑戰(zhàn)與機(jī)遇

Chiplet和異構(gòu)集成時(shí)代芯片測(cè)試的挑戰(zhàn)與機(jī)遇

評(píng)論