今天給大家分享的是:

去耦電容,去耦電容PCB設(shè)計(jì)和布局

一、去耦電容

去耦電容用于濾除輸出信號(hào)的干擾,通常用于不需要交流電的放大器電路中,用來(lái)消除自激,使放大器溫度工作。

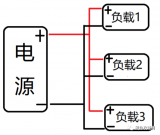

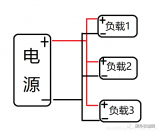

在只有一根導(dǎo)體的電路中,當(dāng)共享電源時(shí),如果有設(shè)備需要提供輸出,則導(dǎo)體的電壓同時(shí)被拉低,從而產(chǎn)生耦合到共享電路中的噪聲。

在嘈雜的環(huán)境中,電磁波會(huì)在導(dǎo)體中感應(yīng)出電壓信號(hào),影響回路中的元器件,而在數(shù)字電路中國(guó),由于關(guān)鍵位置的干擾,器件容易產(chǎn)生錯(cuò)誤信號(hào),從而引起錯(cuò)誤的動(dòng)作。

去耦電容可以減少上述情況,去耦電容一般放置在元器件的電源處,以減少布線(xiàn)阻抗對(duì)濾波效果的影響,大多數(shù)去耦電容都是陶瓷電容,其值的電壓信號(hào)最快的上升和下降速度決定。

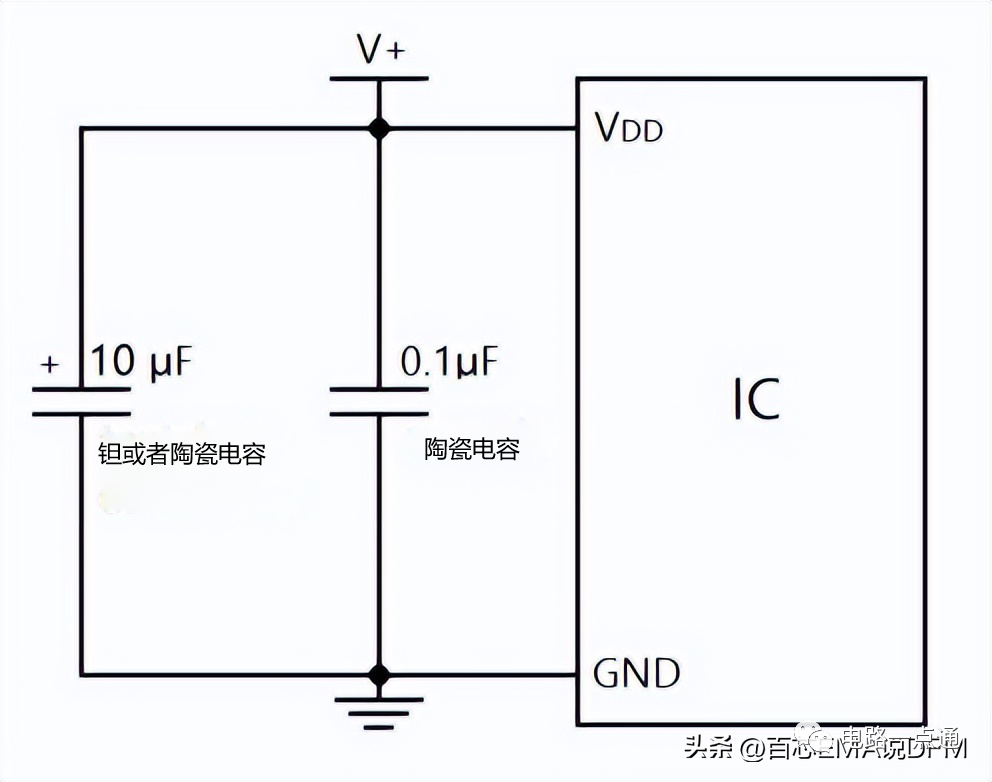

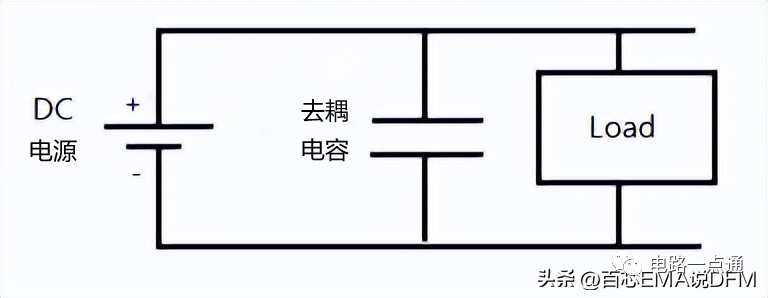

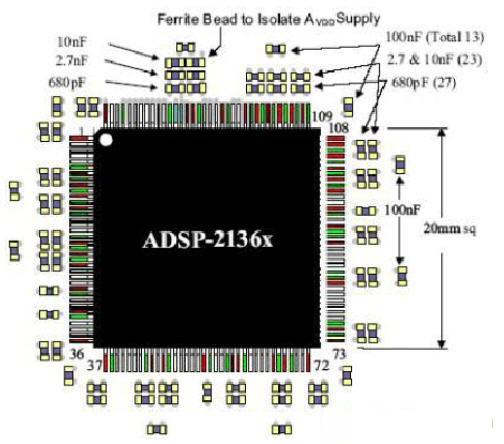

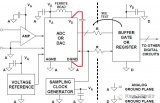

在IC旁邊使用去耦電容的典型應(yīng)用

二、去耦電容的作用

1、去除高頻

去耦電容主要用于去除通過(guò)電磁輻射進(jìn)入設(shè)備的射頻信號(hào)等高頻干擾。

芯片附近的電容也儲(chǔ)能作用。假設(shè)主電源是水庫(kù),我們樓里的每戶(hù)人家都需要供水,水不是直接從水庫(kù)里面來(lái)的,因?yàn)樘h(yuǎn)了,要很久。實(shí)際上的水都是來(lái)自附近儲(chǔ)存的水的分塔,可以起到一個(gè)緩沖作用。

從微觀上看,高頻器件工作時(shí),其電流是不連續(xù)的,頻率很高,器件VCC與主電源之間有一定的距離。

在高頻下,阻抗Z為:

阻抗

而且線(xiàn)路的電感也會(huì)很大,不能及時(shí)給設(shè)備供電。去耦電容可以彌補(bǔ)這一點(diǎn)不足,這也就是為什么PCB板上高頻器件的VCC引腳上放置很多小電容的原因之一。

2、為有源器件提供直流電源

當(dāng)有源器件打開(kāi)和關(guān)閉時(shí),會(huì)產(chǎn)生高頻噪聲并沿電源線(xiàn)傳輸。去耦電容的主要作用是為有源器件提供本地直流電源,以減少PCB板上開(kāi)關(guān)噪聲的傳播,并將噪聲引至地。

三、去耦電容計(jì)算

去耦的最初目的:無(wú)論法規(guī)和電流波動(dòng)的要求如何,都將電壓限制保持在規(guī)定的允許誤差內(nèi)。

1、計(jì)算方式一

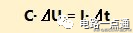

IC所需要的去耦電容的電容值C可由以下公式計(jì)算:

去耦電容容值

⊿U 為實(shí)際電源母線(xiàn)電壓的允許降低量(V);

I 為最大所需電流(A);

⊿t 是所需電容的持續(xù)時(shí)間。

2、計(jì)算方法二

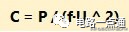

建議去耦電容或者值大于等效開(kāi)路電容的1/m倍。m 是 IC 電源引腳上允許的電源總線(xiàn)電壓變化的最大百分比,通常會(huì)在 IC 數(shù)據(jù)表中給出。下面為等效開(kāi)路電容:

等效開(kāi)路電容

P:IC耗散的總瓦數(shù)

U:IC的最大直流供電電壓

f:IC的時(shí)鐘頻率

確定等效開(kāi)路電容后,將其乘以1/m即可得出 IC 所需的總?cè)ヱ铍娙莼蛑怠H缓髮⒔Y(jié)果除以連接到同一電源總線(xiàn)的電源引腳總數(shù),最后得到連接到每條電源總線(xiàn)的所有電源引腳附近的電容值。

三、PCB去耦電容的選擇與布局

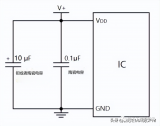

去耦電容并不是越多越好,要注意濾波效果。在設(shè)計(jì)PCB時(shí),在電源輸入端跨接一個(gè)10uf-100uf的電解電容,在每個(gè)集成芯片的電源和地之間配置一個(gè)0.01μF的陶瓷電容。

一方面, 去耦電容提供和吸收集成電路開(kāi)合時(shí)的瞬時(shí)充放電能量,另一方面,繞過(guò)了設(shè)備的高頻噪聲。

1、去耦電容的分類(lèi)

去耦電容對(duì)集成芯片進(jìn)行補(bǔ)償或者PCB工作電壓出現(xiàn)下降時(shí),可以起到儲(chǔ)能作用。可以分為整體型,局部型和板間型三種。

1)整體去耦電容

整體去耦電容工作在低頻(<1MHz)范圍,為整個(gè)PCB提供一個(gè)電流源,以補(bǔ)償PCB在工作過(guò)程中產(chǎn)生的噪聲電流ΔI,保證工作電源的穩(wěn)定。整體去耦電容是PCB上所有負(fù)載電容總和50倍到100倍。

一般來(lái)說(shuō),整體去耦電容應(yīng)該靠近PCB的電源延長(zhǎng)線(xiàn)和地線(xiàn)放置,印刷制線(xiàn)密度很高。為PCB上放置關(guān)鍵印刷線(xiàn)路提供了空間,而不會(huì)減少低頻去耦。

2)局部去耦

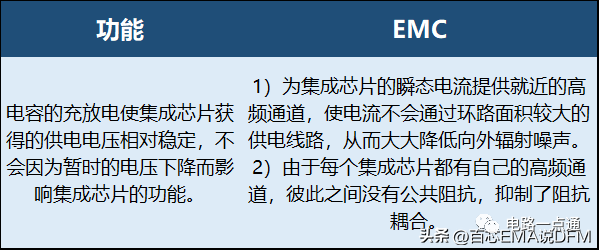

局部去耦有2個(gè)原因:1是因?yàn)楣δ芊矫妫?是因?yàn)?a target="_blank">EMC方面,具體的如下所示:

局部去耦原因

局部去耦電容安裝在集成芯片的電源端和地端之間,并盡可能靠近集成芯片。

3)板間去耦電容S

板間去耦電容指電源層和地層之間的電容,是高頻去耦電流的主要來(lái)源,可以通過(guò)增加電源層和接地層之間的面積來(lái)增加平面之間的電容。

在PCB中,一些平面可以分布到電源平面,移除這些接地平面并用電源隔離區(qū)域替換它們會(huì)增加平面之間的電容。

2、PCB去耦電容值

在直流電源電路中,負(fù)載的變化會(huì)產(chǎn)生電源噪聲,例如在數(shù)字電路中,當(dāng)電路從一種狀態(tài)轉(zhuǎn)換到另一種狀態(tài)時(shí),電源線(xiàn)上會(huì)產(chǎn)生很大的峰值電流,形成瞬態(tài)噪聲電壓。

配置去耦電容可以抑制負(fù)載變化引起的噪聲,在PCB可靠性設(shè)計(jì)經(jīng)常會(huì)用這個(gè)方法,一個(gè)好的高頻去耦電容可以去除高達(dá)1GHz的高頻成分。陶瓷貼片電容或者多層陶瓷電容的高頻特性較好。

在設(shè)計(jì)PCB時(shí),必須要在每塊集成電路的電源和地之間添加一個(gè)去耦電容。去耦電容有2個(gè)作用,一方面是集成電路的儲(chǔ)能電容,提供和吸收集成電路開(kāi)、關(guān)時(shí)的瞬時(shí)充放電能量。另一方面,去耦電容繞過(guò)了設(shè)備的高頻噪聲。

PCB去耦電容

去耦電容的配置原則如下:

1)電源配置濾波電容

電源輸入端跨接一個(gè) 10μF ~ 100μF 的電解電容,如果PCB的位置允許的話(huà),這個(gè)電解電容的抗干擾效果會(huì)更好。

并聯(lián)諧振頻率在2020MHz以上的1μF和10μF電容,去除高頻噪聲效果較好。在電源進(jìn)入PCB的區(qū)域應(yīng)用,應(yīng)用電容通常是有利的,而且通常電池供電系統(tǒng)也是需要這種電容。

2)芯片配置去耦電容

每個(gè)集成電路芯片配置一個(gè)0.01μF陶瓷電容。數(shù)字電容中典型的去耦電容為 0.1/μF。去耦電容具有 5nH的分布電感 ,其并聯(lián)諧振頻率在7MHz左右,意味著對(duì)10MHz以下的噪聲有很好的去耦效果,對(duì)40MHz以上的噪聲影響不大。

如果PCB的空間太小,可以每4~10個(gè)芯片加一個(gè)1μF~10μF的鉭電解電容。這種電容的高頻阻抗特別小,在500kHz-20MHz范圍內(nèi)小于1μF-10μF,漏電流很小(0.5μA以下)。

去耦電容的選值并沒(méi)有那么嚴(yán)格,可以用以下公式來(lái)計(jì)算:

去耦電容

對(duì)于單片機(jī)組成的系統(tǒng),電容可以在在0.1μF - 0.01μF之間。

3)充放電電容S

每10個(gè)左右的集成電路需要加一個(gè)容量為10uf的充放電電容,通常使用的大電容是電解電容。但是當(dāng)濾波頻率較高時(shí),電解電容會(huì)卷起2層薄膜,卷起的結(jié)構(gòu)在高頻時(shí)表現(xiàn)為電感。在這種情況下,使用鉭電容或者聚碳酸酯電容。

四、PCB去耦電容布局的影響因素

1、電容引線(xiàn)的影響

在使用電容抑制電磁干擾和濾波時(shí),最容易被忽視的問(wèn)題是電容引線(xiàn)濾波效果的影響。

電容的容抗與頻率成反比,基于這一特點(diǎn),在信號(hào)線(xiàn)和地線(xiàn)之間并聯(lián)電容,起到旁路高頻噪聲的作用,然后在實(shí)際電路中,有很多人發(fā)現(xiàn)這種方法并沒(méi)有達(dá)到預(yù)期的濾除噪聲和效果。原因之一就是忽略了電容引線(xiàn)對(duì)旁別效應(yīng)的影響。

實(shí)際的電容式由等效串聯(lián)電感(ESL)、電容和等效串聯(lián)電容(ESR)組成的串聯(lián)網(wǎng)絡(luò)。

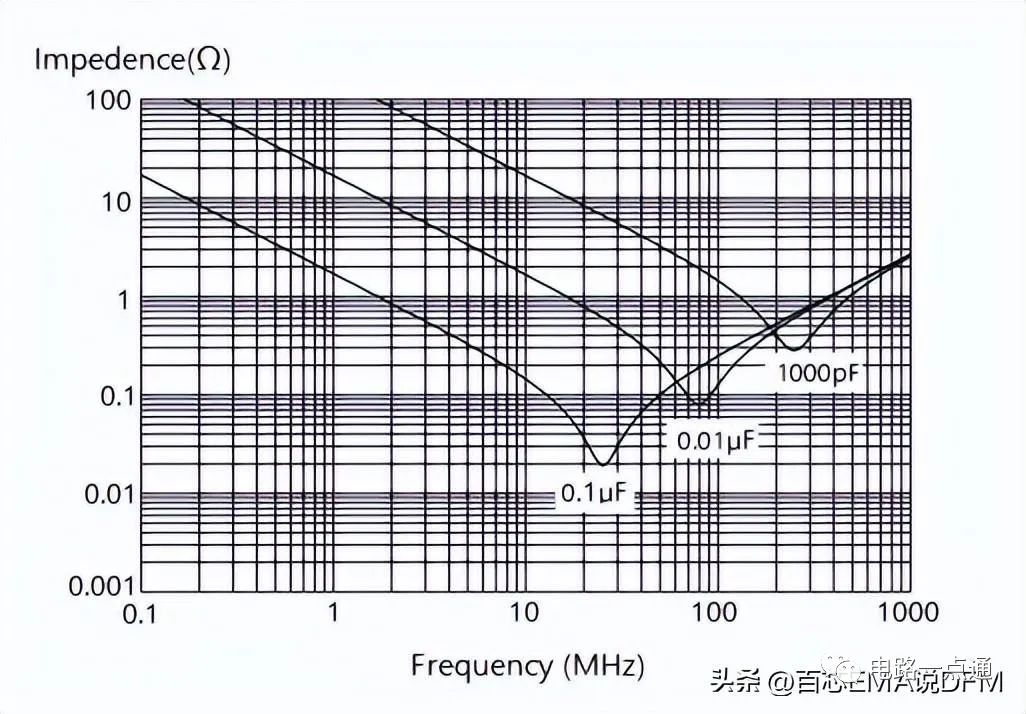

理想電容的阻抗隨著頻率的升高而降低,實(shí)際電容的阻抗特性如下圖所示:

實(shí)際電容的阻抗特性

當(dāng)頻率較低時(shí),表現(xiàn)出電容特性,即阻抗隨頻率升高而降低,在某一點(diǎn)發(fā)生諧振,電容的阻抗等于ESR。在諧振動(dòng)以上,由于ESL的作用,電容的阻抗隨頻率的升高而增大,使電容表現(xiàn)出電感的阻抗特性。隨著電容阻抗的增加,對(duì)高頻噪聲的旁路作用減弱甚至消失。

因此,在布置去耦電容時(shí),要注意電容的分布參數(shù)對(duì)濾波的影響。

2、電容引線(xiàn)的作用

電容的諧振頻率由ESL和C共同決定,電容或者電感較大,諧振頻率越低,意味著,電容的高頻濾波效果越差。

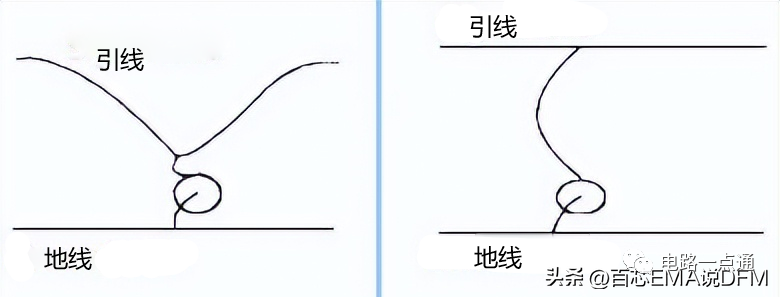

除了電容的種類(lèi),引線(xiàn)的長(zhǎng)度也是ESL非常重要的一個(gè)參數(shù)。引線(xiàn)越長(zhǎng),電感越大,電容的諧振頻率越低。因此在實(shí)際設(shè)計(jì)中,電容的引線(xiàn)應(yīng)該盡可能短。電容的正確安裝方法和不正確的安裝方法如下圖所示:

濾波電容的安裝方法

根據(jù)LC電容串聯(lián)諧振原理,諧振點(diǎn)不僅與電感有關(guān),還與電容值有關(guān),電容越大,諧振點(diǎn)越低。

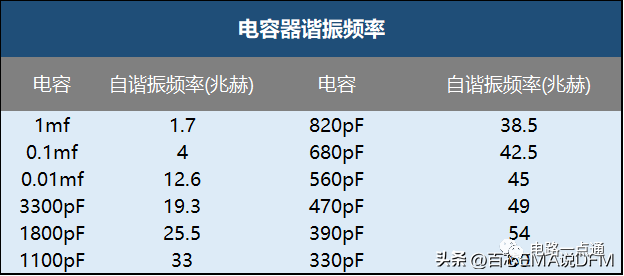

有些人會(huì)認(rèn)為電容越大,濾波效果也會(huì)越好,這是一種誤解,雖然電容越大,低頻干擾的旁路效果越好,但由于電容諧振頻率較低,隨著頻率的升高阻抗開(kāi)始增大,高頻噪聲的旁路效果變差,表中給出了不同容量陶瓷電容的自諧振頻率,電容的引線(xiàn)長(zhǎng)度為1.6mm。

雖然從濾波高頻噪聲的角度來(lái)看,電容的諧振是不可取的,但也有好的一方面,當(dāng)待濾除噪聲的頻率確定后,可調(diào)節(jié)電容使諧振點(diǎn)剛好落在干擾頻率。

3、溫度的影響

溫度對(duì)電容的特性也有很大的影響。由于電容中的介質(zhì)參數(shù)受溫度變化的影響,因此電容的容值值也隨溫度變化。不同的介質(zhì)有不同的溫度變化規(guī)律,有的電容在溫度升高時(shí)電容量會(huì)下降70%以上。

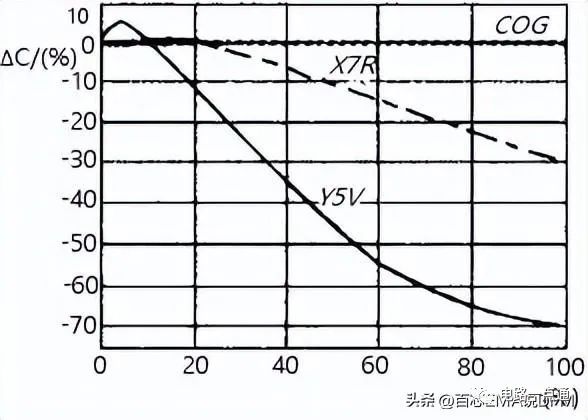

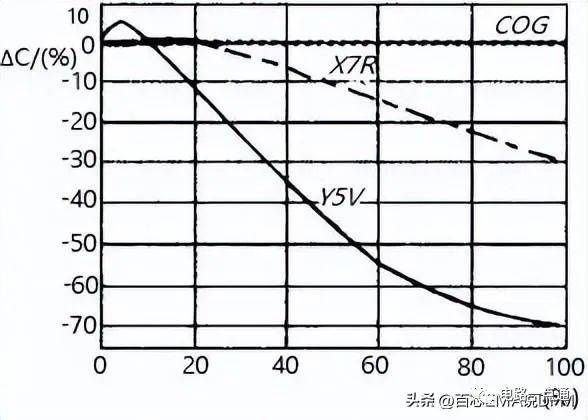

常用的濾波電容是陶瓷電容。陶瓷電容分為超穩(wěn)型、穩(wěn)定型和通用型三種。不同電介質(zhì)電容的溫度特性如圖所示。

不同介質(zhì)電容的溫度特性

可以看出, COG電容的電容量幾乎不隨溫度變化。X7R電容在額定工作溫度范圍內(nèi)的容量變化在12%以?xún)?nèi), YSV電容在額定工作溫度范圍內(nèi) 的容量 變化在70%以上。

溫度特性都是我們應(yīng)該注意的,否則濾波器在高溫或者低溫下的性能會(huì)發(fā)生變化,從而導(dǎo)致電磁兼容問(wèn)題。

COG介質(zhì)電容雖然受溫度影響較小,特性穩(wěn)定,但其介電常數(shù)較低,一般為10~100,所以體積小時(shí),電容量也會(huì)小。

XTR 介質(zhì)電容的介電常數(shù)要高得多,從 2000 到 4000,因此更小的體積可以產(chǎn)生更大的電容

YSV介質(zhì)電容的介電常數(shù)最高,為5000-25000,通常用于需要體積較小、電容量較大的場(chǎng)合。

在選擇電容時(shí),很多人單方面追求電容的體積小。這種電容雖然介電常數(shù)高,但溫度穩(wěn)定性很差,會(huì)導(dǎo)致器件的溫度特性較差。這是我們?cè)谶x擇電容時(shí)要特別注意的,特別是軍用裝備。

4、PCB電壓的影響

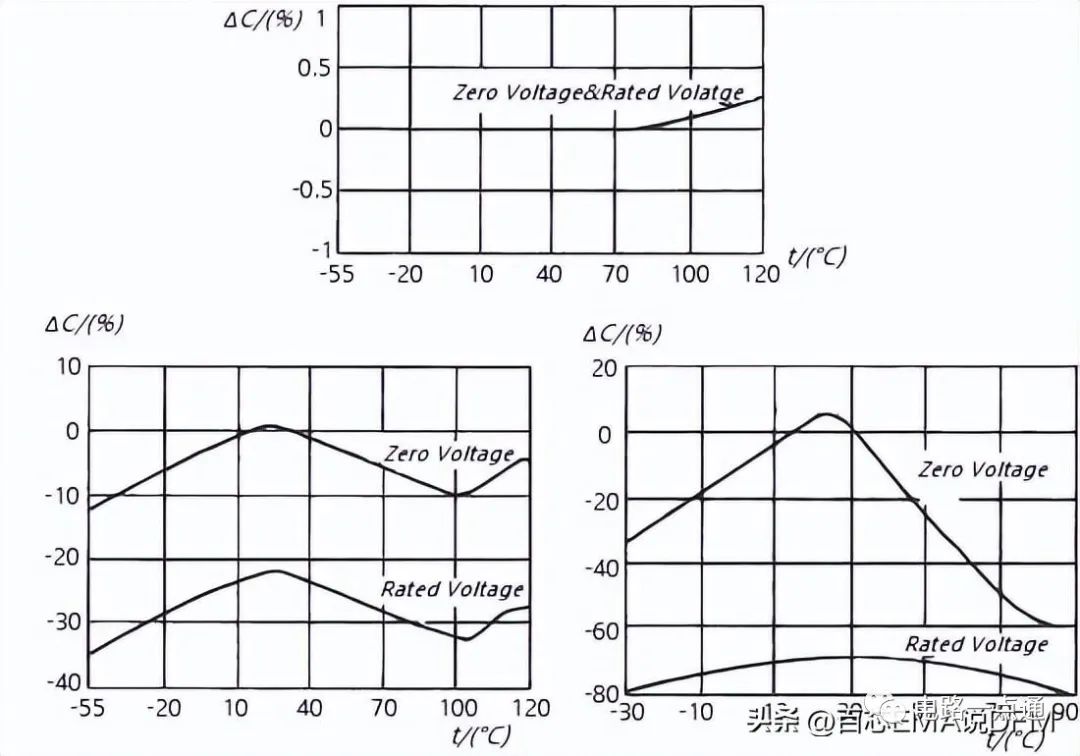

電容的容量不僅隨溫度而變化,而且隨工作電壓而變化。在實(shí)際項(xiàng)目中必須注意這一點(diǎn)。

下圖顯示了不同介質(zhì)材料的電容的電壓特性。圖中,在額定電壓下,X7R電容的容量減少到原來(lái)的70%,YSV電容的容量減少到原來(lái)的30%。因此,在選擇電容時(shí),電壓和電容值要留有余量,否則濾波器在額定工作電壓下達(dá)不到預(yù)期效果。

當(dāng)同時(shí)考慮溫度和電壓的影響時(shí),電容的變化如圖所示。

電容器的電壓特性

因此,我們?cè)诜胖脼V波電容時(shí)必須充分考慮電容的濾波作用。

電容的溫度/電壓特性

五、 PCB去耦電容的合理放置

1、原理圖中一般只畫(huà)出幾個(gè)電源去耦電容,但并沒(méi)有標(biāo)明應(yīng)該接在哪里。實(shí)際上,這些電容是為開(kāi)關(guān)器件(門(mén)電路)或其他需要去耦的元器件而設(shè)置的,因此應(yīng)盡可能靠近這些元器件放置。當(dāng)電源去耦電容布置得當(dāng),接地點(diǎn)問(wèn)題就不那么明顯了。

2、對(duì)于抗噪聲能力弱、掉電時(shí)電流變化大的器件和ROM、RAM等存儲(chǔ)器件,應(yīng)在芯片電源線(xiàn)(VCC)和地(GND)之間直接接去耦電容。

3、去耦電容的引線(xiàn)不宜過(guò)長(zhǎng)。引線(xiàn)越短,去耦效果越好。特別是高頻旁路電容不能有引線(xiàn)。

4、去耦的量并不是越多越好,而是要注意濾波的效果,根據(jù)電路板和器件的時(shí)間來(lái)選擇電容的數(shù)量和大小。

5、陶瓷電容和電解電容電容精度差,分布電感大,對(duì)去耦要求較高時(shí)不采用。相反,應(yīng)使用鉭電容器或聚酯電容。

6、在芯片和去耦電容較多的地方,可加裝充放電電容,以處理電路開(kāi)關(guān)工作時(shí)產(chǎn)生的電荷。

審核編輯:湯梓紅

-

電容器

+關(guān)注

關(guān)注

64文章

6709瀏覽量

102915 -

pcb

+關(guān)注

關(guān)注

4368文章

23489瀏覽量

409663 -

元器件

+關(guān)注

關(guān)注

113文章

4834瀏覽量

95134 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4801瀏覽量

90422 -

去耦電容

+關(guān)注

關(guān)注

11文章

319瀏覽量

22949

原文標(biāo)題:五、 PCB去耦電容的合理放置

文章出處:【微信號(hào):電路一點(diǎn)通,微信公眾號(hào):電路一點(diǎn)通】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

PCB布局時(shí)去耦電容擺放經(jīng)驗(yàn)分享

去耦電容的選擇、容值計(jì)算和pcb布局布線(xiàn)詳解

20180223-PCB布局時(shí)如何擺放及安裝去耦電容?

PCB布局時(shí)去耦電容擺放經(jīng)驗(yàn)分享

什么是去耦電容?為什么要去耦?去耦電容的PCB布局布線(xiàn)設(shè)計(jì)

去耦電容PCB設(shè)計(jì)和布局

去耦電容PCB設(shè)計(jì)和布局

評(píng)論