高速先生成員--姜杰

大家都知道,信號(hào)的最佳回流路徑是GND:對于走線而言,我們希望能參考GND平面;對于信號(hào)管腳,我們希望GND管腳伴隨;對于BGA區(qū)域的高速信號(hào)扇出過孔,我們希望能被相鄰的GND過孔包圍。

因此,經(jīng)驗(yàn)豐富的攻城獅一定會(huì)避免讓高速差分信號(hào)置于如下的境地:BGA區(qū)域差分信號(hào)管腳的四周分布多個(gè)電源管腳(圖中白色對應(yīng)差分信號(hào),綠色是GND網(wǎng)絡(luò),黃色是電源PWR網(wǎng)絡(luò)),不多不少,一邊一個(gè)。

理想很豐滿,現(xiàn)實(shí)卻很骨感,上圖的這種情況偏偏是存在的,更要命的是,電源管腳還不能換成GND網(wǎng)絡(luò)。

當(dāng)硬件攻城獅對換PIN方案表示無能為力的時(shí)候,Layout攻城獅把求助的眼光投向了高速先生,高速先生則默默的看向本文的標(biāo)題:如何用電源去耦電容改善高速信號(hào)質(zhì)量?

沒錯(cuò),高速先生做過類似的案例。

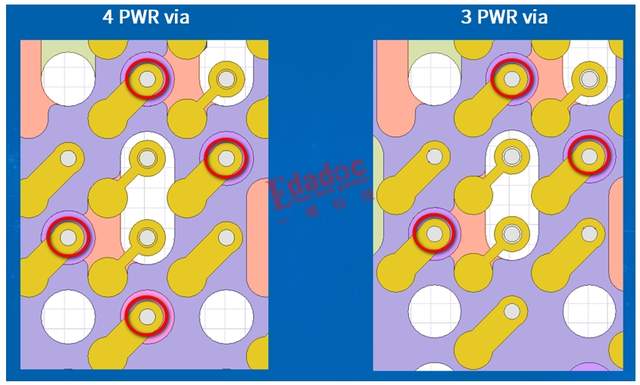

如前所述,我們的Layout攻城獅經(jīng)驗(yàn)豐富,在他的努力下,找到了另外一個(gè)對比模型,信號(hào)管腳周圍只分布了3個(gè)電源管腳(下圖中的紅色圓圈)的情況。

為了高速先生仿真對比,Layout攻城獅也是非常的貼心了。

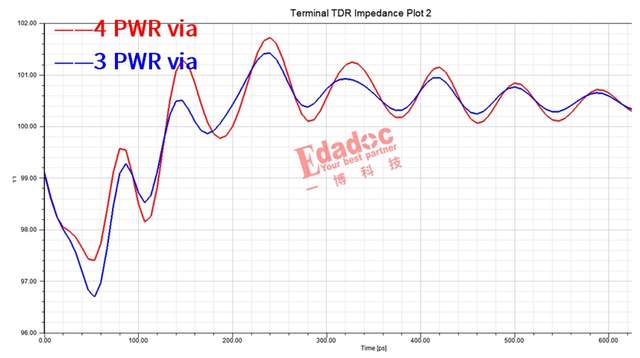

先仿真沒有電容的情況。這個(gè)時(shí)候,對于走線特征阻抗100歐姆的差分信號(hào),過孔阻抗是這樣的:

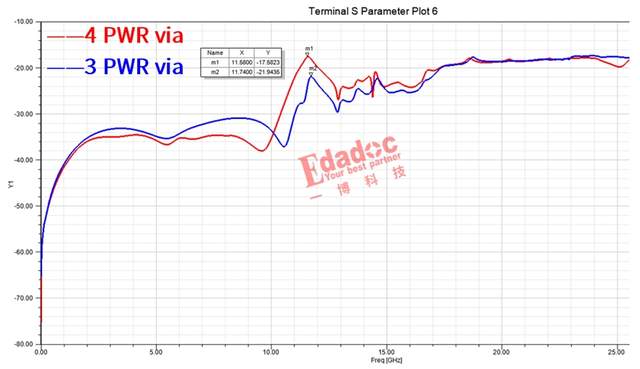

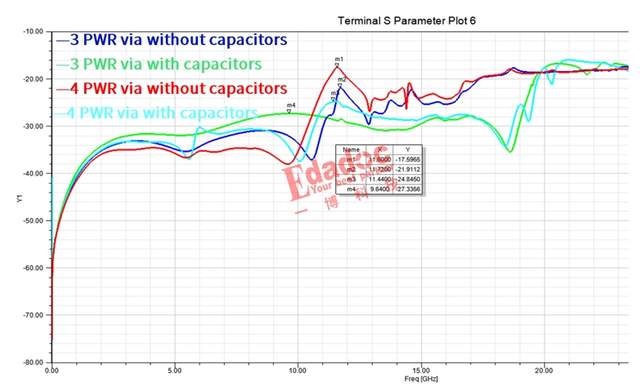

阻抗曲線甚至出現(xiàn)了振蕩。換個(gè)角度,對比衡量阻抗連續(xù)性的另外一個(gè)參數(shù),回波損耗。對于本案例中的100GBASE-KR4信號(hào),在基頻12.9GHz以內(nèi)的頻段,4個(gè)電源孔情況下的最大回?fù)p-17.5dB,3個(gè)電源孔情況下的最大回?fù)p-21.9dB。

通過對比可以發(fā)現(xiàn),回流地孔的增加確實(shí)改善了差分過孔的阻抗,回?fù)p也反映了同樣的趨勢。問題在于,無論是3個(gè)電源孔還是4個(gè)電源孔,結(jié)果都不太理想。

一直關(guān)注高速先生的朋友,一定還記得前不久的一篇文章《瞧不起誰啊!“縫合電容”我怎么可能不知道》,此時(shí)會(huì)不會(huì)突發(fā)靈感:同樣是電容,電源去耦電容該不會(huì)對改善高速信號(hào)質(zhì)量有幫助吧?

試試看。

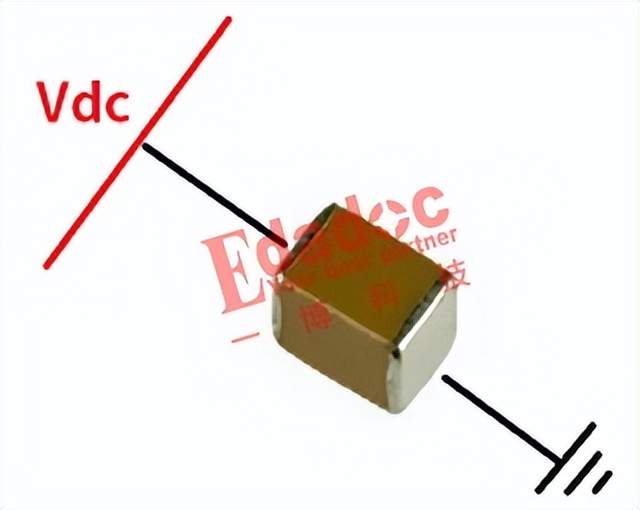

每個(gè)電源管腳加上本就屬于它的去耦電容,像下圖這樣(當(dāng)然了,BGA和電容位于PCB不同的布局面,本視圖是為了大家更清楚的看到二者的相對位置)。

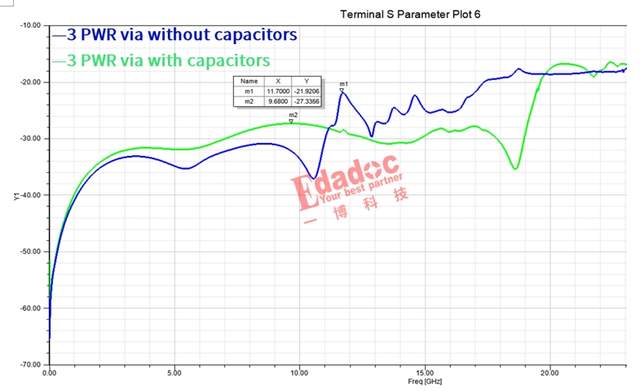

增加電容前后,3個(gè)電源過孔情況的回?fù)p對比如下,在關(guān)注頻段內(nèi),增加電容后的最大回?fù)p有較大改善。

同樣的, 4個(gè)相鄰電源過孔的差分過孔回?fù)p也改善了不少。整體對比情況如下圖。

電源去耦電容本來是為了減小電源噪聲,沒想到還能順帶改善信號(hào)質(zhì)量,這到底是為什么呢?

問題來了

本案例中的電源去耦電容改善信號(hào)質(zhì)量的原理是什么?

審核編輯 黃宇

-

仿真

+關(guān)注

關(guān)注

51文章

4234瀏覽量

135281 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4775瀏覽量

89105 -

去耦電容

+關(guān)注

關(guān)注

11文章

319瀏覽量

22798 -

GND

+關(guān)注

關(guān)注

2文章

544瀏覽量

39465

發(fā)布評論請先 登錄

高速PBC設(shè)計(jì)中揭秘DC-BIAS效應(yīng):電容“縮水”對電源噪聲的影響

高速PCB設(shè)計(jì)中揭秘DC-BIAS效應(yīng):電容“縮水”對電源噪聲的影響

PCB設(shè)計(jì)仿真,“縫合電容”我怎么可能不知道

面試常考:為什么芯片電源引腳的去耦電容一般選100nF?

干貨推薦!去耦電容的基本知識(shí)

深度解析:PCB高速信號(hào)傳輸中的阻抗匹配與信號(hào)完整性

高速PCB設(shè)計(jì)EMI防控手冊:九大關(guān)鍵步驟詳解

高速PCB設(shè)計(jì)指南

PCB設(shè)計(jì)如何用電源去耦電容改善高速信號(hào)質(zhì)量

PCB設(shè)計(jì)如何用電源去耦電容改善高速信號(hào)質(zhì)量

評論