去耦電容的應(yīng)用的非常廣泛,在電路應(yīng)用過程中對于去耦電容的容值計算和PCB電路布局布線有一些我們必須要了解的技巧。

有源器件在開關(guān)時產(chǎn)生的高頻開關(guān)噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個局部的直流電源給有源器件,以減少開關(guān)噪聲在板上的傳播,和將噪聲引導(dǎo)到地。

去耦電容的容值計算

去耦的初衷是:不論IC對電流波動的規(guī)定和要求如何都要使電壓限值維持在規(guī)定的允許誤差范圍之內(nèi)。 使用表達(dá)式:

C⊿U=I⊿t

由此可計算出一個IC所要求的去耦電容的電容量C。

⊿U是實(shí)際電源總線電壓所允許的降低,單位為V。

I是以A(安培)為單位的最大要求電流;

⊿t是這個要求所維持的時間。

去耦電容容值計算方法: 推薦使用遠(yuǎn)大于1/m乘以等效開路電容的電容值。

此處m是在IC的電源插針上所允許的電源總線電壓變化的最大百分?jǐn)?shù),一般IC的數(shù)據(jù)手冊都會給出具體的參數(shù)值。

等效開路電容定義為:

C=P/(fU^2) 式中:

P——IC所耗散的總瓦數(shù);

U——IC的最大DC供電電壓;

f——IC的時鐘頻率。

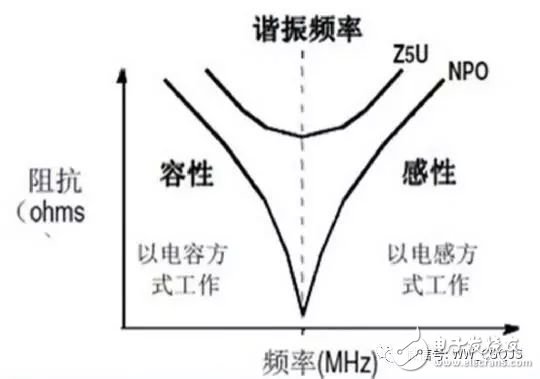

電容的容值選擇一般取決于電容的諧振頻率。

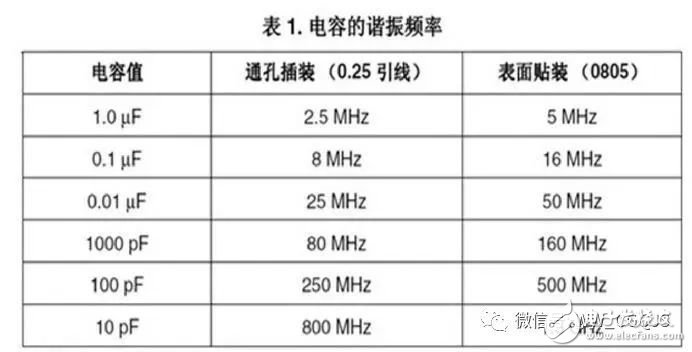

不同封裝的電容有不同的諧振頻率,下表列出了不同容值不同封裝的電容的諧振頻率:

需要注意的是數(shù)字電路的去耦,低的ESR值比諧振頻率更為重要,因為低的ESR值可以提供更低阻抗的到地通路,這樣當(dāng)超過諧振頻率 的電容呈現(xiàn)感性時仍能提供足夠的去耦能力。

降低去耦電容ESL的方法

去耦電容的ESL是由于內(nèi)部流動的電流引起的,使用多個去耦電容并聯(lián)的方式可以降低電容的ESL影響,而且將兩個去耦電容以相反走向放置在一起,從 而使它們的內(nèi)部電流引起的磁通量相互抵消,能進(jìn)一步降低ESL。(此方法適用于任何數(shù)目的去耦電容,注意不要侵犯DELL公司的專利)

IC去耦電容的數(shù)目選擇

在設(shè)計原理圖的時候,經(jīng)常遇到的問題是為芯片的電源引腳設(shè)計去耦電容,上面已經(jīng)介紹了去耦電容的容值選擇,但是數(shù)目選擇怎么確定呢?理論上是每個電 源引腳最好分配一個去耦電容,但https://mp.weixin.qq.com/cgi-bin/appmsg?t=media/appmsg_edit&action=edit&type=10&isMul=1&isNew=1&lang=zh_CN&token=1045897676是在實(shí)際情況中,卻經(jīng)常看到去耦電容的數(shù)目要少于電源引腳數(shù)目的情況,如freescale提供的iMX233的PDK原 理圖中,內(nèi)存SDRAM有15個電源引腳,但是去耦電容的數(shù)目是10個。

去耦電容數(shù)目選擇依據(jù)

在布局空間允許的情況下,最好做到一個電源引腳分配一個去耦電容,但是在空間不足的時候,可以適當(dāng)削減電容的數(shù)目,具體情況應(yīng)該根據(jù)芯片上電源引腳 的具體分布決定,因為廠家在設(shè)計IC的時候,經(jīng)常是幾個電源引腳在一起,這樣可以共用去耦電容,減少去耦電容的數(shù)目。

電容的安裝方法 電容的擺放

對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍 遠(yuǎn),最外層放置容值最大的。但是,所有對該芯片去耦的電容都盡量靠近芯片。另外的一個原因是:如果去耦電容離IC電源引腳較遠(yuǎn),則布線阻抗將減小去耦電容 的效力。

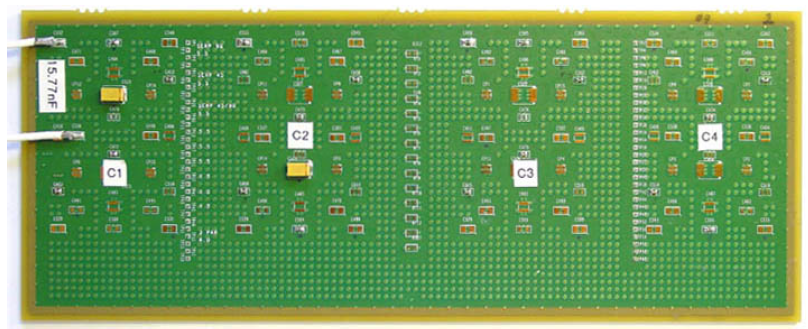

還有一點(diǎn)要注意,在放置時,最好均勻分布在芯片的四周,對每一個容值等級都要這樣。通常芯片在設(shè)計的時候就考慮到了電源和地引腳的排列位置,一般都 是均勻分布在芯片的四個邊上的。因此,電壓擾動在芯片的四周都存在,去耦也必須對整個芯片所在區(qū)域均勻去耦。

電容的安裝

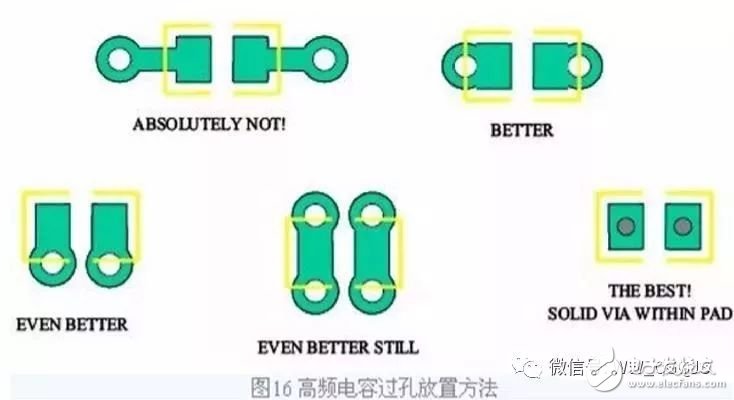

在安裝電容時,要從焊盤拉出一小段引出線,然后通過過孔和電源平面連接,接地端也是同樣。放置過孔的基本原則就是讓這一環(huán)路面積最小,進(jìn)而使總的寄 生電感最小。圖16顯示了幾種過孔放置方法。

第一種方法從焊盤引出很長的引出線然后連接過孔,這會引入很大的寄生電感,一定要避免這樣做,這時最糟糕的安裝方式。

第二種方法在焊盤的兩個端點(diǎn)緊鄰焊盤打孔,比第一種方法路面積小得多,寄生電感也較小,可以接受。

第三種在焊盤側(cè)面打孔,進(jìn)一步減小了回路面積,寄生電感比第二種更小,是比較好的方法。

第四種在焊盤兩側(cè)都打孔,和第三種方法相比,相當(dāng)于電容每一端都是通過過孔的并聯(lián)接入電源平面和地平面,比第三種寄生電感更小,只要空間允許,盡量 用這種方法。

最后一種方法在焊盤上直接打孔,寄生電感最小,但是焊接是可能會出現(xiàn)問題,是否使用要看加工能力和方式。 推薦使用第三種和第四種方法。

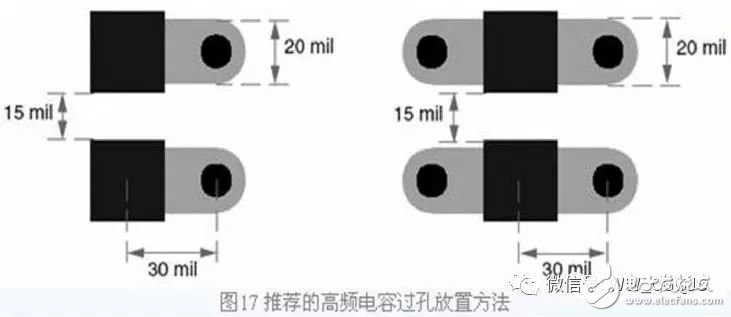

需要強(qiáng)調(diào)一點(diǎn):有些工程師為了節(jié)省空間,有時讓多個電容使用公共過孔。任何情況下都不要這樣做。最好想辦法優(yōu)化電容組合的設(shè)計,減少電容數(shù)量。 由于印制線越寬,電感越小,從焊盤到過孔的引出線盡量加寬,如果可能,盡量和焊盤寬度相同。這樣即使是0402封裝的電容,你也可以使用20mil 寬的引出線。引出線和過孔安裝如圖17所示,注意圖中的各種尺寸。

對于大尺寸的電容,比如板級濾波所用的鉭電容,推薦用圖18中的安裝方法。注意:小尺寸電容禁止在兩個焊盤間打孔,因為容易引起短 路。

電容的去耦半徑

對于大尺寸的電容,比如板級濾波所用的鉭電容,推薦用圖18中的安裝方法。注意:小尺寸電容禁止在兩個焊盤間打孔,因為容易引起短路。

電容的去耦半徑

電容去耦的一個重要問題是電容的去耦半徑。大多數(shù)資料中都會提到電容擺放要盡量靠近芯片,多數(shù)資料都是從減小回路電感的角度來談這個擺放距離問題。 確實(shí),減小電感是一個重要原因,但是還有一個重要的原因大多數(shù)資料都沒有提及,那就是電容去耦半徑問題。如果電容擺放離芯片過遠(yuǎn),超出了它的去耦半徑,電 容將失去它的去耦的作用。

理解去耦半徑最好的辦法就是考察噪聲源和電容補(bǔ)償電流之間的相位關(guān)系。當(dāng)芯片對電流的需求發(fā)生變化時,會在電源平面的一個很小的局部區(qū)域內(nèi)產(chǎn)生電壓 擾動,電容要補(bǔ)償這一電流(或電壓),就必須先感知到這個電壓擾動。信號在介質(zhì)中傳播需要一定的時間,因此從發(fā)生局部電壓擾動到電容感知到這一擾動之間有 一個時間延遲。同樣,電容的補(bǔ)償電流到達(dá)擾動區(qū)也需要一個延遲。因此必然造成噪聲源和電容補(bǔ)償電流之間的相位上的不一致。

特定的電容,對與它自諧振頻率相同的噪聲補(bǔ)償效果最好,我們以這個頻率來衡量這種相位關(guān)系。設(shè)自諧振頻率為f,對應(yīng)波長為λ,補(bǔ)償電流表達(dá)式可寫 為:

其中,A是電流幅度,R為需要補(bǔ)償?shù)膮^(qū)域到電容的距離,C為信號傳播速度。 當(dāng)擾動區(qū)到電容的距離達(dá)到λ/4時,補(bǔ)償電流的相位為π,和噪聲源相位剛好差180度,即完全反相。此時補(bǔ)償電流不再起作用,去耦作用失效,補(bǔ)償?shù)?能量無法及時送達(dá)。為了能有效傳遞補(bǔ)償能量,應(yīng)使噪聲源和補(bǔ)償電流的相位差盡可能的小,最好是同相位的。距離越近,相位差越小,補(bǔ)償能量傳遞越多,如果距 離為0,則補(bǔ)償能量百分之百傳遞到擾動區(qū)。這就要求噪聲源距離電容盡可能的近,要遠(yuǎn)小于λ/4。實(shí)際應(yīng)用中,這一距離最好控制在λ/40-λ/50之間, 這是一個經(jīng)驗數(shù)據(jù)。

例如:0.001uF陶瓷電容,如果安裝到電路板上后總的寄生電感為1.6nH,那么其安裝后的諧振頻率為125.8MHz,諧振周期為 7.95ps。假設(shè)信號在電路板上的傳播速度為166ps/inch,則波長為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于 2.4厘米。 本例中的電容只能對它周圍2.4厘米范圍內(nèi)的電源噪聲進(jìn)行補(bǔ)償,即它的去耦半徑2.4厘米。不同的電容,諧振頻率不同,去耦半徑也不同。對于大電 容,因為其諧振頻率很低,對應(yīng)的波長非常長,因而去耦半徑很大,這也是為什么我們不太關(guān)注大電容在電路板上放置位置的原因。對于小電容,因去耦半徑很小, 應(yīng)盡可能的靠近需要去耦的芯片,這正是大多數(shù)資料上都會反復(fù)強(qiáng)調(diào)的,小電容要盡可能近的靠近芯片放置。

綜上所述,在選擇去耦電容時,需要考慮的因素有電容的ESR、ESL值,諧振頻率,布局時要注意根據(jù)IC電源引腳的數(shù)目和周圍布局 空間決定去耦電容數(shù)目,根據(jù)去耦半徑?jīng)Q定具體的布局位置。

-

pcb

+關(guān)注

關(guān)注

4349文章

23392瀏覽量

406220 -

電容

+關(guān)注

關(guān)注

100文章

6186瀏覽量

153070 -

去耦電容

+關(guān)注

關(guān)注

11文章

319瀏覽量

22783

原文標(biāo)題:巴鐵和中國關(guān)系到底有多鐵?

文章出處:【微信號:UCAS2004,微信公眾號:國科環(huán)宇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

解決噪聲問題試試從PCB布局布線入手

電解電容的容值范圍與電壓等級解析

干貨推薦!去耦電容的基本知識

去耦電容的基本知識

去耦電容的選擇、容值計算和pcb布局布線詳解

去耦電容的選擇、容值計算和pcb布局布線詳解

評論