IO約束在頂層和模塊級的主要命令都是以下幾個(gè),但是實(shí)際應(yīng)用的復(fù)雜程度不可同日而語,本篇會先介紹模塊級IO約束實(shí)戰(zhàn)經(jīng)驗(yàn),然后講解頂層IO約束復(fù)雜性,過程中會介紹DDR接口時(shí)序。

set_input_delay

set_output_delay

set_drive

set_driving_cell

set_input_transition

set_load

...

各個(gè)命令的具體用法可以在PT中通過man了解詳情,這里就不費(fèi)勁重復(fù)了:

pt_shell > man set_input_delay

模塊級IO約束實(shí)戰(zhàn)

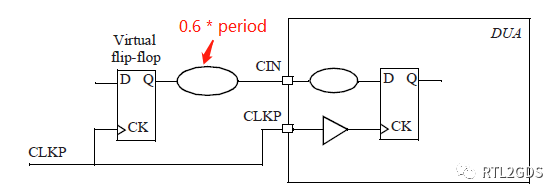

上圖給出了一種IN2REG路徑的示意圖,DUA為當(dāng)前模塊,外部有一個(gè)假想的虛擬寄存器在驅(qū)動(dòng)CIN端口,這種情況下我們可通過以下命令來約束:

set period 8

create_clock -name CLKP -period $period [get_ports CLKP]

#創(chuàng)建同頻率的虛擬時(shí)鐘

create_clock -name vCLKP -period $period

#參考值為0.6,根據(jù)實(shí)際情況調(diào)整

set_input_delay [expr 0.6 * $period] -clock vCLKP [get_ports CIN]

#假設(shè)端口buffer為BUFX4

set_driving_cell -lib_cell BUFX4 -pin Z [get_ports CIN]

虛擬時(shí)鐘的作用

使用set_input_delay時(shí),可以指定真實(shí)時(shí)鐘CLKP,也可以指定虛擬時(shí)鐘vCLKP,在CTS之前是沒有區(qū)別的。然而,在CTS之后,如果指定的是真實(shí)時(shí)鐘,那么虛擬寄存器的時(shí)鐘延遲就被忽略了。如果指定的是虛擬時(shí)鐘,工具往往可以根據(jù)內(nèi)部真實(shí)時(shí)鐘的平均延遲來估算外部虛擬寄存器的時(shí)鐘延遲,更加合理。

一般地,為了讓頂層的時(shí)序更容易滿足,在模塊級優(yōu)化的時(shí)候,都會對自己內(nèi)部的IN2REG和REG2OUT路徑約束更加嚴(yán)格,可以設(shè)置外部的延遲為60%的時(shí)鐘周期,給內(nèi)部的數(shù)據(jù)路徑留40%的空間。不過,具體問題需要具體分析了。

需要注意,set_input_delay 可以指定-max和-min選項(xiàng),分別對應(yīng)setup和hold時(shí)序檢查,如果只是指定其中一個(gè)選項(xiàng),或者都不指定,那么工具在檢查setup和hold時(shí),會使用相同的值。

端口Buffer和set_driving_cell配合使用

在實(shí)際項(xiàng)目中,為了避免模塊之間,或者模塊和頂層之間IO接口部分出現(xiàn)時(shí)序問題,一般會要求在靠近IO端口的地方添加具有一定驅(qū)動(dòng)能力的端口Buffer。在這種情況下,可以通過set_driving_cell來模擬端口的真實(shí)外部環(huán)境。假如沒有端口Buffer,也可以通過set_input_transition大致指定輸入端口的驅(qū)動(dòng)能力。

總體來說,set_driving_cell會考慮到OCV的影響,input transition是查表計(jì)算出來的,而set_input_transition比較簡單粗暴,在IO端口時(shí)序不那么關(guān)鍵的時(shí)候,也可以使用。但在頂層,一般使用后者,因?yàn)镮O單元的輸入電容較大,芯片外部具備驅(qū)動(dòng)能力較強(qiáng)的器件,標(biāo)準(zhǔn)單元庫中沒有buffer能夠驅(qū)動(dòng)。

頂層IO約束實(shí)戰(zhàn)

頂層IO約束在原理上與模塊級沒有本質(zhì)區(qū)別,然而由于頂層需要與外部器件進(jìn)行通訊,除了GPIO,還會接觸到各種標(biāo)準(zhǔn)協(xié)議接口,例如UART,I2C,SPI,LVDS,DDR等等,在寫SDC前需要讀一讀協(xié)議。更復(fù)雜的情況是,由于存在端口復(fù)用的情況,往往同一個(gè)端口具備多種時(shí)序要求,需要逐一定義。

上圖是一個(gè)PinMux(也稱為IOMux)的示意圖,在SoC設(shè)計(jì)中非常常見,特別對于IO limited的芯片來說,PinMux是很有必要的。看似復(fù)雜,其實(shí)只要各個(gè)擊破就能達(dá)到目標(biāo),SDC標(biāo)準(zhǔn)制定者已經(jīng)為我們考慮到了這一點(diǎn),通過set_input_delay的選項(xiàng)-add_delay,可以對同一個(gè)端口設(shè)置多重約束,例如:

set_input_delay [expr 0.6 * $periodA] -clock CLKA [get_ports CIN] -add_delay

set_input_delay [expr 0.3 * $periodB] -clock CLKB [get_ports CIN] -add_delay

另外,針對頂層輸出數(shù)字端口,需要根據(jù)芯片使用的實(shí)際情況set_load,一般的GPIO端口負(fù)載電容都在pF級別。

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123324 -

SoC設(shè)計(jì)

+關(guān)注

關(guān)注

1文章

151瀏覽量

19074 -

輸入電容

+關(guān)注

關(guān)注

1文章

46瀏覽量

9952 -

虛擬機(jī)

+關(guān)注

關(guān)注

1文章

962瀏覽量

29043 -

DDR接口

+關(guān)注

關(guān)注

0文章

5瀏覽量

7586

發(fā)布評論請先 登錄

擁有20多年工程實(shí)戰(zhàn)經(jīng)驗(yàn)的技術(shù)總工,和你談電機(jī)控制!

pcb制造業(yè)節(jié)約用電實(shí)戰(zhàn)經(jīng)驗(yàn)

FPGA寶貴實(shí)戰(zhàn)經(jīng)驗(yàn)及Verilog編程規(guī)范

【資料分享】ST MCU實(shí)戰(zhàn)經(jīng)驗(yàn)10篇,應(yīng)用問題,官方解答

LLEGRO高速高密PCB設(shè)計(jì)實(shí)戰(zhàn)經(jīng)驗(yàn)

振動(dòng)傳感器項(xiàng)目外包,有實(shí)戰(zhàn)經(jīng)驗(yàn)的電子工程師聯(lián)系我。

開關(guān)電源維修方法和實(shí)戰(zhàn)經(jīng)驗(yàn)

STM32 應(yīng)用實(shí)戰(zhàn)經(jīng)驗(yàn)篇推薦閱讀

ARM全國產(chǎn)云平臺部署容器實(shí)戰(zhàn)經(jīng)驗(yàn)分享

實(shí)戰(zhàn)經(jīng)驗(yàn):從5個(gè)方面來談IC設(shè)計(jì)資料下載

嵌入式項(xiàng)目實(shí)戰(zhàn)經(jīng)驗(yàn)

提升開關(guān)電源效率的理論分析與實(shí)戰(zhàn)經(jīng)驗(yàn)

移動(dòng)電源EMC整改:認(rèn)證失敗到一次通過的實(shí)戰(zhàn)經(jīng)驗(yàn)

Top和Block實(shí)戰(zhàn)經(jīng)驗(yàn)以及DDR接口時(shí)序

Top和Block實(shí)戰(zhàn)經(jīng)驗(yàn)以及DDR接口時(shí)序

評論