小芯片為工程師們提供了半導(dǎo)體領(lǐng)域的新機(jī)遇,但當(dāng)前的鍵合技術(shù)帶來(lái)了許多挑戰(zhàn)。現(xiàn)在,IBM 和 ASMPT 之間的一家合資企業(yè)已經(jīng)開(kāi)發(fā)出一種用于封裝芯片的新型混合鍵合技術(shù),可以在原子尺度上直接鍵合芯片,從而減小觸點(diǎn)尺寸。

chiplet 面臨哪些挑戰(zhàn),合資企業(yè)開(kāi)發(fā)了什么,這將如何幫助加速未來(lái)的 chiplet 設(shè)計(jì)?

小芯片面臨哪些挑戰(zhàn)?

隨著半導(dǎo)體制造商努力縮小單個(gè)晶體管的尺寸,研究人員也在不斷尋找提高現(xiàn)代設(shè)備性能的新方法。雖然一種選擇是使通用處理器更強(qiáng)大(具有更快的計(jì)算速度和更大的內(nèi)存大小),但另一種選擇是識(shí)別資源密集型的特定任務(wù)并創(chuàng)建專用硬件加速器。這種硬件加速器的使用已經(jīng)得到廣泛使用,例如處理圖形例程的 GPU、針對(duì)神經(jīng)網(wǎng)絡(luò)優(yōu)化的 AI 加速器,以及允許在不影響性能的情況下進(jìn)行即時(shí)加密的加密加速器。

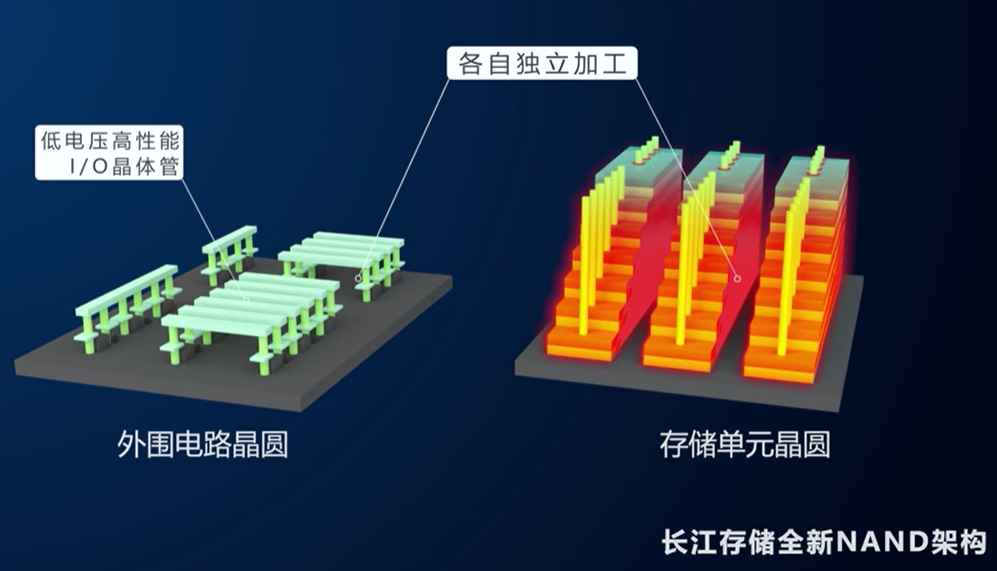

然而,對(duì)于加速器提供的所有好處,將加速器放置在芯片外部會(huì)對(duì)數(shù)據(jù)帶寬產(chǎn)生巨大影響,但嘗試將加速器集成到單個(gè)單片半導(dǎo)體中會(huì)減少可用于其他硬件(例如處理器內(nèi)核和內(nèi)存)的總面積。為了解決這一挑戰(zhàn),工程師們正在轉(zhuǎn)向小芯片,即具有特定用途的小型獨(dú)立半導(dǎo)體芯片,并將這些小芯片連接在一起以創(chuàng)建封裝模塊。

這不僅讓工程師能夠充分利用任何一個(gè)裸片上的硅空間,而且還允許定制,小芯片可以換成不同的設(shè)備,從而實(shí)現(xiàn) SoC 的完全定制。但是,盡管小芯片帶來(lái)了所有優(yōu)勢(shì),但工程師們正在努力應(yīng)對(duì)一個(gè)主要缺點(diǎn):芯片互連。

在 IBM Research 最近的一篇博客文章中,他們深入探討了小芯片的概念以及它們?nèi)绾螏椭朔@些挑戰(zhàn)。小芯片本質(zhì)上是復(fù)雜功能芯片的更小的功能塊,它可以包括獨(dú)立的計(jì)算處理器、圖形單元、AI 加速器和 I/O 功能。通過(guò)打破片上系統(tǒng)模型,chiplet 可以帶來(lái)更節(jié)能的系統(tǒng),縮短系統(tǒng)開(kāi)發(fā)周期,并以比現(xiàn)在更低的成本構(gòu)建專用計(jì)算機(jī)。

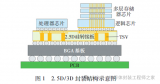

一種解決方案是將小芯片倒裝到類似于 PCB 的基板上,并將裸片焊接到基板上。然而,由于目前焊接技術(shù)的限制,芯片上的焊盤尺寸必須大于幾十微米,這就限制了互連密度。同時(shí),焊料可能難以控制,導(dǎo)致帶寬受限的低質(zhì)量連接。

IBM 的第二代納米片技術(shù)為在 300 毫米晶圓上生產(chǎn)的 2 納米節(jié)點(diǎn)鋪平了道路。這項(xiàng)技術(shù)允許在指甲蓋大小的空間內(nèi)安裝 500 億個(gè)晶體管。用于 2 納米芯片節(jié)點(diǎn)的納米片晶體管是對(duì)幾個(gè)較小的里程碑的驗(yàn)證,這些里程碑證明了這是可以做到的,也是 IBM 跨學(xué)科專家團(tuán)隊(duì)在材料、光刻、集成、設(shè)備、表征和建模方面的辛勤工作和奉獻(xiàn)精神的驗(yàn)證。

另一種選擇是將裸片安裝到基板上并在裸片之間使用金線。雖然這通常用于芯片鍵合,但它是一種昂貴的工藝,可能不適合定制小芯片設(shè)計(jì)的小批量生產(chǎn)。還有一些實(shí)際限制可能會(huì)使芯片的鍵合線變得復(fù)雜(因?yàn)榻Y(jié)束鍵合線會(huì)留下尾巴,尾巴會(huì)四處移動(dòng)并可能導(dǎo)致短路)。

IBM 和 ASMPT 開(kāi)發(fā)了

一種新的小芯片鍵合技術(shù)

認(rèn)識(shí)到小芯片鍵合面臨的挑戰(zhàn),IBM和ASMPT的研究人員聯(lián)合開(kāi)發(fā)了一種新的解決方案,可以幫助加速小芯片的部署。這種用于封裝芯片的新型混合鍵合允許芯片在原子尺度上直接鍵合。

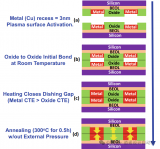

IBM 和 ASMPT 在 chiplet bonding 技術(shù)上取得了重大突破。他們開(kāi)發(fā)了一種混合鍵合技術(shù),可以大大減少兩個(gè)小芯片之間所需的鍵合尺寸。這是通過(guò)在原子尺度上利用銅和氧化物層來(lái)實(shí)現(xiàn)的,鍵本身只有幾個(gè)原子厚。這一發(fā)展可能會(huì)徹底改變小芯片的封裝方式,并加速小芯片技術(shù)的部署。

為了幫助粘合小芯片,該研究機(jī)構(gòu)開(kāi)發(fā)了一種混合技術(shù),該技術(shù)在原子尺度上利用銅和氧化物層(粘合本身只有幾個(gè)原子厚)。然而,為了使粘合起作用,必須去除兩個(gè)表面之間的所有水分和碎屑,因?yàn)榧词故菐讉€(gè)水分子也足以影響兩個(gè)觸點(diǎn)之間的電氣連續(xù)性。這也適用于可能在兩個(gè)表面之間形成的潛在氣泡,因?yàn)樾馀菘梢院苋菀椎赝ㄟ^(guò)靜電力容納氣體分子。

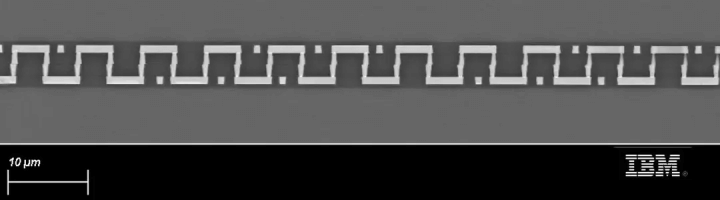

一張圖片展示了通過(guò)該團(tuán)隊(duì)的方法實(shí)現(xiàn)的兩層之間的微小結(jié)合。

IBM 和 ASMPT 開(kāi)發(fā)的混合鍵合技術(shù)改變了半導(dǎo)體行業(yè)的游戲規(guī)則。通過(guò)將兩個(gè)小芯片之間所需的鍵合尺寸減小到僅幾個(gè)原子,該技術(shù)可以顯著增加兩個(gè)不同芯片之間的連接密度。這反過(guò)來(lái)又會(huì)導(dǎo)致數(shù)據(jù)帶寬的大幅增加,為半導(dǎo)體產(chǎn)品的設(shè)計(jì)和性能開(kāi)辟新的可能性。

據(jù)研究人員稱,所開(kāi)發(fā)的方法與現(xiàn)有的不同小芯片之間使用的芯片接合方法極為相似,但規(guī)模要小得多。此外,該合資企業(yè)能夠?qū)崿F(xiàn)與 ASMPT 提供的現(xiàn)有機(jī)械的結(jié)合,這意味著這項(xiàng)新技術(shù)有可能在未來(lái)幾年內(nèi)得到部署。

這種貼片技術(shù)如何改變未來(lái)的技術(shù)?

到目前為止,新開(kāi)發(fā)的鍵合技術(shù)提供的最大優(yōu)勢(shì)是它顯著增加了兩個(gè)不同芯片之間的連接密度,從而增加了數(shù)據(jù)帶寬。然而,增加連接密度也允許工程師將復(fù)雜的設(shè)計(jì)拆分到多個(gè)芯片上,這不僅有助于提高晶圓良率,而且會(huì)顯著增加設(shè)計(jì)的尺寸。反過(guò)來(lái),這會(huì)增加大型半導(dǎo)體產(chǎn)品的晶體管數(shù)量,從而導(dǎo)致具有更高處理器和內(nèi)存容量的指數(shù)級(jí)更強(qiáng)大的系統(tǒng)。

此外,新的鍵合技術(shù)還有助于加速工程師的半導(dǎo)體定制。雖然仍處于起步階段,但如果 chiplet 行業(yè)與 PCB 行業(yè)有任何相似之處,那么用不了多久,工程師就能夠以近乎相同的方式設(shè)計(jì)自己的 SoC,以提供組裝服務(wù)的定制 PCB。此類服務(wù)將允許工程師創(chuàng)建適合其應(yīng)用的 SoC,為關(guān)鍵任務(wù)集成加速器,同時(shí)利用低能耗選項(xiàng)來(lái)降低功耗。

總體而言,IBM 和 ASMPT 開(kāi)發(fā)的產(chǎn)品令 chiplet 行業(yè)興奮不已。雖然需要做更多的研究來(lái)確保鍵合技術(shù)的可靠性和可重復(fù)性,但這種用于封裝芯片的新型混合鍵合可能會(huì)徹底改變半導(dǎo)體的設(shè)計(jì)和制造方式。

這種新的混合鍵合技術(shù)的開(kāi)發(fā)證明了IBM和ASMPT的研究人員正在進(jìn)行的創(chuàng)新工作。這是小芯片技術(shù)領(lǐng)域的一個(gè)重要里程碑,對(duì)未來(lái)充滿希望。隨著這項(xiàng)技術(shù)的不斷發(fā)展,我們可以期待在半導(dǎo)體的設(shè)計(jì)和制造方式上看到更多激動(dòng)人心的發(fā)展。

IBM 對(duì)小芯片的研究已經(jīng)顯示出可喜的成果。他們正在根據(jù)行業(yè)小芯片標(biāo)準(zhǔn)的兩個(gè)主要競(jìng)爭(zhēng)者通用小芯片互連快速 (UCIe) 聯(lián)盟和開(kāi)放計(jì)算項(xiàng)目的線束規(guī)范的方向探索小芯片I/O 的各種設(shè)計(jì)。IBM 研究人員參與了這兩項(xiàng)計(jì)劃,在潛在的未來(lái)小芯片封裝解決方案的背景下研究信號(hào)映射策略。這種主動(dòng)方法可確保 IBM 在標(biāo)準(zhǔn)達(dá)成一致后立即準(zhǔn)備好構(gòu)建小芯片。

審核編輯:劉清

-

加速器

+關(guān)注

關(guān)注

2文章

823瀏覽量

38918 -

SoC芯片

+關(guān)注

關(guān)注

1文章

636瀏覽量

35657 -

封裝芯片

+關(guān)注

關(guān)注

0文章

18瀏覽量

8651 -

chiplet

+關(guān)注

關(guān)注

6文章

453瀏覽量

12866

發(fā)布評(píng)論請(qǐng)先 登錄

混合鍵合市場(chǎng)空間巨大,這些設(shè)備有機(jī)會(huì)迎來(lái)爆發(fā)

閃存沖擊400層+,混合鍵合技術(shù)傳來(lái)消息

混合鍵合在先進(jìn)封裝領(lǐng)域取得進(jìn)展

從發(fā)展歷史、研究進(jìn)展和前景預(yù)測(cè)三個(gè)方面對(duì)混合鍵合(HB)技術(shù)進(jìn)行分析

三維堆疊封裝新突破:混合鍵合技術(shù)揭秘!

混合鍵合的基本原理和優(yōu)勢(shì)

SK海力士將在HBM生產(chǎn)中采用混合鍵合技術(shù)

金絲鍵合強(qiáng)度測(cè)試儀試驗(yàn)方法:鍵合拉脫、引線拉力、鍵合剪切力

銅線鍵合焊接一致性:如何突破技術(shù)瓶頸?

Chiplet混合鍵合難題取得新突破

Chiplet混合鍵合難題取得新突破

評(píng)論