來源:屹立芯創

簡介:

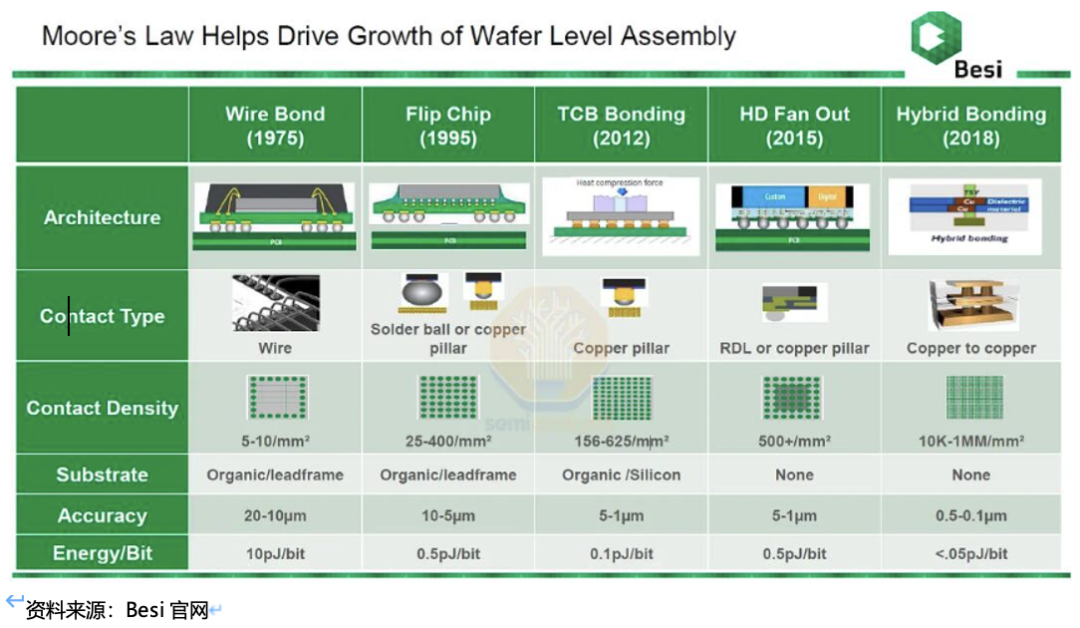

所謂混合鍵合(hybrid bonding),指的是將兩片以上不相同的Wafer或Die通過金屬互連的混合鍵合工藝,來實現三維集成,在Hybrid Bonding前,2D,2.5D及3D封裝都是采用焊錫球凸點(solder bump)或微凸點(Micro bump)來實現芯片與基板,芯片與中介層(Interposer),芯片與芯片間的電連接。Solder bump/micro bump在制備工藝中都有植球的步驟,所植的球就是焊錫球(Solder bump),所以在Hybrid Bonding之前芯片間的連接都是靠焊錫球進行連接。

當然Solder bump是植在銅柱(Copper bump)上的。當copper bump pitch小于10~20um時,焊錫球solder bump就變成了工藝難點及缺陷的主要來源。這時候就需要一種新的工藝來解決bump間距小于10微米芯片間鍵合的問題。

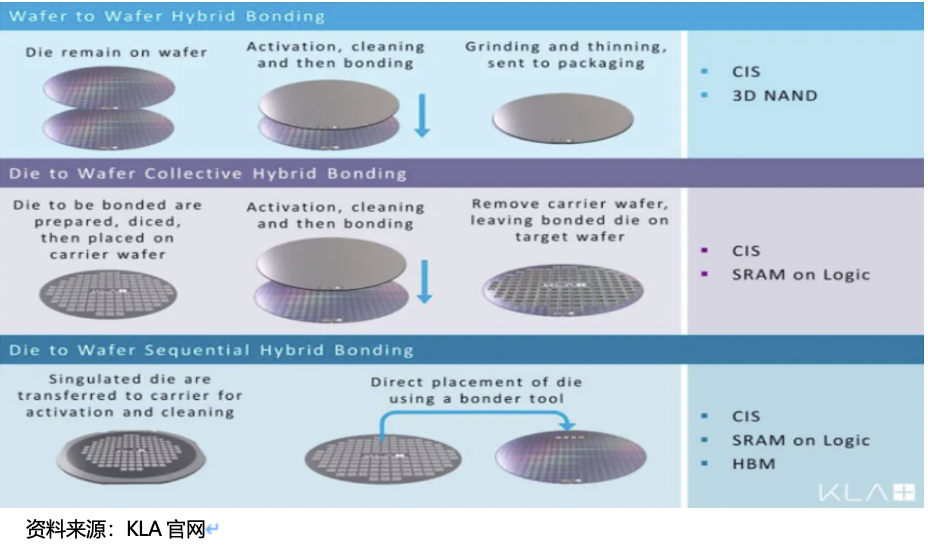

混合鍵合兩種常見的類型:

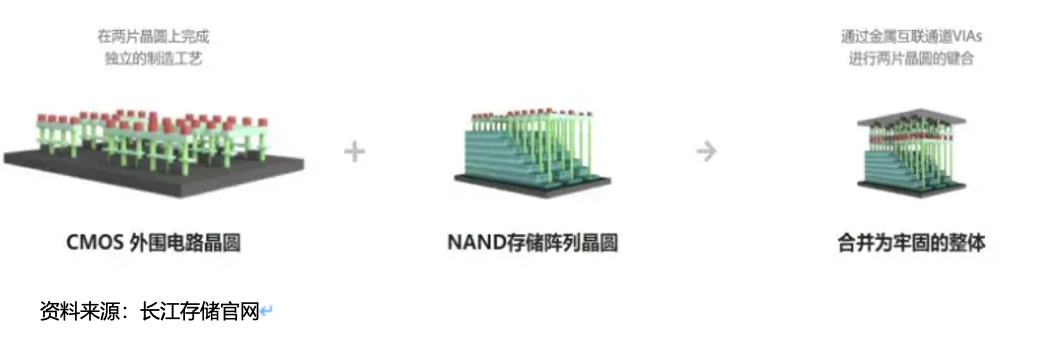

1.Wafer to Wafer (W2W)晶圓對晶圓:適合高良率的芯片,如CMOS、3D NAND。2.Die to Wafer (D2W)芯片對晶圓:適合不同種類型芯片集成,如異構集成。

W2W可以提供更高的對準精度、吞吐量和鍵合良率。但一個主要限制是無法選擇已知的合格芯片(KGD)。這會導致將有缺陷的芯片粘合到好的芯片上,從而導致優質芯片的浪費。W2W的另一個缺點是兩片晶圓上芯片的尺寸必須一致,因此這限制了異構集成選項的靈活性。所以,W2W適用于良率高的晶圓,通常是設計尺寸較小芯片,如CMOS圖像傳感器、3D NAND。

D2W允許將不同尺寸、工藝節點的芯片(如邏輯芯片與存儲芯片)選擇性集成到同一晶圓上,從而支持異構集成和定制化設計,避免了W2W因整片晶圓鍵合導致的良率損失問題(例如一片晶圓存在缺陷時,僅影響單個芯片而非整片)。此外,D2W可通過分步測試篩選合格芯片(KGD)再進行鍵合,降低了整體成本。 這種特性使其在先進封裝(如3D堆疊)中更具適應性,尤其適用于需要整合多來源芯片的高性能計算場景。然而,D2W混合鍵合的技術實現難度更高,主要體現在亞微米級對準精度和界面共面性控制兩大挑戰。

工藝流程:

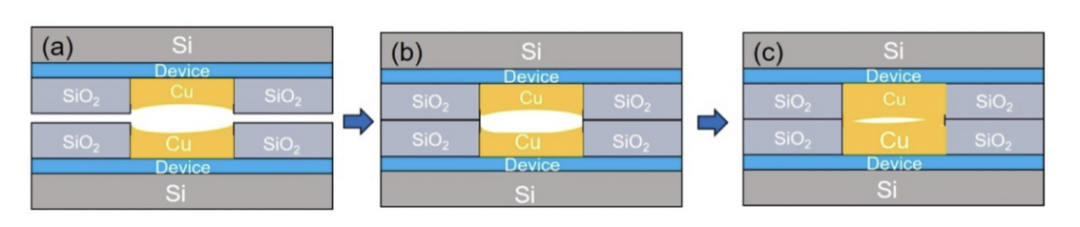

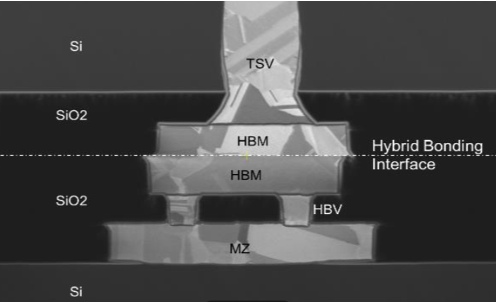

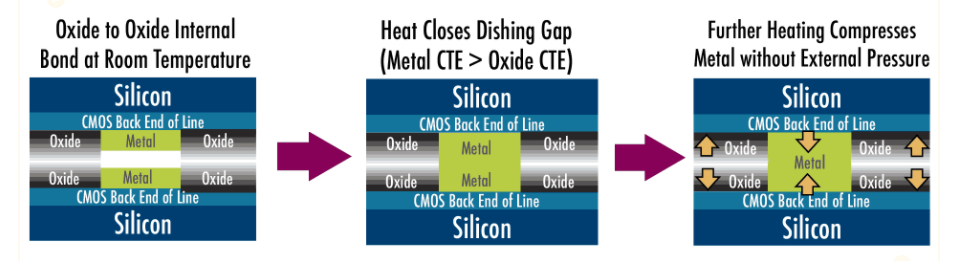

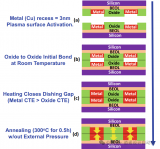

混合鍵合結合了兩種不同的鍵合技術:介電鍵合和金屬互連。一般采用介電材料(通常是SiO?)與嵌入式銅(Cu)焊盤結合,通過形成電介質鍵(dielectric bond)和金屬鍵(metal bond)實現兩個晶圓(wafers)或裸片(dies)之間建立永久電連接,而無需焊料凸塊。這種無凸塊方法通過減少信號損耗和改善熱管理來提高電氣性能 。

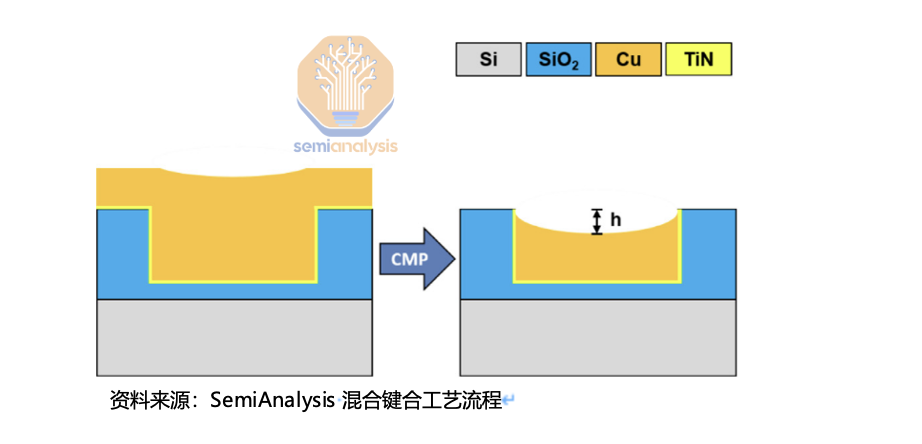

一.表面準備:晶圓需經過化學機械拋光/平坦化(CMP)和表面活化及清洗處理。混合鍵合層的表面光滑度非常關鍵。Hybrid Bonding界面處對任何類型的凹凸都可能會產生空洞和無效的鍵合,通常需要確保表面粗糙度(Ra)低于0.5nm。,銅焊盤為1nm。為了達到這種平滑度,需要進行化學機械平坦化(CMP)。

CMP完成后,還需要進行表面活化(Activation)等離子體處理:對SiO?表面進行Ar、N?或O?等離子體處理,增加表面羥基(-OH)密度,增強親水性。銅表面可能需還原性等離子體(如H?)去除氧化層。

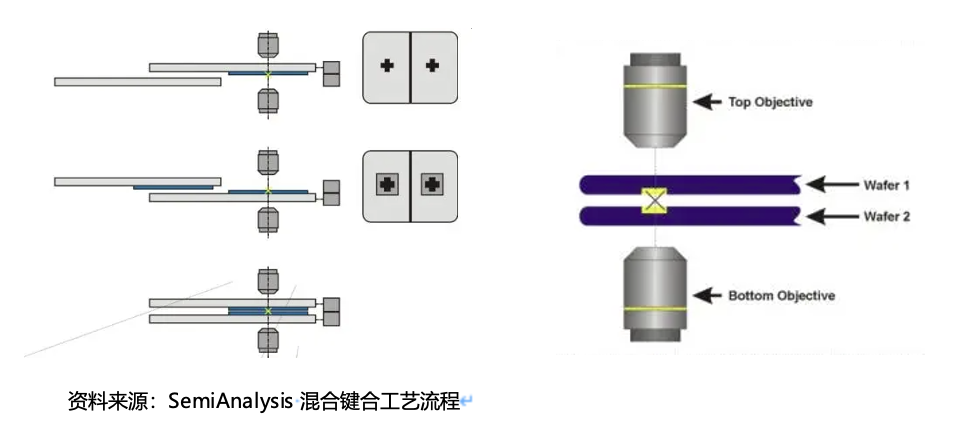

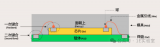

二.對位:晶圓或芯片的對準需要在潔凈室(Class 1-10)中進行,避免顆粒污染。經過精確對準,以確保金屬焊盤正確對應,從而實現有效的電氣互連。

需要注意的是:由于鍵合過程涉及兩個非常光滑且平坦的表面齊平地鍵合在一起,因此鍵合界面對任何顆粒的存在都非常敏感;高度僅為1微米的顆粒會導致直徑為10毫米的粘合空隙,從而導致鍵合缺陷。

三.預鍵合:經過對位之后晶圓或芯片間僅形成初始電介質鍵,此時只是通過范德華力結合在一起,還需要在室溫或略高的溫度、在N?或真空環境下,配合一定的壓力,通過原子擴散和機械互鎖形成牢固的鍵合。

南京屹立芯創擁有多項創新發明專利技術,設備可以通過在真空和升溫環境中對晶圓與芯片施加穩定、均勻的壓力,讓芯片與晶圓之間更平坦化,實現晶圓或芯片間穩定鍵合。

南京屹立芯創有著豐富的經驗和解決方式,致力于提高客戶產品的質量及可靠度。公司的產品廣泛應用于半導體封裝,電子組裝,5G通訊,新能源應用,車用零件,航天模塊,生化檢測等各大科技領域。

四.鍵合后處理:初始鍵合后,還需要通過額外的熱處理來進一步促進銅向介電層擴散,確保穩固的互連,以此來增強鍵合強度和電氣性能。

混合鍵合應用:

混合鍵合用于芯片的垂直(或3D)堆疊。混合鍵合的顯著特點是無凹凸。它從基于焊接的凸塊技術轉向直接的銅對銅連接。這意味著頂模和底模彼此齊平。兩個芯片都沒有凸塊,只有可以縮放到超細間距的銅焊盤。沒有焊料,因此避免了與焊料相關的問題。同時混合鍵合在電學性能方面也有獨特的優勢,Hybrid Bonding信號丟失率幾乎可以忽略不計,這在高吞吐量,高性能計算領域優勢明顯。

目前常見的應用場景:

1.3D芯片堆疊:混合鍵合被廣泛應用于處理器和內存堆棧中,例如AMD的3D V-Cache技術和HBM高帶寬內存的多層堆疊。通過混合鍵合,可以將CPU與額外緩存芯片緊密連接在一起,顯著提升系統性能;同時,在圖形處理單元(GPU)和高性能計算領域,將內存芯片直接堆疊到邏輯芯片上,極大地提高了數據帶寬和訪問效率。

2.異構集成:混合鍵合技術也促進了異構系統的集成,使得各種不同工藝節點制造的芯片可以有效地結合在一起,形成一個單一的高性能封裝體。例如,將射頻芯片、傳感器、處理器等多種類型的芯片整合在同一封裝內,優化了物聯網設備、智能手機和其他智能硬件的空間利用和整體性能。

3.圖像傳感器:混合鍵合在CMOS圖像傳感器(CIS)領域也有重要應用,如背照式(BSI)傳感器和堆疊式傳感器等,其中底層的像素陣列通過混合鍵合技術與頂層的電路層相連,降低了光路損失并實現了更小型化的相機模組設計。

總結:

混合鍵合作為先進封裝技術的核心組成部分,正逐漸成為推動半導體行業向三維集成發展的重要驅動力。從市場規模來看,當前火爆的AI算力需求,推動混合鍵合技術市場正以顯著增速擴張,其在高密度集成、低功耗傳輸上的優勢使其成為3D封裝的關鍵技術。

-

芯片

+關注

關注

459文章

52169瀏覽量

436108 -

晶圓

+關注

關注

52文章

5118瀏覽量

129161 -

工藝

+關注

關注

4文章

669瀏覽量

29248 -

鍵合

+關注

關注

0文章

78瀏覽量

8057

原文標題:混合鍵合(Hybrid Bonding)工藝介紹

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

介紹芯片鍵合(die bonding)工藝

混合鍵合市場空間巨大,這些設備有機會迎來爆發

有償求助本科畢業設計指導|引線鍵合|封裝工藝

銅混合鍵合的發展與應用

什么是混合鍵合?為什么要使用混合鍵合?

金絲鍵合工藝溫度研究:揭秘鍵合質量的奧秘!

混合鍵合工藝介紹

混合鍵合工藝介紹

評論