臺積電在2022 IEDM上發表了兩篇關于3nm的論文;“Critical Process features Enabling Aggressive Contacted Gate Pitch Scaling for 3nm CMOS Technology and Beyond”和“A 3nm CMOS FinFlex Platform Technology with Enhanced Power Efficiency and Performance for Mobile SOC and High Performance Computing Applications”。

當我在演講前閱讀這兩篇論文時,我的第一反應是第一篇論文描述了臺積電的 N3 工藝,第二篇論文描述了 N3E 工藝,這在第二次演講中得到了演講者的證實。

我的第二個反應是這些論文延續了臺積電盡量減少所呈現的技術細節數量的習慣。在這兩篇論文中,電氣結果至少以實數為單位,但第一篇論文只有 Contacted Gate Pitch,第二篇論文只有最小金屬間距。我覺得這非常令人沮喪,一旦零件進入公開市場,內部人員和臺積電的競爭對手可能已經知道它們是什么,關鍵pitch將被測量和披露,我不認為呈現高質量的技術論文會有什么問題。

N3工藝

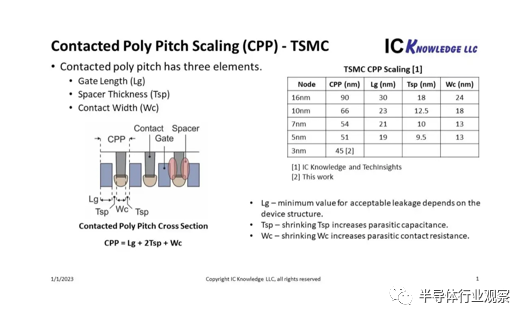

在第一篇論文中,臺積電公開了 45nm 的 Contacted Gate Pitch(Contacted Poly Pitch,如我所描述的 CPP)。CPP 由柵極長度 (Lg)、接觸間隔厚度 (Tsp) 和接觸寬度 (Wc) 組成,如圖 1 所示。

圖 1.CPP。

從圖 1 中,我們可以看到臺積電通過減少構成 CPP 的所有三個元素來減少每個新節點的 CPP。邏輯設計是通過使用標準單元完成的,而 CPP 是標準單元寬度的主要驅動因素,因此縮小 CPP 是提高新節點密度的關鍵部分。

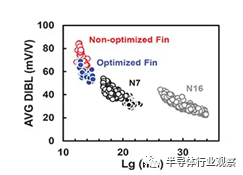

最小 Lg 是溝道柵極控制的函數,例如從具有不受約束的溝道厚度的單柵極平面器件轉移到具有 3 個柵極圍繞薄溝道的 FinFET,從而實現更短的 Lg。FinFET 的柵極控制在鰭底部最弱,優化至關重要。圖 2 說明了多個 TSMC 節點的 DIBL 與 Lg,以及優化鰭片如何減少當前工作的 DIBL。

圖 2. DIBL 與 Lg。

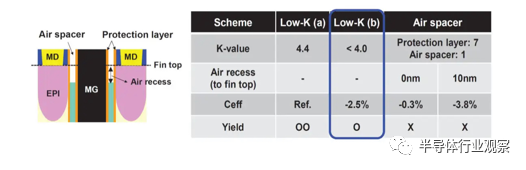

縮小 CPP 的第二個因素是 Tsp 厚度。除非墊片(spacer)經過優化以降低 k 值,否則降低 Tsp 會增加寄生電容。圖 3 說明了 TSMC 對低 k 間隔物與氣隙間隔物的研究。臺積電發現低 k 間隔物是縮放 CPP 的最佳解決方案。

圖 3. 與柵極間隔器的接觸。

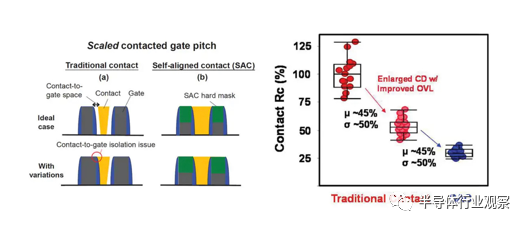

CPP 的最后一個元素是接觸寬度。在這項工作中,開發了一種優化的自對準接觸 (SAC) 方案,可提供較低的接觸電阻。圖 4 的左側說明了 SAC,右側說明了電阻改善。

圖 4. 自對準觸點。

這項工作使 N3 工藝具有 0.0199μm 2的高密度 SRAM 尺寸。隨著臺積電推進其 2nm 工藝,這項工作也很重要。在 2nm 時,臺積電將轉向一種稱為水平納米片 (HNS) 的環柵 (GAA) 架構,HNS 可實現更短的 Lg(4 個柵極而不是三個圍繞一個薄柵極),但 Wc 和 Tsp 將還是有待優化。

N3E工藝

臺積電將 N3E 工藝描述為 N3 的增強版本,有趣的是,N3E 被認為比 N3 實現了更寬松的間距,例如 CPP、M0 和 M1 都被認為出于性能和良率的原因而被放松。關于臺積電 N3 是否準時,有不同的說法。我的看法是,N5 進入風險始于 2019 年,到 2020 年圣誕節,商店中出現了配備 N5 芯片的 Apple iPhone。N3 進入風險從 2021 年開始,配備 N3 芯片的 iPhone 要到明年才能上市。在我看來,這個過程至少晚了 6 個月。在本文中,公開了尺寸為 0.021 μm 2的高密度 SRAM 單元。大于 0.0199 μm 2的 N3 SRAM 單元。N3 的產率通常被描述為良好,提到了 60% 到 80%。

本文討論的這個過程有兩個主要特點:

FinFlex

最小金屬間距為 23 納米,銅互連采用“創新”襯里以實現低電阻。

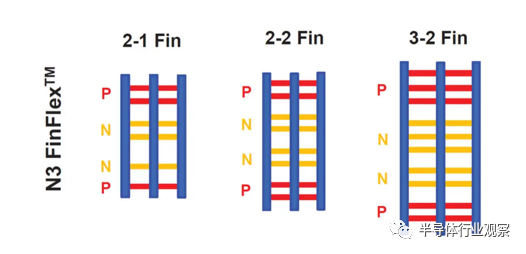

FinFlex 是一種混合和匹配策略,具有雙高度cell,可以是頂部 2 鰭cell,底部 1 鰭cell以獲得最大密度,2 鰭cell超過 2 鰭cell作為中等性能和密度,以及 3 鰭超過 2 個鰭狀的cell可實現最佳性能。這為設計人員提供了很大的靈活性來優化他們的電路。

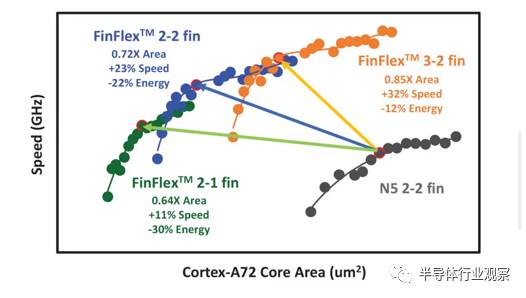

圖 5 說明了各種 FinFlex 配置,圖 6 將每種配置的規格與 5nm 的標準 2 over 2 鰭式cell進行了比較。

圖 5. FinFlex cell。

圖 6. 3nm FinFlexcell性能與 5nm cell的對比。

本文中的繪圖是 15 級金屬堆疊在大約 550 歐姆時的通孔電阻分布。在目前的工藝中,功率通過金屬堆疊的頂部進入,必須通過通孔鏈向下傳輸到設備,550 歐姆的電源線電阻很大。這就是英特爾、三星和臺積電都宣布為其 2 納米級工藝提供背面供電的原因。隨著晶圓的極度減薄,從背面引入電源的通孔應能使通孔電阻提高 10 倍以上。

比較

作為讀者,您可能會有一個問題,即此工藝與三星的 3nm 工藝相比如何。臺積電仍在使用 FinFET,而三星已過渡到 GAA——他們稱之為多橋 HNS。

根據我們的計算,在 5nm 節點,臺積電最密集的邏輯單元是三星最密集邏輯單元密度的 1.30 倍。如果您查看圖 6 中的 TSMC 密度值,在 5nm 中,2-2 鰭式單元的密度比 2-2 單元高 1.39 倍,而 2-1 單元的密度提高了 1.56 倍。三星有兩個版本的 3nm,SF3E(3GAE)版本比 5nm 密度高 1.19 倍,SF3(3GAP)版本比 5nm 密度高 1.35 倍,進一步落后于臺積電行業領先的密度。我也相信臺積電在 3nm 上有更好的性能和更好的功率,盡管三星已經縮小了功率差距可能是由于 HNS 工藝。

審核編輯 :李倩

-

臺積電

+關注

關注

44文章

5755瀏覽量

169811 -

單柵極

+關注

關注

0文章

2瀏覽量

5832 -

FinFET

+關注

關注

12文章

257瀏覽量

91182

原文標題:臺積電3nm FinFET工藝

文章出處:【微信號:半導體設備與材料,微信公眾號:半導體設備與材料】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

臺積電2nm制程良率已超60%

臺積電加大亞利桑那州廠投資,籌備量產3nm/2nm芯片

蘋果M5芯片量產,采用臺積電N3P制程工藝

消息稱臺積電3nm、5nm和CoWoS工藝漲價,即日起效!

臺積電2025年起調整工藝定價策略

臺積電2nm工藝將量產,蘋果iPhone成首批受益者

臺積電分享 2nm 工藝深入細節:功耗降低 35% 或性能提升15%!

臺積電3nm FinFET工藝

臺積電3nm FinFET工藝

評論