本篇博客將為您演示如何使用此報告來幫助加速調試,甚至完全避免硬件故障,最后確定此問題根本原因是校準完成時出現爭用狀況。出現爭用狀況的原因是由于某個多周期約束所覆蓋的時序例外,由此導致在時序分析報告中并未標記此問題。

這是使用方法論報告系列博文的第 5 部分。如需閱讀整個系列中的所有博文,請點擊下方標題查看。

第3部分:時序已滿足,但硬件中存在 DDR4 校準失敗

問題說明:

客戶在使用 UltraScale+ DDR4 IP 時,在硬件中遇到校準后數據錯誤。

根據設計的布線和實現,此問題與構建有關,換言之,在產品開發期間對多個構建鏡像進行測試時,此問題可能出現而后又消失。此外,此問題可能僅在小部分板上出現。

時序報告顯示沒有任何違例。

調試方法:

由于重新實現后,此問題可能就會消失,因此無法使用 ILA 調試。

我們在已布線的 DCP 中使用 ECO 來探測未使用的管腳的信號,通過示波器觀測信號發現哪個(些)信號開始顯現錯誤。

最終,我們將問題范圍縮小到 1 個特定的信號線,在 DCP 中對該信號線進行重新布線后,故障消失了。

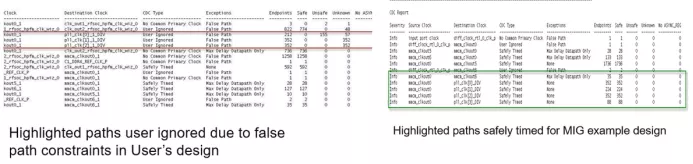

隨后,我們檢查了與此信號線相關的路徑上的時序分析和時序約束:

1. 經過該信號線的路徑的時序報告。在此報告中,我們得知,所涉及的路徑被多周期路徑約束所覆蓋

report_timing -through [get_nets ]

2. 打開“Timing Constraints”Wizard,查找對應的多周期路徑約束。

工具 (Tools) -> 時序 (Timing) -> 編輯時序約束 (Edit Timing Constraints)

我們在“Timing Constraints”Wizard 中發現了以下多周期路徑約束:

set_multicycle_path -setup -from [get_pins */u_ddr_cal_top/calDone*/C] 8 set_multicycle_path -hold -end -from [get_pins */u_ddr_cal_top/calDone*/C] 7

基于以上分析,我們判定在這些路徑上存在爭用狀況問題。

這些多周期路徑約束不應添加,在此用例中,應在每個時鐘周期內正確捕獲數據,以避免出現爭用狀況,因此,這些路徑不屬于多周期路徑。

根本原因分析:

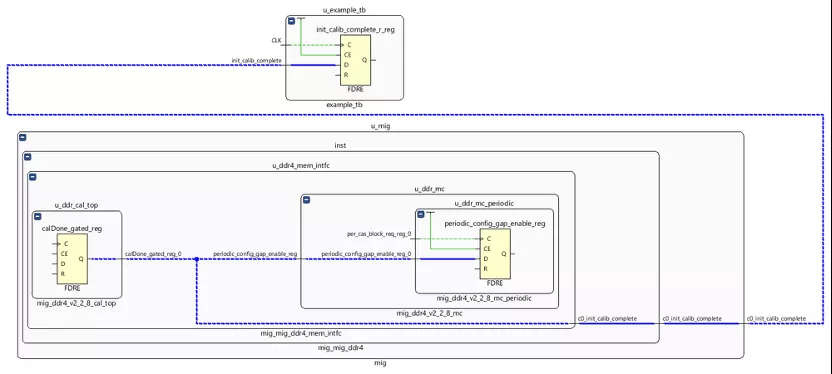

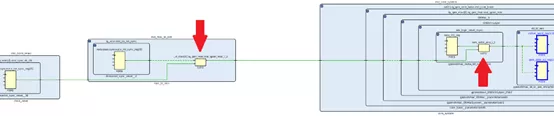

以下就是發生爭用狀況問題的路徑。

其中 2 個目標都應在同一個周期內接收到 calDone 信號,因為這兩者緊密相關。這 2 條路徑屬于不同時序路徑,各自都應在不同時鐘周期達成時序收斂(根據多周期約束,應在 1 到 8 個周期內達成時序收斂)。這可能導致 calDone 在不同時間線到達目標,導致功能異常。

另一方面,2 個目標都沒有 CE 管腳控制(CE 管腳綁定到 VCC)。因此,未能在同一時鐘周期內捕獲 2 條路徑上的數據,所以這些路徑并非合格的多周期路徑。

此多周期約束違例實際上是由 Methodology Report 捕獲的:

TIMING-46 警告 1

多周期路徑含綁定 CE 管腳

在寄存器

u_mig/inst/u_ddr4_mem_intfc/u_ddr_cal_top/calDone_gated_reg/Q

與寄存器

u_example_tb/init_calib_complete_r_reg/D

之間定義了 1 條或多條多周期路徑,并具有直接連接,且 CE 管腳已連接到 VCC(請參閱 Vivado IDE 中的“時序約束 (Timing Constraint)”窗口中的約束位置 6)。這可能導致路徑要求不準確。

TIMING-46 警告 2

多周期路徑含綁定 CE 管腳

在寄存器

u_mig/inst/u_ddr4_mem_intfc/u_ddr_cal_top/calDone_gated_reg/Q

與寄存器

u_mig/inst/u_ddr4_mem_intfc/u_ddr_mc/u_ddr_mc_periodic/periodic_config_gap_enable_reg/D

之間定義了 1 條或多條多周期路徑,并具有直接連接,且 CE 管腳已連接到 VCC(請參閱 Vivado IDE 中的“時序約束 (Timing Constraint)”窗口中的約束位置 6)。

這可能導致路徑要求不準確。

最好在流程初期階段盡早檢查 Methodology Report。在諸如此類的示例中,它可幫助您捕獲并修復多周期違例,并避免發生硬件故障。您還可以在調試過程中先運行 Methodology Report,并查看警告,其中高亮的違例將有助于加速問題調查。

解決辦法:

【賽靈思答復記錄 73068】提供的補丁可用于解決在低于 2020.1 版的版本中發生的此問題。

從 2020.1 版起,已移除了多周期路徑約束,并在路徑上添加了流水線階段,以簡化時序收斂,同時確保所有目標都能在同一個互連結構周期內達成時序收斂。

結論:

1. 在設計流程中盡早運行 Methodology Report 以便捕獲并修復潛在問題。

2. 請在含綁定到 VCC 的 CE 管腳的路徑上謹慎使用多周期約束。

審核編輯:湯梓紅

-

DDR4

+關注

關注

12文章

328瀏覽量

41525 -

時序

+關注

關注

5文章

397瀏覽量

37784

發布評論請先 登錄

引起調節的根本原因是什么

引起調節的根本原因是偏差嗎

低功耗產生的根本原因及其控制方法

內核oops的根本原因是什么?我們如何調試內核oops?

使用SPI找到無鉛制造缺陷的根本原因

如何修復硬件中存在DDR4校準錯誤

硬件中存在DDR4校準后數據錯誤

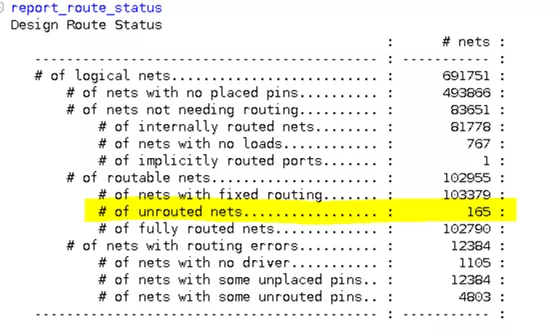

XILINX使用方法論設計無法連貫布線

網線是影響網速快慢的根本原因嗎

DDR4 IP校準后硬件故障的調試方法與根本原因分析

DDR4 IP校準后硬件故障的調試方法與根本原因分析

評論