繼最近發(fā)布一些突破性新硅光子(SiPh)探針的發(fā)展對于CM300xi探針臺,我們想向后盤旋并深入了解一些細(xì)節(jié)。我們之前展示了一些OptoVue Pro?的亮點,可以在不移除當(dāng)前被測試晶圓的情況下原位執(zhí)行光學(xué)定位器校準(zhǔn),從而縮短了數(shù)據(jù)采集時間。在這里,我們將探討高帶寬的新邊緣耦合效率。

用于水平模級邊緣耦合

通過使光纖/陣列通過水平裸片級邊緣耦合盡可能靠近裸露的波導(dǎo)小平面,可以實現(xiàn)高帶寬應(yīng)用的最佳耦合效率。真正的邊緣耦合功能可實現(xiàn)逼真的環(huán)境條件仿真,其設(shè)備性能最接近最終應(yīng)用。

我們提供了市場上唯一的解決方案,該解決方案能夠?qū)崿F(xiàn)水平模具級邊緣耦合的高級自動對準(zhǔn),部署專有的光纖到面對準(zhǔn)自動對準(zhǔn)技術(shù)并通過避免碰撞技術(shù)將損壞光纖的風(fēng)險降至最低。

像AlignOpticalProbes3D這樣的獨特軟件算法(請參見下文)可優(yōu)化光纖與光纖之間的間隙以及輸入和輸出端的最大耦合功率。

沒有其他可用的解決方案使您能夠在YZ平面中校準(zhǔn)定位硬件,并準(zhǔn)備執(zhí)行邊緣耦合光學(xué)優(yōu)化。

晶圓級邊緣耦合

晶圓級邊緣耦合現(xiàn)在可以通過硬件和軟件功能的創(chuàng)新組合實現(xiàn),以對準(zhǔn)和優(yōu)化晶圓級溝槽中的光纖/陣列。

一套軟件對準(zhǔn)算法可在晶片溝槽中進行YZ優(yōu)化掃描,而帶錐狀透鏡的光纖支架可相對于晶片表面提供較小的接近角。這使得探針在溝槽中的對準(zhǔn)盡可能靠近小平面,從而以最小的溝槽尺寸最小化耦合損耗。

該解決方案意味著即使對于經(jīng)驗不足的用戶也可以輕松設(shè)置,由于獨特的光纖到面間隙對齊技術(shù),可重復(fù)獲得測量結(jié)果,并通過防撞技術(shù)降低了損壞光纖的風(fēng)險。

以下是我們現(xiàn)已提供的先進對準(zhǔn)解決方案的四個關(guān)鍵功能:

1. Measure3DCoupling–執(zhí)行連續(xù)的區(qū)域掃描,然后沿耦合軸步進移動,以構(gòu)建功率耦合的3D圖像。可用于多種目的,例如檢測光纖損壞,檢測DUT污染,測量透鏡光纖的焦距等。適用于邊緣和垂直耦合。

2. AlignOpticalProbesEdge–對多個選定的探針執(zhí)行基于視覺的間隙比對,然后執(zhí)行YZ區(qū)域掃描,同時根據(jù)需要進行重新居中。

3. AlignOpticalProbes3D–搜索輸入和輸出光纖的最佳間隙,以產(chǎn)生最大耦合功率。

4. AlignOpticalProbeGap–在XY中的單個探針上執(zhí)行基于視覺的間隙對齊,移至Z中的探針高度,并準(zhǔn)備進行YZ區(qū)域掃描。

審核編輯:符乾江

-

芯片

+關(guān)注

關(guān)注

459文章

52217瀏覽量

436569 -

晶圓

+關(guān)注

關(guān)注

52文章

5125瀏覽量

129198

發(fā)布評論請先 登錄

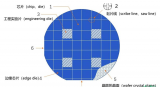

什么是晶圓級扇出封裝技術(shù)

晶圓隱裂檢測提高半導(dǎo)體行業(yè)效率

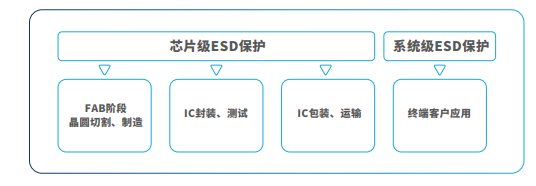

ESD技術(shù)文檔:芯片級ESD與系統(tǒng)級ESD測試標(biāo)準(zhǔn)介紹和差異分析

深入探索:晶圓級封裝Bump工藝的關(guān)鍵點

晶圓和芯片級應(yīng)用的邊緣耦合效率

晶圓和芯片級應(yīng)用的邊緣耦合效率

評論