靜電放電(ESD)問題對芯片可靠性構成嚴峻挑戰。本文介紹了芯片級ESD(HBM、CDM、MM)和系統級ESD(IEC61000-4-2)的測試標準、測試方法和測試等級,并對比分析了芯片級ESD和系統級ESD之間的差異。隨后,介紹了隔離系統中常用的ESD防護設計方法和測試注意事項。

芯片級ESD測試和系統級ESD測試共同體現了芯片在整個生命周期中的抗ESD性能,但這兩種參數的測試對象不同,對應的測試標準也不同。芯片級ESD測試以獨立芯片作為DUT,用于評估芯片本身的抗ESD能力。而系統級ESD則是以完整產品作為DUT,用于評估整套產品對外界ESD的抗干擾能力。因此,芯片內部集成的ESD保護電路存在不足以承受同等級的系統級ESD直接沖擊的可能,這也是使用系統級ESD對芯片直接進行測試更容易失效的原因。

芯片級ESD與系統級ESD測試標準介紹和差異分析技術文檔免費下載:

*附件:AN-13-0009_芯片級ESD與系統級ESD測試標準介紹和差異分析.pdf

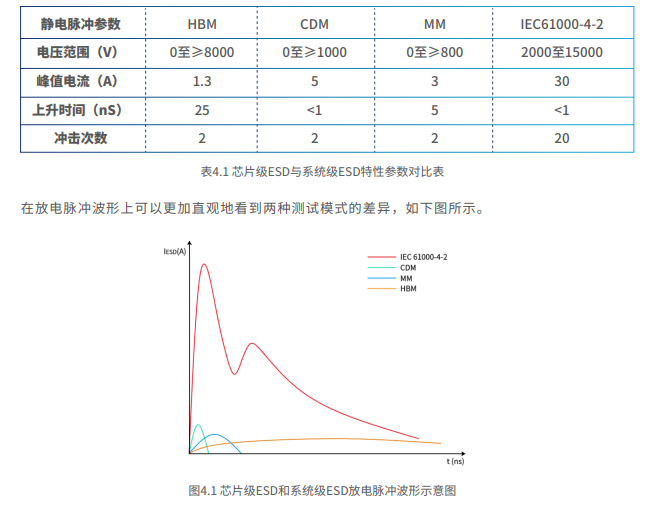

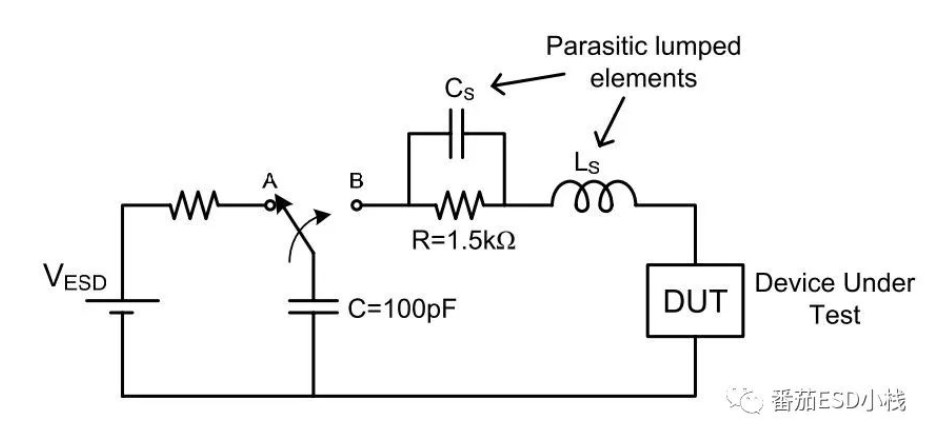

在測試方法上,芯片級ESD是在固定夾具上測試,芯片處于不上電狀態。而系統級ESD的測試則是將芯片焊接在PCB上,測試過程中芯片可能處于上電狀態,測試引腳組合也會因系統電路連接差 異 而 不 同 。 此 外 , 標 準 規 定 的 H B M 測 試 要 求 正 負 極 性 各 3 次 的 脈 沖 電 壓 測 試 , 而 I E C61000-4-2要求至少正負極性各10次的脈沖電流測試,電荷的持續累積也會加速芯片損傷。在放電脈沖波形參數上,芯片級ESD和系統級ESD相比較,脈沖電壓范圍、脈沖上升時間、脈沖電壓沖擊次數等參數均有明顯的差異,如下表所示:

可以看出,一方面,基于IEC61000-4-2標準的ESD能量遠高于HBM和CDM,以8kV接觸放電為例,系統級ESD脈沖電流峰值為30A,而HBM為1.3A,CDM為5A,系統級ESD相比于芯片級ESD對芯片內部的保護器件增加了6倍的電應力需求。另一方面,系統級ESD脈沖上升時間在0.7ns~1ns之間,而HBM的脈沖時間一般需要25ns,系統級ESD對芯片內部保護電路的響應時間提出了更加嚴格的要求,這就使得主要以HBM模型設計的保護電路無法及時響應,從而使芯片功能電路直接被損壞。

-

ESD

+關注

關注

49文章

2267瀏覽量

175143 -

ESD保護

+關注

關注

0文章

450瀏覽量

27412 -

納芯微電子

+關注

關注

0文章

70瀏覽量

2310

發布評論請先 登錄

ESD技術文檔:芯片級ESD與系統級ESD測試標準介紹和差異分析

ESD技術文檔:芯片級ESD與系統級ESD測試標準介紹和差異分析

評論