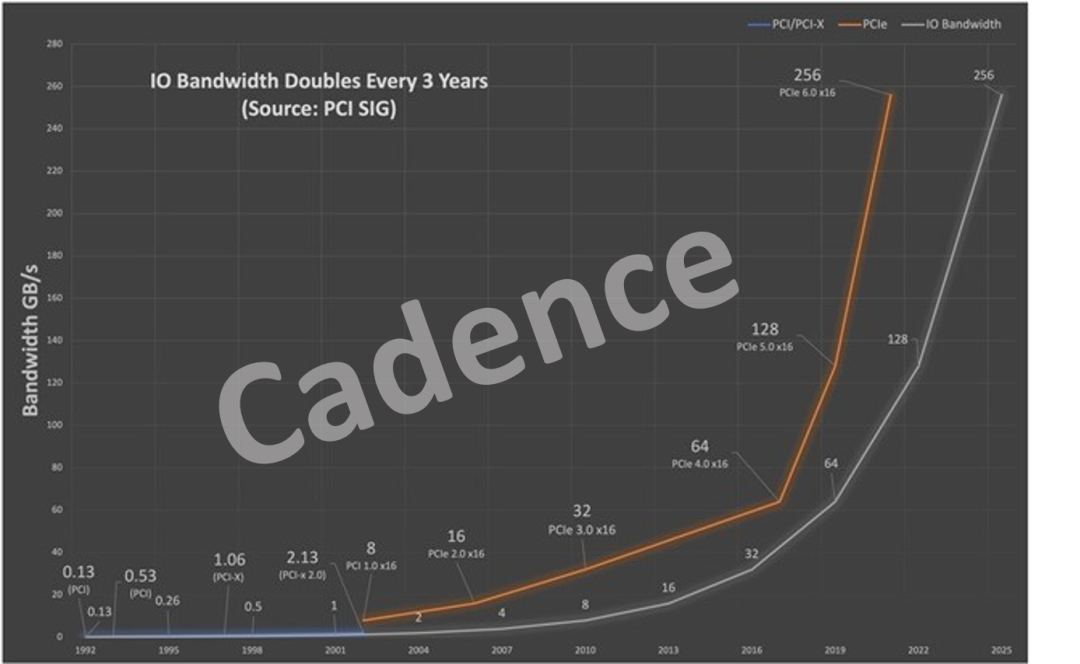

從正式發(fā)布至今,PCI Express (PCIe) 發(fā)展迅速,在現(xiàn)代數(shù)字世界中無處不在,已經成為高性能計算、人工智能/機器學習(ML)加速器、網絡適配器和固態(tài)存儲等應用不可或缺的一項技術。不僅如此,PCIe 技術近期在速度和延遲方面取得的突破讓其在存儲器架構中也獲得了廣泛應用(例如通過 PCIe/CXL 插槽連接的持久內存和 DRAM)。

人工智能/機器學習(ML)應用的變革以及企業(yè)工作負載加速遷移至云端的趨勢,持續(xù)推動數(shù)據(jù)流量前所未有的增長。為了應對未來對數(shù)據(jù)帶寬的需求,PCI-SIG 于2019 年發(fā)布了 PCIe 6.0,將數(shù)據(jù)傳輸速率翻倍至 64GT/s。最終版 PCIe 6.0 標準已于 2022年1月正式發(fā)布。

圖1:IO 帶寬增長預測和 PCIe 標準的演化

PCIe 6.0 的主要挑戰(zhàn)

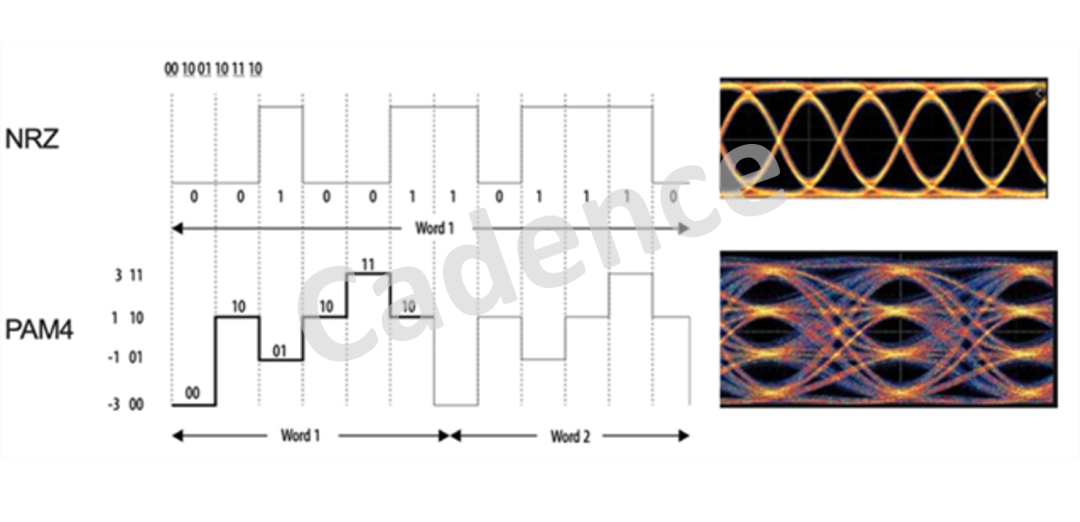

將 I/O 帶寬從 PCIe 5.0 的 32GT/s 翻倍至 64GT/s 給信號完整性(SI)帶來了巨大挑戰(zhàn)。PCIe 向后兼容的需求必須持續(xù)支持 PCB、連接頭和擴展卡等傳統(tǒng)通道。數(shù)據(jù)速率為 32GT/s 且采用不歸零制(NRZ)編碼時,傳統(tǒng)通道的插入損耗總和在奈奎斯特頻率(16GHz)下可達到36dB以上;當速率提升至64GT/s NRZ 時,奈奎斯特頻率翻倍至 32GHz,通道的頻率相關損耗將增加到 70dB 以上。如此的全通道信號損失將令噪音完全無法識別,傳輸?shù)臄?shù)據(jù)將無法被有效還原。

PAM4 加持 PCIe

將信號調制模式從非歸零編碼(NRZ)改至四電平脈沖幅度調制(PAM4)是 PCIe 6.0 克服通道信號損失挑戰(zhàn)的方法。

PAM4 是一種多電平信號傳輸技術,每個單位時間(UI)傳輸2比特,而 NRZ 每個單位時間僅傳輸1比特(見圖2)。采用 PAM4 信號調制技術的PCIe 6.0 每個 UI 可以傳輸2比特數(shù)據(jù),數(shù)據(jù)速率在奈奎斯特頻率不變的情況下增加一倍,成為 PCIe 6.0 的一大優(yōu)勢。通道損失也因此與 PCIe 5.0 一樣可控。

圖2:PAM4 信號調制

然而,升級至采用 PAM4 信號調制的 PCIe 版本還需要解決一系列挑戰(zhàn),并應對因此導致的復雜性上升。幸運的是,Cadence 對 PAM4 并不陌生。早在 2017 年,Cadence 就通過對 Nusemi 公司的收購開始研發(fā)112Gb/s 的 PAM4 技術。

今天,Cadence 已經是多個先進 FinFET 節(jié)點下 112G/56G PAM4 SerDes IP 的領先供應商,客戶使用我們的 IP 已經開發(fā)出多項成功的芯片設計。

協(xié)議更新,為效率而生

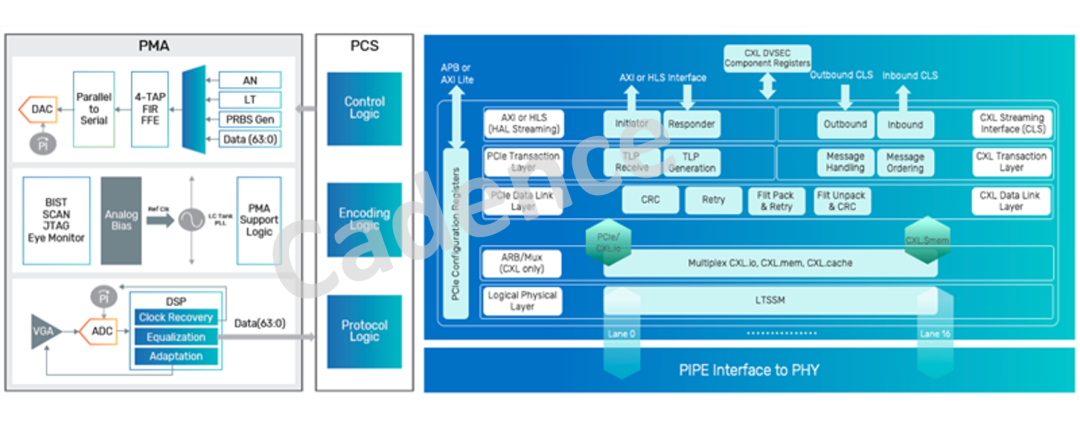

PIPE 到控制器的接口也升級到了 6.0 版本,延遲進一步降低。

PCIe 6.0 標準引入了流控制單元的概念(FLIT),與 PAM4 所需的前向糾錯(FEC)高效協(xié)同,為采用最常見配置的主流負載提供更低的延遲。

PCIe 前代版本通過動態(tài)鏈路帶寬和低功耗狀態(tài)實現(xiàn)節(jié)能。但在此過程中,動態(tài)鏈路帶寬會干擾數(shù)據(jù)流的傳輸。PCIe 6.0 采用全新的低功耗狀態(tài) L0p,可在不干擾數(shù)據(jù)流的前提下允許功耗相對帶寬的按比例調整。

Cadence 針對 PCIe 6.0 的完整 IP 解決方案

圖3:Cadence 的 PCIe PHY 和控制器解決方案

Cadence 致力于引領行業(yè)采用最新的 PCIe 6.0 標準,用 PCIe 6.0 IP 解決方案應對前沿領域快速變革的技術需求。

過去 20年,Cadence 一直是 PCIe PHY 和控制器的領先供應商。采用 Cadence 領先的 PAM4 技術以及經過驗證的112G/56G PAM4 以太網 PHY IP,結合在 PCIe 領域深厚的經驗,Cadence 致力于為市場提供最先進的 PCIe 6.0 PHY 和控制器 IP。

關于 Cadence

Cadence 在計算軟件領域擁有超過 30 年的專業(yè)經驗,是電子系統(tǒng)設計產業(yè)的關鍵領導者。基于公司的智能系統(tǒng)設計戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產品,助力電子設計概念成為現(xiàn)實。Cadence 的客戶遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計算、5G 通訊、汽車、移動、航空、消費電子、工業(yè)和醫(yī)療等最具活力的應用市場交付從芯片、電路板到完整系統(tǒng)的卓越電子產品。Cadence 已連續(xù)八年名列美國財富雜志評選的 100 家最適合工作的公司。如需了解更多信息,請訪問公司網站 cadence.com。

2022 Cadence Design Systems, Inc. 版權所有。在全球范圍保留所有權利。Cadence、Cadence 徽標和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標志均為 Cadence Design Systems, Inc. 的商標或注冊商標。所有其他標識均為其各自所有者的資產。

原文標題:成熟的PCIe 6.0 IP可極大降低復雜系統(tǒng)開發(fā)難度

文章出處:【微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

控制器

+關注

關注

114文章

16979瀏覽量

182995 -

Cadence

+關注

關注

67文章

965瀏覽量

143860 -

PCIe

+關注

關注

16文章

1324瀏覽量

84707

原文標題:成熟的PCIe 6.0 IP可極大降低復雜系統(tǒng)開發(fā)難度

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

Cadence推出HBM4 12.8Gbps IP內存系統(tǒng)解決方案

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內存IP系統(tǒng)解決方案

核芯互聯(lián)推出面向PCIe 5.0/6.0的32/64Gbps高速重驅動器芯片CLH3264R

是德科技PCIe 6.0發(fā)射機合規(guī)性測試解決方案

詳解PCIe 6.0中的FLIT模式

PCIe 6.0時代的測試挑戰(zhàn)和解決方案

Cadence宣布收購Secure-IC

加特蘭集成Cadence DSP,升級汽車成像雷達解決方案

PCIe信號完整性問題解決方案

Cadence展示完整的PCIe 7.0 IP解決方案

新思科技PCIe 7.0驗證IP(VIP)的特性

如何簡化PCIe 6.0交換機的設計

Cadence針對PCIe 6.0的完整IP解決方案

Cadence針對PCIe 6.0的完整IP解決方案

評論