核芯互聯(lián)CLRD320:高速互連解決方案

在數(shù)據(jù)中心、人工智能和高性能計(jì)算需求爆發(fā)的今天,高速信號(hào)傳輸?shù)姆€(wěn)定性和效率成為系統(tǒng)設(shè)計(jì)的核心挑戰(zhàn)。核芯互聯(lián)推出的CLRD320八通道redriver(線性轉(zhuǎn)接驅(qū)動(dòng)器)芯片,憑借多項(xiàng)技術(shù)創(chuàng)新,為PCIe 5.0、PCIe 6.0、CXL 2.0等超高速接口提供了更優(yōu)的國(guó)產(chǎn)化解決方案,助力企業(yè)突破信號(hào)完整性與系統(tǒng)能效的瓶頸。

CLRD320完全采用國(guó)產(chǎn)化設(shè)計(jì),封裝上與DS320PR810的完全Pin 2 Pin兼容,提供更優(yōu)秀的增益和串?dāng)_抑制。

什么是redriver芯片

Redriver芯片(重驅(qū)動(dòng)器芯片)是一種用于高速信號(hào)傳輸?shù)年P(guān)鍵器件,主要功能是補(bǔ)償信號(hào)在傳輸過(guò)程中的衰減和失真,提升信號(hào)完整性。

基本定義

Redriver是一種模擬信號(hào)調(diào)理芯片,通過(guò)均衡器(如CTLE)和信號(hào)放大器來(lái)增強(qiáng)高頻信號(hào)的幅度,抵消傳輸線(如PCB走線、電纜)導(dǎo)致的頻率相關(guān)衰減。它不涉及協(xié)議處理,僅作用于物理層,因此具有低延遲(<5ns)和低功耗的優(yōu)勢(shì)。

工作原理

- 信號(hào)補(bǔ)償:在發(fā)送端,Redriver通過(guò)連續(xù)時(shí)間線性均衡器(CTLE)補(bǔ)償信號(hào)的高頻損耗,再通過(guò)增益放大恢復(fù)信號(hào)幅度;

- 預(yù)加重/去加重:部分型號(hào)支持預(yù)加重技術(shù),提前增強(qiáng)信號(hào)的高頻分量,以對(duì)抗傳輸中的衰減;

- 眼圖優(yōu)化:通過(guò)上述技術(shù),Redriver能將原本閉合的信號(hào)“眼圖”重新張開(kāi),降低誤碼率。

典型應(yīng)用場(chǎng)景

- PCIe/USB/HDMI/以太網(wǎng)接口:延長(zhǎng)高速接口(如PCIe 4.0/5.0)的信號(hào)傳輸距離,解決服務(wù)器、AI加速卡等場(chǎng)景中的鏈路損耗問(wèn)題;

- 數(shù)據(jù)中心與存儲(chǔ):用于NVMe SSD、全閃存陣列等設(shè)備,確保高速存儲(chǔ)協(xié)議(如SATA/SAS)的穩(wěn)定性;

- 車(chē)載與工業(yè)電子:工業(yè)級(jí)Redriver可支持車(chē)載以太網(wǎng)、傳感器數(shù)據(jù)匯聚等嚴(yán)苛環(huán)境下的信號(hào)傳輸。

與reimter的技術(shù)、市場(chǎng)應(yīng)用及成本對(duì)比分析

信號(hào)處理機(jī)制

- Redriver:本質(zhì)是模擬信號(hào)放大器,通過(guò)連續(xù)時(shí)間線性均衡(CTLE)和增益級(jí)補(bǔ)償信道損耗,僅放大信號(hào)但無(wú)法消除累積抖動(dòng)和噪聲。其延遲極低(約100ps),但無(wú)法恢復(fù)數(shù)據(jù)時(shí)鐘,不參與協(xié)議交互(如PCIe鏈路訓(xùn)練)。

- Retimer:采用數(shù)字+模擬混合架構(gòu),集成時(shí)鐘數(shù)據(jù)恢復(fù)(CDR)和判決反饋均衡(DFE),能完全再生信號(hào)并消除抖動(dòng),支持協(xié)議層交互(如PCIe均衡訓(xùn)練)。其延遲較高(約64ns),但可重置鏈路時(shí)序預(yù)算,適用于復(fù)雜信道環(huán)境

均衡能力與協(xié)議支持

- Redriver僅支持CTLE和預(yù)加重,無(wú)法處理反射和串?dāng)_(核芯互聯(lián)CLRD320中加入了動(dòng)態(tài)串?dāng)_抑制電路,可以有效的抑制串?dāng)_),信號(hào)噪聲可能被放大。

- Retimer通過(guò)DFE和Tx FIR均衡器,可動(dòng)態(tài)調(diào)整參數(shù)適應(yīng)信道特性,支持PCIe、CXL等復(fù)雜協(xié)議,且能消除串?dāng)_影響。

信號(hào)完整性

- Redriver在中短距離場(chǎng)景下性價(jià)比高,但長(zhǎng)距離傳輸時(shí)眼圖惡化風(fēng)險(xiǎn)大。

- Retimer通過(guò)CDR再生信號(hào),可延長(zhǎng)傳輸距離,并保持高質(zhì)量眼圖。

CLRD320的技術(shù)突破:攻克高速互連三大核心挑戰(zhàn)

-

32Gbps超高速信號(hào)完整性優(yōu)化

CLRD320在支持PCIe 5.0(32Gbps)速率的同時(shí),通過(guò)多級(jí)自適應(yīng)均衡技術(shù),將CTLE(連續(xù)時(shí)間線性均衡)在16GHz下的增益提升至24dB(較同類(lèi)產(chǎn)品提升9%),有效補(bǔ)償長(zhǎng)達(dá)40英寸的FR4 PCB走線損耗。其創(chuàng)新的動(dòng)態(tài)串?dāng)_抑制電路可將通道間串?dāng)_降低至-45dB以下,確保在密集布線場(chǎng)景下的眼圖張開(kāi)度。 -

亞納秒級(jí)超低延遲設(shè)計(jì)

針對(duì)AI訓(xùn)練、金融交易等對(duì)實(shí)時(shí)性要求嚴(yán)苛的場(chǎng)景,CLRD320采用全差分線性驅(qū)動(dòng)架構(gòu),將端到端傳輸延遲壓縮至85ps(行業(yè)平均100ps),并通過(guò)獨(dú)特的時(shí)鐘樹(shù)優(yōu)化技術(shù),實(shí)現(xiàn)通道間延遲偏差<5ps,顯著降低系統(tǒng)時(shí)序不確定性。 -

智能電源管理與熱控制

在3.3V單電源供電下,CLRD320集成多級(jí)動(dòng)態(tài)電壓調(diào)節(jié)模塊,可自適應(yīng)負(fù)載波動(dòng),將電源噪聲抑制能力提升至30dB@500MHz,且低功耗的設(shè)計(jì)使得芯片無(wú)需外置散熱器即可在-40℃~105℃寬溫范圍內(nèi)穩(wěn)定運(yùn)行。

技術(shù)優(yōu)勢(shì):性能全面升級(jí),設(shè)計(jì)無(wú)縫遷移

| 特性 | CLRD320 | 競(jìng)品典型值 |

|---|---|---|

| 最大數(shù)據(jù)速率 | 32Gbps(兼容PCIe 5.0/CXL 2.0) | 32Gbps |

| CTLE增益@16GHz | 24dB | 22dB |

| 附加隨機(jī)抖動(dòng)(RJ) | 65fs RMS | 75fs RMS |

| 端到端延遲 | 85ps | 100ps |

| 單通道功耗 | 145mW(@32Gbps全負(fù)載) | 160mW |

| 溫度范圍 | -40℃~105℃ | -40℃~85℃ |

此外,CLRD320提供三重配置模式:

? Pin Strap模式:通過(guò)電阻配置快速啟用預(yù)設(shè)優(yōu)化參數(shù),縮短開(kāi)發(fā)周期

? I2C/SMBus接口:支持實(shí)時(shí)通道級(jí)EQ調(diào)節(jié)與狀態(tài)監(jiān)控

? EEPROM自加載:可實(shí)現(xiàn)多設(shè)備級(jí)聯(lián)配置,適用于x24寬鏈路拓?fù)?/p>

應(yīng)用場(chǎng)景:賦能下一代算力基礎(chǔ)設(shè)施

-

AI服務(wù)器與異構(gòu)計(jì)算

在GPU/FPGA集群中,CLRD320可延長(zhǎng)PCIe 5.0信號(hào)傳輸距離至1.5米(通過(guò)電纜),解決多機(jī)柜擴(kuò)展時(shí)的信號(hào)衰減問(wèn)題,同時(shí)支持CXL 2.0內(nèi)存池化低延遲互聯(lián)。 -

全閃存存儲(chǔ)與數(shù)據(jù)中心網(wǎng)絡(luò)

針對(duì)NVMe-oF架構(gòu),CLRD320的-50dB回波損耗特性可優(yōu)化25G/100G以太網(wǎng)物理層連接,確保RDMA零拷貝傳輸?shù)姆€(wěn)定性,助力存儲(chǔ)時(shí)延降至微秒級(jí)。 -

自動(dòng)駕駛域控制器

CLRD320,可在車(chē)載環(huán)境下實(shí)現(xiàn)多傳感器數(shù)據(jù)的低抖動(dòng)匯聚,支持10Gbps車(chē)載以太網(wǎng)TSN實(shí)時(shí)通信。 -

5G基帶與邊緣計(jì)算

在O-RAN前傳網(wǎng)絡(luò)中,CLRD320的高抗噪特性可有效抑制毫米波頻段干擾,確保CPRI/eCPRI接口在復(fù)雜電磁環(huán)境中的可靠性。

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

8637瀏覽量

149111 -

PCIe

+關(guān)注

關(guān)注

16文章

1324瀏覽量

84710 -

核芯互聯(lián)

+關(guān)注

關(guān)注

0文章

30瀏覽量

1957

原文標(biāo)題:核芯互聯(lián)發(fā)布支持PCIe 5.0/6.0的32/64Gbps的高速redriver芯片CLRD320

文章出處:【微信號(hào):gh_0dbe96735e9d,微信公眾號(hào):核芯互聯(lián)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

德州儀器(TI)推出面向IGBT與MOSFET的隔離式柵極驅(qū)動(dòng)器

Maxim推出面向汽車(chē)投影儀的激光器驅(qū)動(dòng)器MAX3601

MACOM宣布推出面向長(zhǎng)距離、城域和數(shù)據(jù)中心互連應(yīng)用的四通道64G線性調(diào)制器驅(qū)動(dòng)芯片

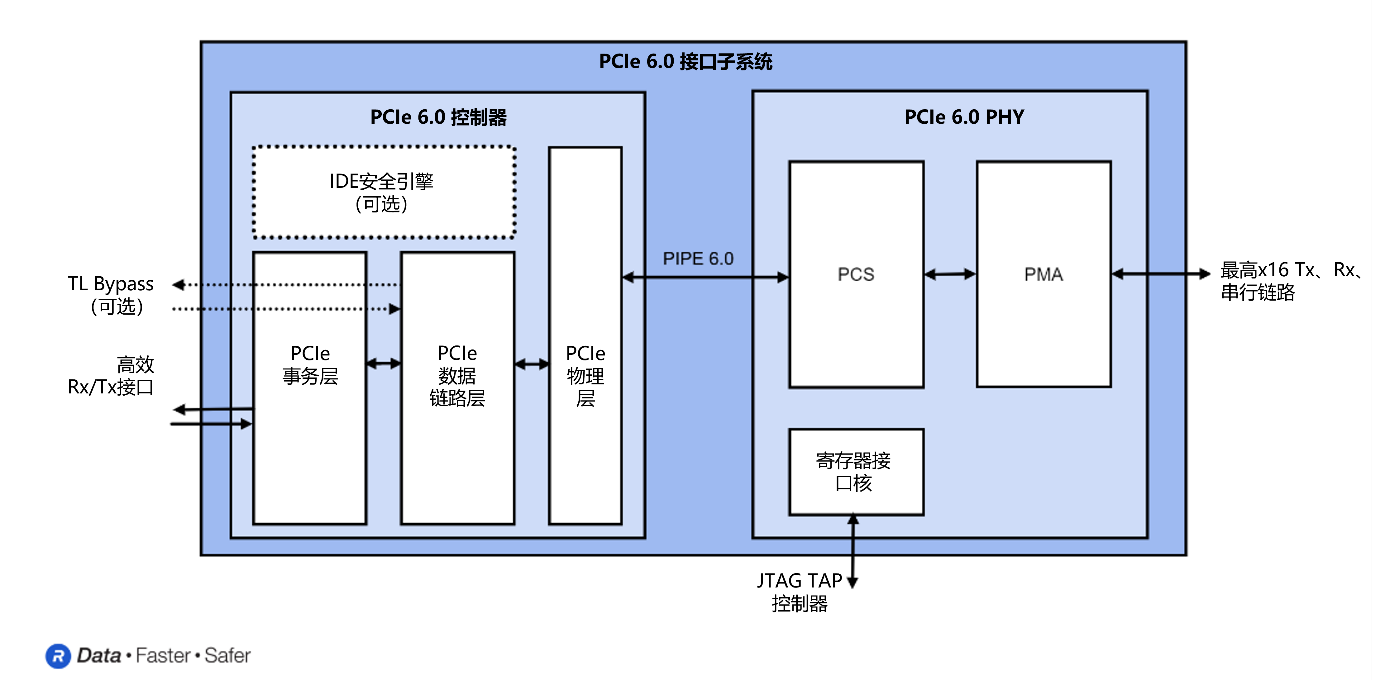

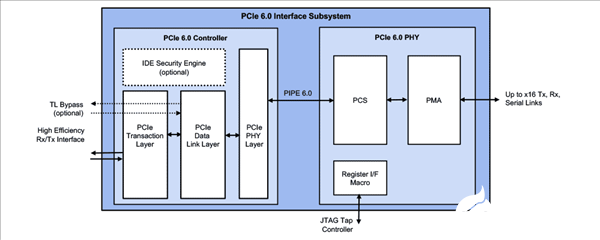

Rambus推出面向高性能數(shù)據(jù)中心和人工智能SoC的PCIe 6.0接口子系統(tǒng)

IT66318--HDMI2.0(6.0 Gbps)重定時(shí)緩沖器,為HDMI 優(yōu)化信號(hào)

MACOM宣布推出面向100G和400G PAM-4應(yīng)用的單通道和四通道線性EML驅(qū)動(dòng)器系列

Rambus推出全球首個(gè)PCIe 6.0接口子系統(tǒng) 面向大數(shù)據(jù)與AI領(lǐng)域

核芯互聯(lián)推出符合DB2000QL及PCIe Gen5和Gen 6標(biāo)準(zhǔn)的低抖動(dòng)時(shí)鐘緩沖器CLB2000

核芯互聯(lián)推出全新20路LP-HCSL差分時(shí)鐘緩沖器CLB2000

AI和數(shù)據(jù)中心:PCIe 6.0,你是懂加速的

核芯互聯(lián)推出支持PCIe Gen 6的時(shí)鐘發(fā)生器CLG440

下一代PCIe5.0 /6.0技術(shù)熱潮趨勢(shì)與測(cè)試挑戰(zhàn)

DS320PR1601 32Gbps 16通道PCIe 5.0、CXL 2.0線性轉(zhuǎn)接驅(qū)動(dòng)器數(shù)據(jù)表

核芯互聯(lián)推出面向PCIe 5.0/6.0的32/64Gbps高速重驅(qū)動(dòng)器芯片CLH3264R

核芯互聯(lián)推出面向PCIe 5.0/6.0的32/64Gbps高速重驅(qū)動(dòng)器芯片CLH3264R

評(píng)論