時間交錯技術可使用多個相同的 ADC(文中雖然僅討論了 ADC,但所有原理同樣適用于 DAC 的時間交錯特性),并以比每一個單獨數據轉換器工作采樣速率更高的速率來處理常規采樣數據序列。簡單說來,時間交錯(IL)由時間多路復用 M 個相同的 ADC 并聯陣列組成。

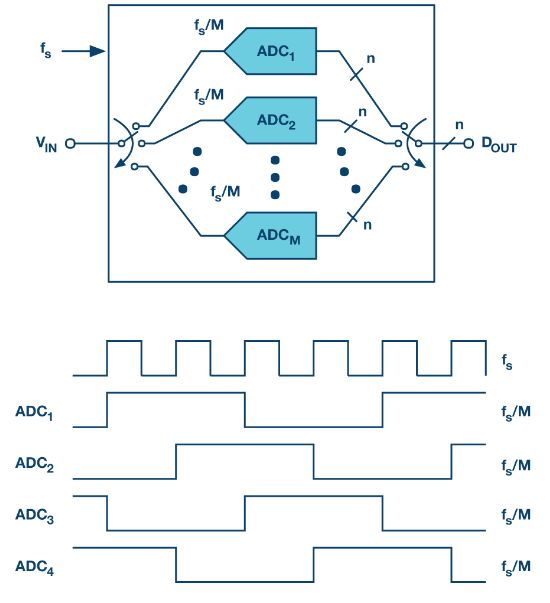

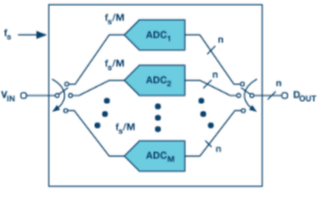

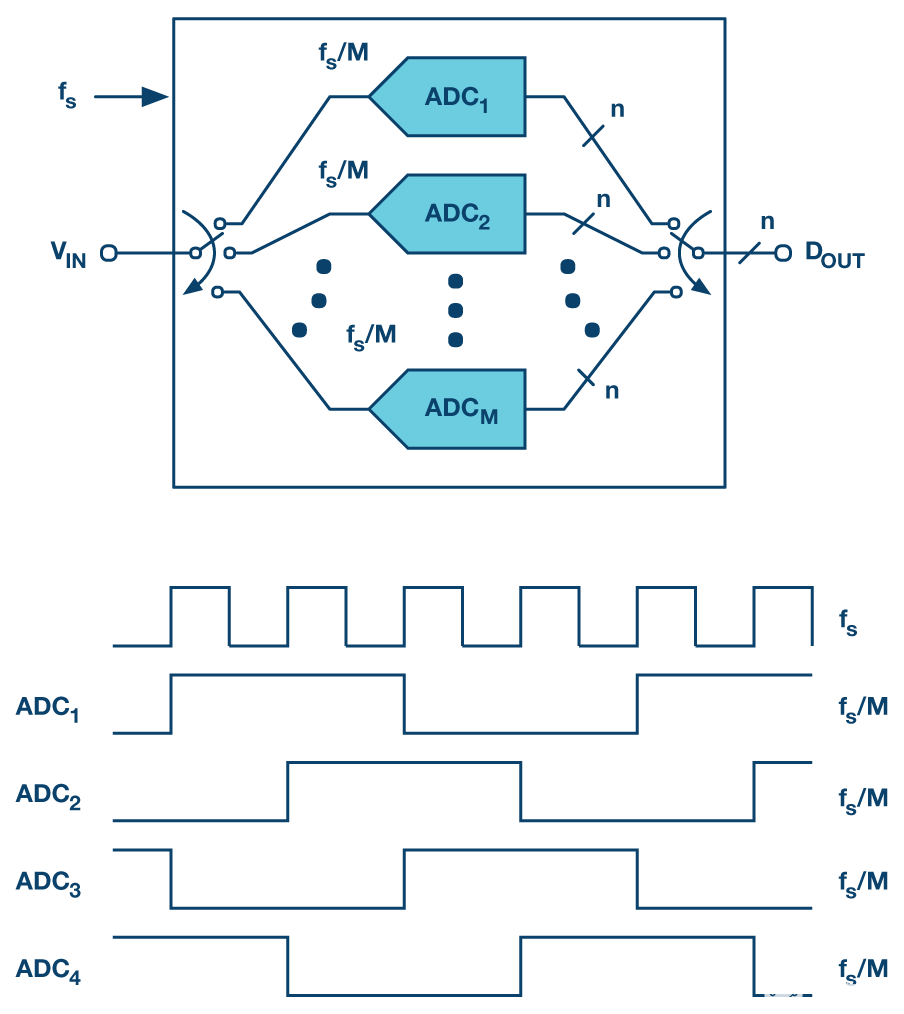

如圖 1 所示。這樣可以得到更高的凈采樣速率 fs(采樣周期 Ts = 1/fs),哪怕陣列中的每一個 ADC 實際上以較低的速率進行采樣(和轉換),即 fs/M。因此,舉例而言,通過交錯四個 10 位/100 MSPS ADC,理論上可以實現 10 位/400 MSPS ADC。

圖1. M次交錯的n位ADC陣列每一個ADC的采樣速率為fs/M,得到的時間交錯ADC采樣速率為fs。M = 4的時鐘方案示例在該圖下半部分顯示。

為了更好地理解 IL 原理,圖 1 中一個模擬輸入 VIN (t) 以 M 個 ADC 進行采樣,其結果為組合數字輸出數據序列 DOUT。ADC1 最先采樣 VIN (t0) 并開始將其轉換為n位數字信號。Ts 秒后,ADC2 將采樣 VIN (t0+Ts) 并開始將其轉換為n位數字信號。接著,Ts 秒后,ADC3 將采樣 VIN (t0 +2Ts),以此類推。ADCM 完成 VIN (t0 +(M-1)×Ts) 采樣后,開始下一個采樣周期,并從 ADC1 采樣 VIN (t0 +M×Ts) 開始,依次進行下去。

由于ADC順序輸出n位數據且輸出順序與剛才描述的采樣操作順序一致,這些數字n位字由同一張圖右側的解復用器所采集。這里獲取的是重新組合的數據輸出序列 DOUT (t0 + L),DOUT (t0 +L + Ts),DOUT (t0 + L + 2Ts),... 。L 表示每一個單獨ADC的固定轉換時間,而該重新組合的數據序列是一個 n 位數據序列,采樣速率為 fs。因此,雖然各個ADC(通常稱為“通道”)為 n 位 ADC 且采樣速率為 fs/M,但整體等于采樣速率為 fs的單個 n 位 ADC,而我們將其稱為時間交錯 ADC(與通道相區別)。輸入本質上是分隔開的,并由陣列中的 ADC 單獨處理,然后在輸出端連續重組,以便構成輸入 VIN 的高數據速率表示 DOUT。

這種強大的技術在實際使用時存在一些難題。一個重要的問題是來自通道的M數據流經過數字組裝后重構原始輸入信號 VIN。如果我們看一下頻譜 DOUT;除了看到 VIN 的數字信號以及模數轉換引入的失真,我們還將看到額外的和大量的雜散成分,稱為“交錯雜散”(或簡稱為 IL 雜散);IL 雜散既沒有多項式類型失真的簽名——比如較高次信號諧波(2次,3次,等等)——也沒有量化或 DNL 誤差簽名。IL 偽像可視為時域固定碼噪聲的一種形式,由通道中的模擬損害引起,因為在交錯過程中采用分隔轉換信號進行調制并出現在最終的數字化輸出 DOUT。

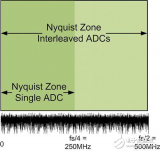

讓我們分析一個簡單的示例,了解可能會發生什么情況。考慮頻率 fIN 下正弦輸入 VIN 的雙路交錯 ADC 情況。假定 ADC1 具有增益 G1,ADC2 具有差分增益 G2。在這種雙路 IL ADC中,ADC1 和 ADC2 將交替采樣 VIN。因此,如果 ADC1 轉換偶數樣本,而 ADC2 轉換奇數樣本,則所有 DOUT 偶數數據的幅度都將由 G1設置,而所有 DOUT 奇數數據的幅度都將由G2設置。然后,DOUT 不僅包含 VIN,還包括一些多項式失真,但它受到 G1 和G2 的交替放大,就好像我們采用頻率為 fs/2 的方波對 VIN 進行幅度調制。這樣做會引入更多雜散成分。特別地,DOUT 在 fs/2 – fIN 頻率處會包含“增益雜散”;并且不幸的是,該雜散的頻率會跟蹤輸入fIN,且位于交錯 ADC 的第一奈奎斯特頻段內(即在 fs/2 內),而在所有其它奈奎斯特頻段內也會存在混疊。該交錯雜散的功率/幅度取決于兩個增益 G1和G2 之間的凈差。換言之,它取決于增益誤差失配。而最終,它取決于輸入 VIN 自身的幅度。

如果輸入并非簡單正弦波,而是真實應用中的全頻帶限幅信號,那么“增益雜散”就不只是干擾音了,而是頻帶限幅輸入信號自身的完整調節鏡像,出現在奈奎斯特頻段內。這在一定程度上抵消了交錯帶來的帶寬增加的優勢。

雖然上例中我們僅考慮了通道間的增益誤差失配,其它損害也會引起交錯雜散。失調失配(通道失調之間的差)引起固定頻率的信號音(“失調雜散”),功率與失調失配成正比。當某些通道比預定順序更早或更晚采樣某位時,便發生采樣時間偏斜。它會引入“時間雜散”,其頻率與增益雜散全一致(并疊加同樣的幅度),但功率會隨著 fIN 的增加以及輸入幅度的增加而不斷加強。各通道之間的帶寬失配會引入更多的雜散成分,頻率取決于 fIN,并且正如時間雜散,雜散功率不僅隨著輸入幅度,而且還會隨著fIN自身而逐步增加。再次強調,無論何種情況,輸出頻譜下降的程度并不取決于通道損害的絕對值(失調、增益、時序、頻段),而是取決于通道之間的相對失配或通道之差。

雖然時間交錯的基本技術存在已有幾十年,但IL可在何種程度上保持最小化則將其過去的適用性限制于低分辨率轉換器。然而,最近在通道失配校準方面以及抑制殘留IL雜散成分方面的進步已經可以實現全集成、極高速、12/14/16 位 IL ADC。

這種情況下,我們需要對交錯進行分類。我們一般將兩個交錯通道稱為“乒乓”工作。然后,當我們描述較少通道數的情況(比如 3 通道至4通道),以及大量通道的情況時(比如超過 4 個通道,通常達到 8 個或更多),我們還區分了“輕度交錯”和“重度交錯”。

乒乓(雙路)交錯

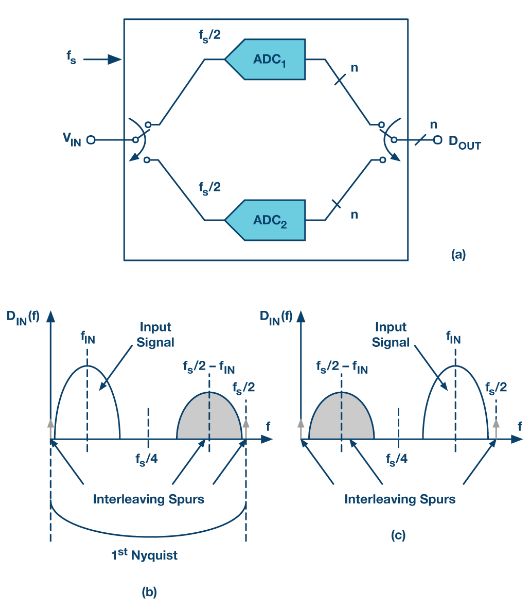

當我們只是交錯兩個通道以便使采樣速率翻倍時,我們將其稱為“乒乓”,如圖 2 (a) 中的框圖所示。這是一種最簡單的情況,它有一些有趣和有用的特性。這種情況下,在交錯ADC的第一奈奎斯特頻段內,交錯雜散位于直流、fs/2 和 fs/2 – fIN 處。因此,如果輸入信號VIN是一個對中至fIN的窄帶信號——如圖 2 (b) 中的第一奈奎斯特輸出頻譜所示——交錯雜散包含直流處的失調雜散、fs/2 處的另一個失調失配雜散以及對中至 fs/2 – fIN 的增益和時序雜散鏡像,看上去就像輸入自身的一個放大復制版本。

圖2.問(a)乒乓方案

(b)窄帶輸入信號位于fs/4以下時的輸出頻譜

(c)此時輸入信號位于fs/4和奈奎斯特頻率fs/2之間

如果輸入信號 VIN(f) 完全位于 0 和 fs/4 之間——如圖 2 (b) 所示——那么交錯雜散不與數字化輸入頻率重疊。此時,壞消息是我們只能數字化半個奈奎斯特頻段,就好比只有一個時鐘為 fs/2 的單通道,雖然我們依舊消耗至少兩倍于該單個通道的功耗。奈奎斯特頻段上限的交錯雜散鏡像可在數字化之后通過數字濾波手段抑制,無需進行模擬損害校正。

但好消息是由于乒乓ADC時鐘為 fs,數字化輸出得益于動態范圍內的 3 dB 處理增益。此外,與使用時鐘為 fs/2 的單個 ADC 相比,乒乓 ADC 放寬了抗混疊濾波器設計要求。

如果窄帶信號位于第一奈奎斯特頻段的上半部,則所有考慮因素都適用,如圖 2 (c) 所示,因為交錯鏡像雜散移至奈奎斯特頻段的下半部分。再次強調,增益和時序雜散可在濾波數字化之后通過數字手段抑制。

最后,輸入信號和交錯雜散的頻率將會重疊,并且一旦輸入信號頻率位置跨過 fs/4 線,交錯鏡像就會破壞輸入頻譜。這種情況下,恢復所需輸入信號將是不可能的,而乒乓方案不可用。當然,除非通道間匹配足夠緊密,使得交錯雜散成分對于應用來說達到可以接受的低程度,或者引入校準來降低導致IL鏡像的原因。

總之,頻率規劃和某些數字濾波可以恢復乒乓方案中的窄帶數字化輸入,哪怕存在通道失配。雖然轉換器功耗相比使用單個時鐘為 fs/2 的 ADC 時基本翻了個倍,但乒乓方案提供了 3 dB 處理增益,同時放寬了抗混疊要求。

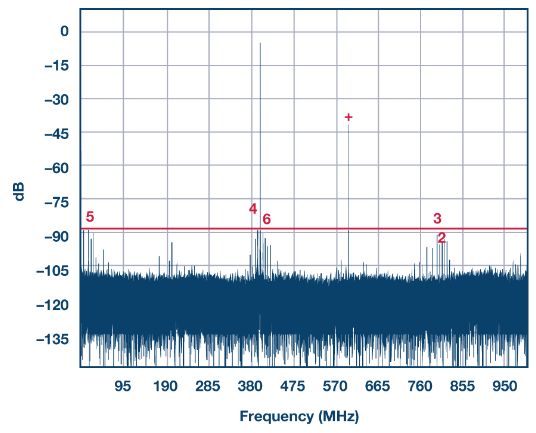

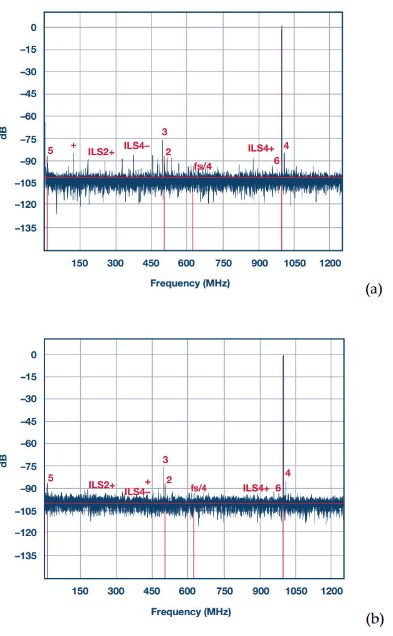

采用乒乓方案并且無任何通道失配校正的一個示例,以及其產生的交錯雜散見圖 3。在該例中,兩個雙通道 14位/1 GSPS ADC AD9680 以交替乘以正弦波的速率進行采樣,從而返回單個組合輸出數據流,速率為 2 GSPS。當我們查看該乒乓方案輸出頻譜的第一奈奎斯特頻段時(位于直流和 1 GHz 之間),可以看到輸入音,它是 fIN = 400 MHz 時位于左側的強音;我們還能看到在 fs/2 – fIN = 2G/2 – 400 M = 600 MHz 處有較強的增益/時序失配雜散。由于通道本身的失真以及其它損害,我們還能看到一系列其它信號音,但都低于–90 dB 線。

圖3. 乒乓方案的2 GSPS輸出數據組合頻譜,采用兩個AD9680在1 GSPS時鐘下獲取,采樣相移為180°。

更高次交錯

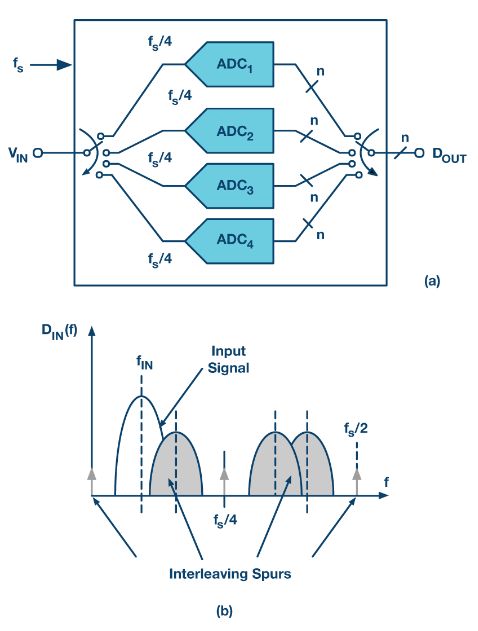

當具有兩個以上通道時,上文所說的頻率規劃就不那么實用了。我們無法將交錯雜散的位置限定在奈奎斯特頻段的某一小部分。比如考慮四路交錯 ADC 的情況,如圖 4(a) 所示。此時,失調失配會提高直流、fs/4 和 fs/2 時的信號音,而增益和時序交錯鏡像位于fs/4 – fIN、fs/4 + fIN和fs/2 – fIN。交錯 ADC 輸出頻譜的一個示例請參見圖 4 (b)。很明顯,除非輸入位于fs/8以內的帶寬之內,否則無論 fIN 的位置如何,輸入都會與部分交錯雜散重疊,并且如果輸入是一個極端窄帶信號,那么我們不應當嘗試使用寬帶交錯 ADC將其數字化。

在這種情況下,我們需要最大程度降低 IL 雜散功率,以便獲得完整的奈奎斯特頻譜和更干凈的頻譜。為了達到這個目的,我們使用校準技術來補償通道間失配。校正失配的影響后,最終的 IL 雜散功率會下降。SFDR 和 SNR 都會得益于該雜散功率的下降。

補償方法受限于失配可測量并最終校正的精度。除了校準所能達到的水平外,為了進一步抑制殘留雜散,還可間歇性隨機打亂通道輸入采樣的順序。這樣做之后,前面討論的由于未校準失配而產生的轉換輸入信號調制效果將從固定碼噪聲轉換為偽隨機噪聲。因此,IL音和干擾周期碼轉換為偽隨機噪聲類成分,并疊加至轉換器量化噪底而消失,或者至少將干擾雜散鏡像和信號音加以擴散。此時,與 IL 雜散成分有關的功率疊加至噪底功率。因此,雖然改善了失真,但 SNR 可能下降,下降量為 IL 雜散功率加上噪聲。SNDR (SINAD) 基本上沒有變化,因為它由失真、噪聲和隨機化組成;它只是將IL貢獻因素從一個成分(失真)轉移到另一個成分(噪聲)。

圖4. (a)四路交錯ADC

(b)對應顯示交錯雜散的第一奈奎斯特輸出頻譜

交錯 ADC 的示例

AD9625 是一個12位/2.5GSPS 三路交錯 ADC。對三個通道之間的失配進行校準,以便最大程度減少交錯雜散。圖 5(a) 所示是一個輸入接近 1 GHz的輸出頻譜示例。在該頻譜中,除了約為 1 GHz的輸入音外,還可以看到通道在 500 MHz 附近存在 2 次和 3 次諧波失真,并在基頻處存在 4 次諧波失真。交錯失配校準可大幅降低交錯雜散的功耗,并且在整個頻譜中可以看到大量的額外殘留的較小雜散音。

為了進一步減少這些殘留雜散成分,引入了通道隨機化。加入了第四個校準通道,然后將四個通道變為三路交錯,并通過間歇性將交錯通道與第四個更換,實現隨機改變順序。這就好比人們可以像耍雜技那樣將三根柱子投向空中,然后每一次都更換第四根。這樣做之后,可使殘留交錯雜散功率隨機化,然后擴散到噪底。如圖 5(b) 所示,經過通道隨機化之后,交錯雜散幾乎消失了,而噪聲功率卻只略為增加,因而 SNR 降低 2dB。當然,需要注意的是,雖然圖 5(b) 中的第二個頻譜比失真音遠為干凈,但隨機無法影響 2 次、3 次 和4 次諧波,因為這些諧波不是交錯雜散。

圖5. AD9625的輸出頻譜,時鐘為2.5 GSPS,輸入音接近1 GHz。

(a)順序三路交錯;SNR = 60 dBFS,SFDR = 72 dBc,受限于3次諧波,接近500 MHz;然而,整個頻譜中可見大量交錯雜散。

(b)三路交錯,隨機通道置亂;SNR = 58 dBFS,而SFDR = 72 dBc依然由3次諧波決定,通過將功率擴散到噪底而消除了所有交錯雜散。

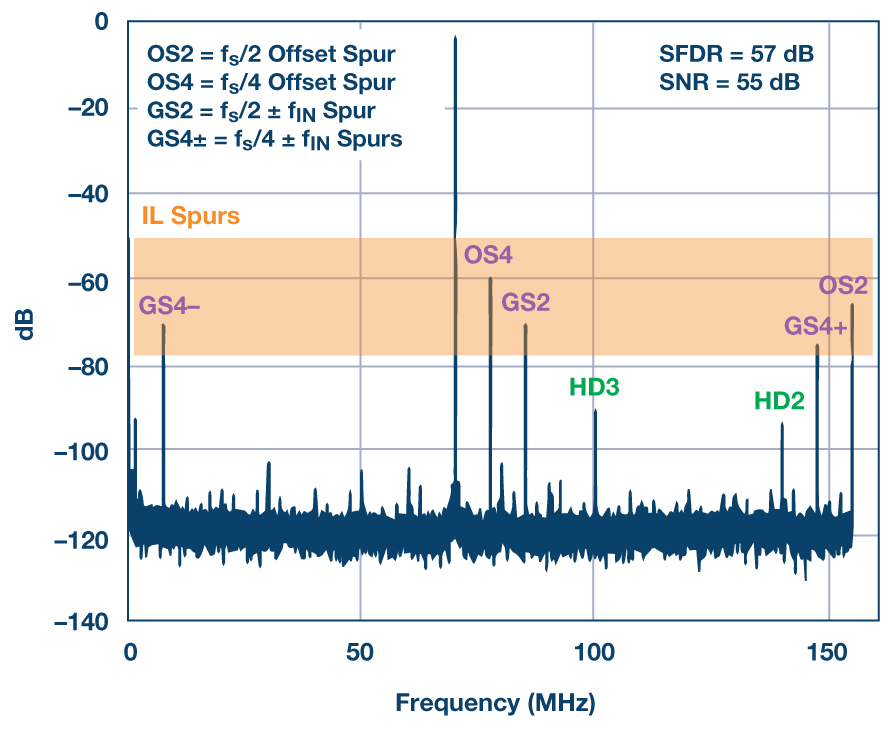

使用通道隨機化的另一個交錯 ADC 示例如圖 6 中的頻譜所示。此時采用四路交錯 16位/310 MSPS ADC AD9652。圖 6 示例中,四個通道以固定順序交錯,并且不進行任何減少通道失配的校準。頻譜清楚表明交錯雜散位于預計頻率位置,且它們的大功率遠高于 2 次和 3 次諧波,并將無雜散動態范圍限制為僅有 57 dBc。

圖6. AD9652的輸出頻譜,時鐘為 fs=310 MHz,采用fIN ~70 MHz的正弦輸入。此時,未施加通道校準和隨機化。2次(HD2)和混疊3次(HD3)諧波分別在大約140 MHz和100 MHz處可見。交錯(IL)雜散同樣可見。這些是直流、fs/2(圖中的OS2)以及fs/4(圖中的OS4)處的失調音。另外,增益(時序)雜散可見于fs /2-fIN(圖中的GS2)、fs /4+fIN(圖中的GS4+)以及fs /4- fIN(圖中的GS4-)。此圖中的SNR查詢人為變差了,因為部分雜散成分和噪聲功率混在了一起。

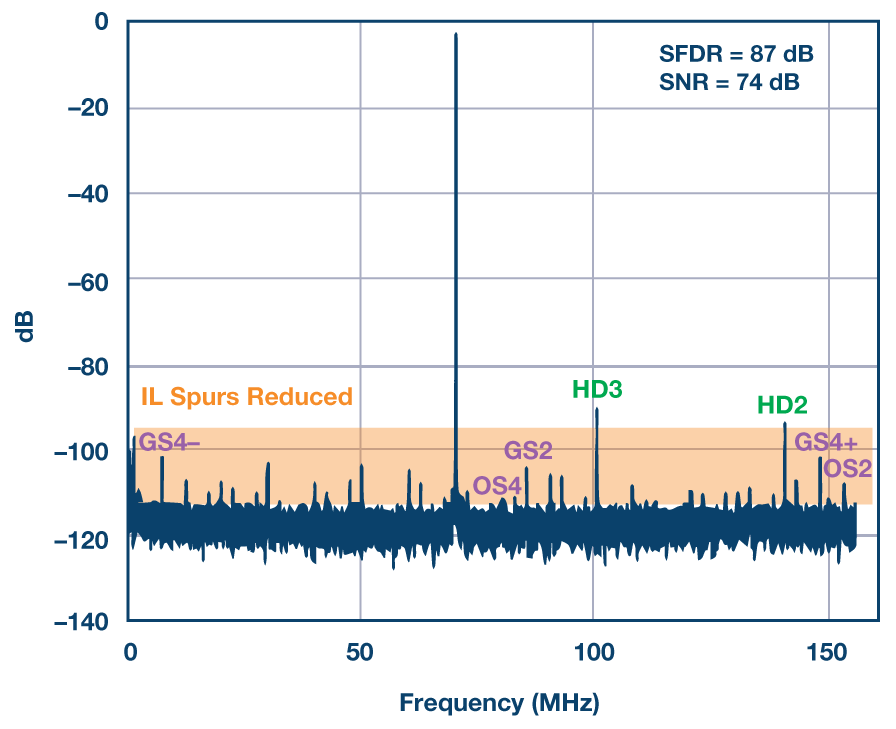

然而,如果同樣的 ADC 經過前景校準以便減少通道失配,那么交錯雜散功率將會大幅下降,如圖7所示。與上例中的情況類似,通道諧波失真不受影響,但通過通道失配校準大幅降低了交錯雜散功率。

圖7. 同一個AD9652的輸出頻譜,采用同樣的輸入,但經過校準后四個通道減少了失配。與圖6相比,雖然2次和3次諧波未受影響,但交錯雜散的功率大幅下降,并且SFDR改善了30 dB,即從57 dBc到87 dBc。

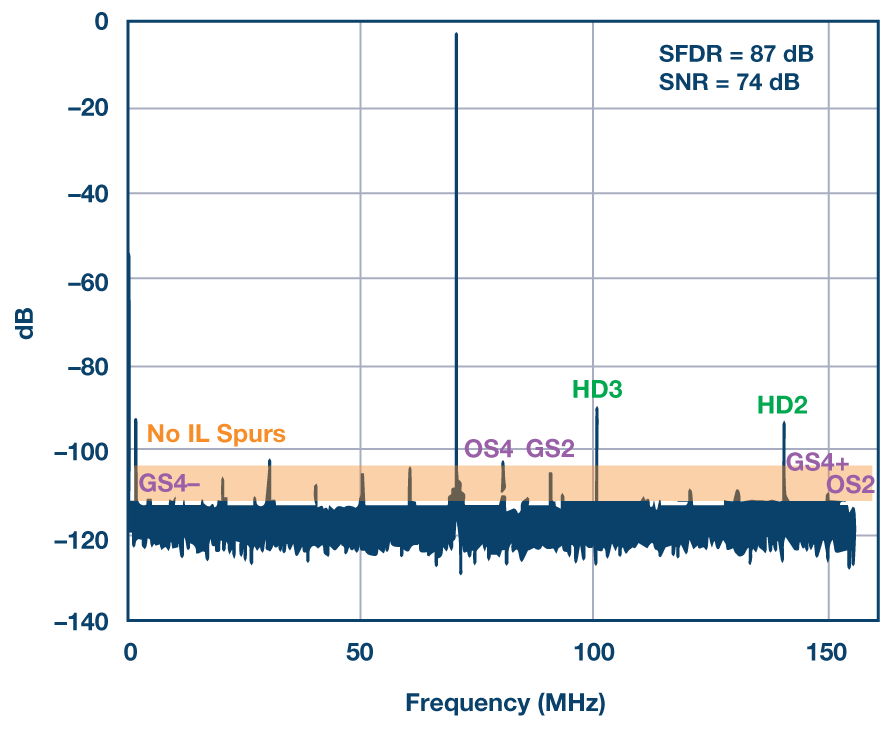

最后,圖7中的頻譜純度可得到進一步改善,方法是使通道順序隨機化,如圖8所示。此時,隨機化使用專利技術,對四個通道的順序進行間歇性加擾無需通過另一個(第五個)通道來達成,從而省下了與此相關的功耗。如圖8所示,經過隨機化之后,結果頻譜中僅有常規諧波失真。

圖8. 上例開啟交錯順序隨機化之后的輸出頻譜。隨機化殘留交錯雜散可將它們的功率擴散到噪底中,相應的尖峰便消失了。可以看到的僅有常規諧波失真。SNR幾乎未受影響,因為來自交錯音并擴散的雜散功率經過失配校準后可以忽略。

結論

時間交錯是增加數據轉換器帶寬的強大技術,在失配校準方面,以及通過隨機化技術消除殘留雜散成分方面的發展已經能夠實現完全集成、極高速 12/14/16 位交錯 ADC。

在輸入信號受頻帶限制的情況下(比如很多通信應用),乒乓(雙路)交錯方法可通過頻率規劃將干擾交錯雜散分配到遠離目標輸入頻段的位置。然后便可以數字手段過濾雜散成分。雖然這種方法相比工作在 IL 采樣速率一半的非交錯式 ADC 獲得同樣的無雜散輸入帶寬所需的功耗要高出幾乎一倍,但它不僅可以通過處理增益提高動態范圍 3 dB,而且還能降低抗混疊的滾降,并修平 ADC 前的濾波器——因為 IL 采樣速率高。

若需要用到 IL 轉換器的全部輸入頻帶才能捕捉寬帶輸入信號,那么可以采用更高次的交錯轉換器。這種情況下,校準和隨機置亂可實現交錯失真和雜散成分的補償和消除。

關于世健

亞太區領先的元器件授權代理商

世健(Excelpoint)是完整解決方案的供應商,為亞洲電子廠商包括原設備生產商(OEM)、原設計生產商(ODM)和電子制造服務提供商(EMS)提供優質的元器件、工程設計及供應鏈管理服務。

世健是新加坡主板上市公司,擁有超過30年歷史。世健中國區總部設于香港,目前在中國擁有十多家分公司和辦事處,遍及中國主要大中型城市。憑借專業的研發團隊、頂尖的現場應用支持以及豐富的市場經驗,世健在中國業內享有領先地位。

原文標題:【世說設計】揭秘ADC時間交錯技術,快來get~

文章出處:【微信公眾號:Excelpoint世健】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

轉換器

+關注

關注

27文章

8953瀏覽量

150732 -

數據

+關注

關注

8文章

7241瀏覽量

91001 -

adc

+關注

關注

99文章

6638瀏覽量

548247

原文標題:【世說設計】揭秘ADC時間交錯技術,快來get~

文章出處:【微信號:Excelpoint_CN,微信公眾號:Excelpoint_CN】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文了解交錯式ADC(數據轉換器)

詳細了解下ups的相關計算

詳細了解一下STM32F1的具體電路參數

拓展一些關于交錯ADC的觀點

ADC 的時間交錯特性討論資料下載

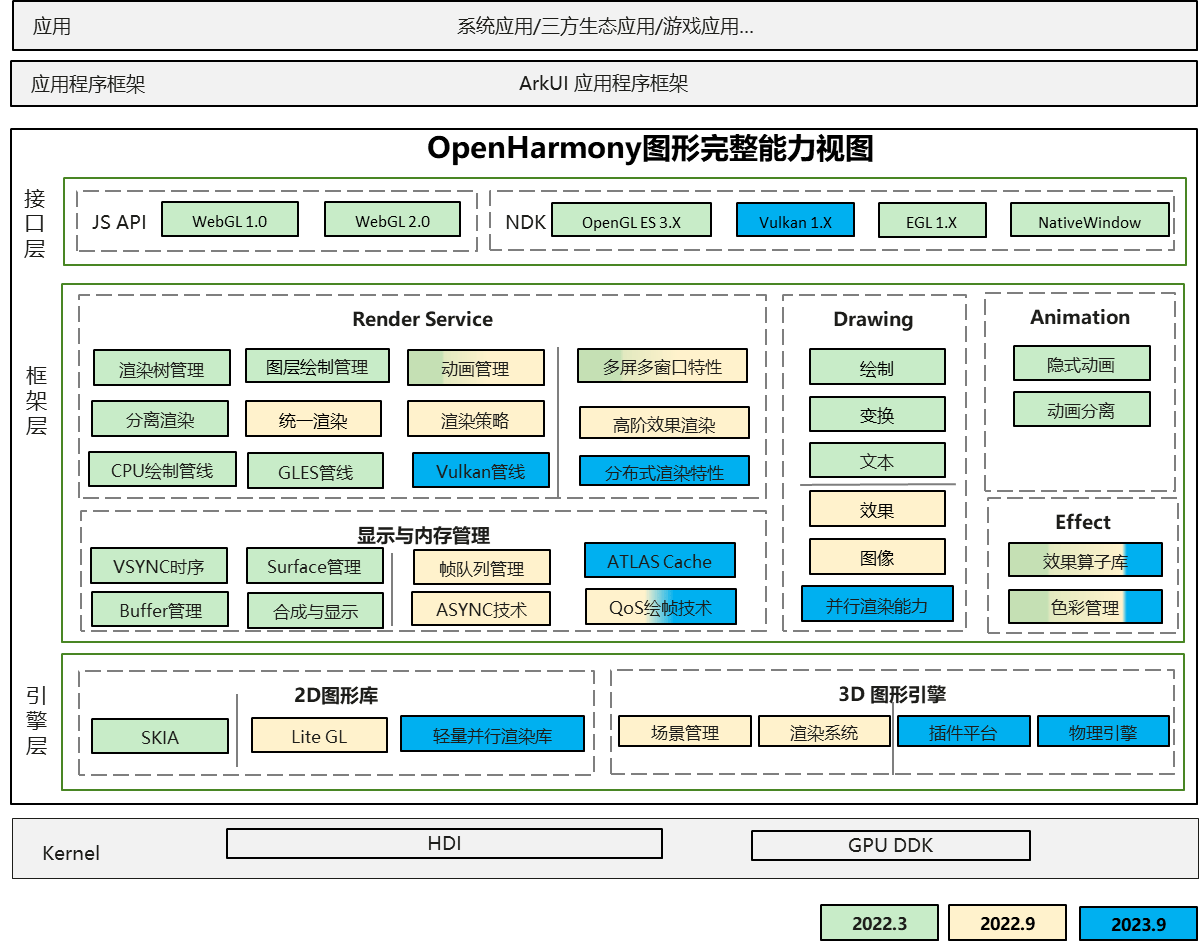

一文詳細了解OpenHarmony新圖形框架

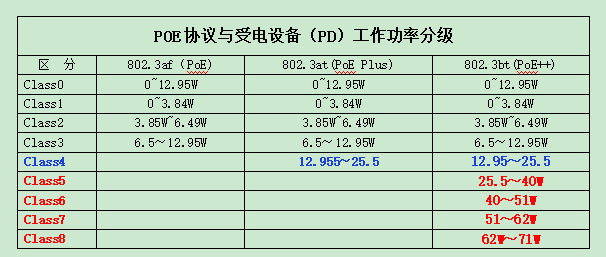

帶您一起詳細了解IEEE802.3bt(PoE++)的有關特點

一文詳細了解ADC時間交錯技術

一文詳細了解ADC時間交錯技術

評論