本應用筆記討論了VMMK-3313及其在15至33 GHz應用中的晶圓級封裝檢測器的使用。VMMK-3313是一種寬帶定向耦合器,具有集成的溫度補償檢測器,設計用于在15至33 GHz的各個頻帶中工作,典型插入損耗為0.5 dB。檢測器提供與RF功率輸入成比例的DC輸出,從而提供測量放大器功率輸出的手段。

簡介

VMMK-3313是一款寬帶定向耦合器,具有集成的溫度補償檢測器,專為15至33 GHz應用而設計。檢測器提供與RF功率輸入成比例的DC輸出,從而提供一種測量放大器功率輸出的方法。

VMMK-3313是三端設備,“直通” 50Ω傳輸線直接連接在RF輸入和RF輸出端口之間。直流偏置被饋送到射頻輸入端口,整流后的直流在射頻輸出端口可用。

使用VMMK-3313

只有三個端子可用,直流偏置和檢測到的電壓在內部分別直流耦合到輸入和輸出端子。VMMK-3313成功運行的關鍵是使用連接到RF輸入端口和RF輸出端口的低損耗偏置去耦網絡。一個簡單的電路如圖1所示。

偏置VMMK-3313檢測器模塊

偏置去耦網絡與用來偏置分立晶體管的網絡非常相似。這兩個網絡都提供了到設備的低損耗交流耦合RF路徑,以及在輸入上對設備進行DC偏置的手段,以及在設備的輸出上提取檢測到的電壓的手段。15至33 GHz頻率范圍內的偏置去耦網絡通常由四分之一波高阻抗線路和低阻抗四分之一波短截線組成。與VMMK-3313的工作頻率范圍相比,它們本質上是窄帶。以R1和R2的形式串聯一些電阻可以提高帶寬。

檢測器的內部負載電阻約為20kΩ。如果需要,可以將電阻器R3用作檢測器的外部負載電阻器。盡管C4提供了額外的去耦,但C4處的任何并聯電容都會減小檢測器的視頻帶寬,因此可能不是所希望的。檢測器本身的-3 dB視頻帶寬約為30 MHz。輸出端子上設備外部的任何其他旁路都會降低帶寬。更詳細的信息將在本應用筆記的后面部分中介紹。

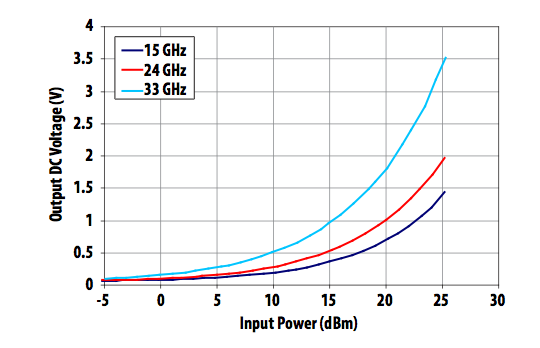

RF輸入端口的建議偏置電壓為1.5V。在該標稱偏置下,偏置電流通常為0.16 mA。如果沒有RF輸入功率,則在檢測到的輸出端口上會出現60 mV的標稱電壓偏移電壓。VMMK-3313的DC輸出與RF輸入的關系圖如圖2所示。

VMMK-3313的輸出DC電壓與RF輸入功率的關系

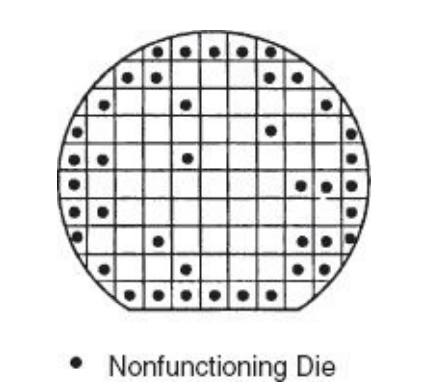

PCB圖案

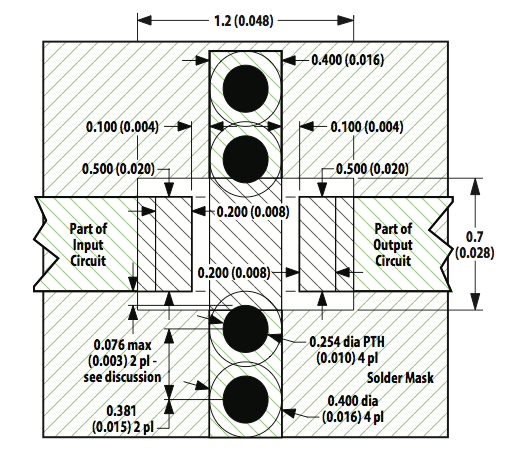

偏置網絡的實現通常在微帶中完成。推薦的印刷電路板通孔圖案如圖3所示。這是非焊料掩膜定義的占位面積(NSMD)。與設備接壤的阻焊層的輪廓由綠色指示的區域顯示。建議的占用空間不需要在設備下方鍍任何通孔。建模和測試表明,如圖3所示,在器件的兩側(0.003英寸以內)并在器件的任一側放置通孔,當將它們安裝在0.010英寸厚的RO4350印刷電路板材料上時,可以為VMMK-3XXX系列器件提供良好的接地。

VMMK器件的推薦PCB布局

演示性能要

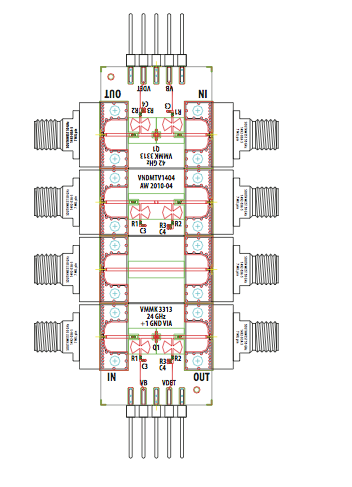

在演示板上演示性能,需要將VMMK-3313安裝在帶有連接器的50Ω微帶線上。具有10密耳厚度的Rogers 4350印刷電路板材料用作低損耗基材,可用于進出VMMK-3313。50Ω的線寬為0.020英寸。印刷電路板疊層是多層疊層,可在測試過程中提供剛性。總厚度為0.060英寸。西南微波2.4毫米連接器(PN 1492-03A-5)用于平滑過渡到微帶線。演示板上已包括偏置去耦網絡,以在輸入端口注入電壓,并作為一種在輸出端口測量檢測到的電壓的手段。

當將低損耗元件嵌入電路板中時,很難測量它在很寬的頻率范圍內的損耗。四分之一波偏置去耦線和梯形斷路開路提供了一種提供偏置去耦的低損耗方法。但是,它們本質上是窄帶。

為了演示VMMK-3313本身的損耗,需要將所有印刷電路板的損耗去嵌入,包括50Ω微帶線,偏置去耦線和連接器。如圖4所示,開發了一組演示板,以幫助測量VMMK-3313的損耗。

VMMK-3313演示板

頂部的演示板包括VMMK-3313器件,偏置去耦網絡和連接器。中間板包括所有這些相同的組件,但VMMK-3313器件除外。這兩塊板之間的損耗之差應該是VMMK-3313的損耗。第三塊板包含一條簡單的50傳輸線和連接器,可用作測量介電損耗的參考。

編輯:hfy

-

檢測器

+關注

關注

1文章

887瀏覽量

48416 -

連接器

+關注

關注

99文章

15217瀏覽量

139290 -

RF

+關注

關注

65文章

3171瀏覽量

168503 -

測量放大器

+關注

關注

0文章

70瀏覽量

9581 -

vmmk器件

+關注

關注

0文章

3瀏覽量

3172

發布評論請先 登錄

什么是晶圓級扇入封裝技術

簽約頂級封裝廠,普萊信巨量轉移技術掀起晶圓級封裝和板級封裝的技術革命

淺談VMMK-3313及15至33 GHz應用中的晶圓級封裝檢測器使用

淺談VMMK-3313及15至33 GHz應用中的晶圓級封裝檢測器使用

評論