經歷了幾年的高速發展之后,人工智能(簡稱 AI)不再是新鮮的名詞,它已經作為一個重要的生產工具,被引入到我們工作和生活的多個領域。但在 AI 爆發的背后,隨之而來的是對 AI 算力需求的暴增。

據 OpenAI 的一份報告顯示,從 2012 年到 2019 年,人工智能訓練集增長了 30 萬倍,每 3.43 個月翻一番,但如果是以摩爾定律的速度,只會有 12 倍的增長。為了滿足 AI 算力的需求,從業人員通過設計專用的 AI 芯片、重配置硬件和算法創新等多方面入手來達成目標。

AI 算力需求增長

然而在此過程中,我們除了看到 AI 對算力的要求以外,內存帶寬也是限制 AI 芯片發展的另一個關鍵要素。這就需要從傳統的馮諾依曼架構談起。作為當前芯片的主流架構,馮諾依曼架構的一大特征就是計算和內存分離的。那就意味著每進行一次計算,計算單元都要從內存中讀取數據然后計算,再把計算結構存回到內存當中。

經典的馮諾依曼架構

在過往,這個架構的短板并不是很明顯,因為處理器和內存的速度都都非常接近。但眾所周知的是,在摩爾定律指導下的處理器在過去幾十年里發生了翻天覆地的變化,但常用的 DRAM 方案與之相比,提升幅度不值一提。

再者,在 AI 時代,數據傳輸量越來越大。先進的駕駛員輔助系統(ADAS)為例。第 3 級及更高級別系統的復雜數據處理需要超過 200 GB/s 的內存帶寬。這些高帶寬是復雜的 AI/ML 算法的基本需求,在道路上自駕過程中這些算法需要快速執行大量計算并安全地執行實時決策。在第 5 級,即完全自主駕駛,車輛能夠獨立地對交通標志和信號的動態環境作出反應,以及準確地預測汽車、卡車、自行車和行人的移動,將需要巨大的內存帶寬。

因此,AI 芯片尋找新的內存方案迫在眉睫,其中 HBM 和 GDDR SDRAM(簡稱 GDDR)就成為了行業的選擇。

為什么是 HBM 和 GDDR ?

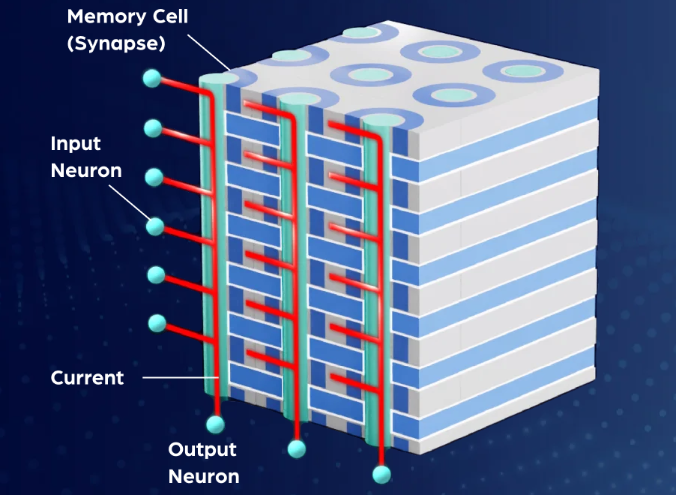

HBM 就是 High Bandwidth Memory 的縮寫,也就是高帶寬內存,這是一項在 2013 年 10 月被 JEDEC 采納為業界標準的內存技術。按照 AMD 的介紹,這種新型的 CPU/GPU 內存芯片(即 “RAM”),就像摩天大廈中的樓層一樣可以垂直堆疊。基于這種設計,信息交換的時間將會縮短。這些堆疊的芯片通過稱為“中介層 (Interposer)”的超快速互聯方式連接至 CPU 或 GPU。將 HBM 的堆棧插入到中介層中,放置于 CPU 或 GPU 旁邊,然后將組裝后的模塊連接至電路板。

盡管這些 HBM 堆棧沒有以物理方式與 CPU 或 GPU 集成,但通過中介層緊湊而快速地連接后,HBM 具備的特性幾乎和芯片集成的 RAM 一樣。更重要的是,這些獨特的設計能給

開發者帶來功耗、性能和尺寸等多個方面的優勢。

從第一代 HBM 與 2013 年面世后,JEDEC 又分別在 2016 年和 2018 把 HBM2 和 HBM2E 納為行業標準。據了解,在 HBM2E 規范下,當傳輸速率上升到每管腳 3.6Gbps 時,HBM2E 可以實現每堆棧 461GB/s 的內存帶寬。此外,HBM2E 支持 12 個 DRAM 的堆棧,內存容量高達每堆棧 24 GB。

具體而言,就是說每一個運行速度高達 3.6Gbps 的 HBM2E 堆棧通過 1024 個數據“線”的接口連接到它的相關處理器。通過命令和地址,線的數量增加到大約 1700 條。這遠遠超出了標準 PCB 所能支持的范圍。因此,硅中介層被采用作為連接內存堆棧和處理器的中介。與 SoC 一樣,精細數據走線可以在硅中介層中以蝕刻間隔的方式實現,以獲得 HBM 接口所需數量的數據線數。

得益于其巨大內存帶寬的能力,使得連接到一個處理器的四塊 HBM2E 內存堆棧將提供超過 1.8 TB/s 的帶寬。通過 3D 堆疊內存,可以以極小的空間實現高帶寬和高容量需求。進一步,通過保持相對較低的數據傳輸速率,并使內存靠近處理器,總體系統功率得以維持在較低水位。

根據 Rambus 的介紹,HBM2E 的性能非常出色,所增加的采用和制造成本可以透過節省的電路板空間和電力相互的緩解 。在物理空間日益受限的數據中心環境中,HBM2E 緊湊的體系結構提供了切實的好處。它的低功率意味著它的熱負荷較低,在這種環境中,冷卻成本通常是幾個最大的運營成本之一。

正因為如此,HBM2E 成為了 AI 芯片的一個優先選擇,這也是英偉達在 Tesla A100 和谷歌在二代 TPU 上選擇這個內存方案的原因。但如前面所說,因為 HBM 獨特的設計,其復雜性、成本都高于其他方案,這時候,GDDR 就發揮了重大的作用。

據了解,圖形 DDR SDRAM(GDDR SDRAM)最初是 20 多年前為游戲和顯卡市場設計的。在這段時間內,GDDR 經歷了幾次重大變革,最新一代 GDDR6 的數據傳輸速率為 16Gbps。GDDR6 提供了令人印象深刻的帶寬、容量、延遲和功率。它將工作電壓從 1.5V 降低到 1.35V 以獲得更高的功率效率,并使 GDDR5 內存的數據傳輸速率(16 比 8 Gbps)和容量(16 比 8 GB)翻了一番。Rambus 已經演示了一個運行速度為 18 Gbps 的 GDDR6 接口,顯示這種內存架構還有額外的增長空間。

與 HBM2E 不同,GDDR6 DRAM 采用與生產標準 DDR 式 DRAM 的大批量制造和組裝一樣的技術。更具體地說,GDDR6 采用傳統的方法,通過標準 PCB 將封裝和測試的 DRAMs 與 SoC 連接在一起。利用現有的基礎架構和流程為系統設計者提供了熟悉度,從而降低了成本和實現的復雜性。

與 HBM2E 寬而慢的內存接口不同,GDDR6 接口窄而快。兩個 16 位寬通道(32 條數據線)將 GDDR6 PHY 連接到相關的 SDRAM。GDDR6 接口以每針 16 Gbps 的速度運行,可以提供 64 GB/s 的帶寬。回到我們之前的 L3 汽車示例,GDDR6 內存系統以連接四個 DRAM 設備為例,帶寬可以達到 200 GB/s。

采用 GDDR6 的主要設計挑戰也來自于它最強大的特性之一:速度。在較低的電壓條件,16 Gbps 的信號速度下,保持信號完整性需要大量的專業經驗知識。設計人員面臨更緊的時序和電壓裕度量損失,這些損失來源與影響都在迅速增加。系統的接口行為、封裝和電路板需要相互影響,需要采用協同設計方法來保證系統的信號完整性。

總的來說,GDDR6 內存的優異性能特性建立久經考驗的基礎制造過程之上,是人工智能推理的理想內存解決方案。其出色的性價比使其適合在廣泛的邊緣網絡和物聯網終端設備上大量采用。

Rambus 將扮演重要角色

從上文的介紹中,我們看到了 HBM2E 和 GDDR 6 在 AI 中的重要作用,而要真正將其落實到 AI 芯片中,相應的 IP 供應商將是很關鍵的一環,而 Rambus 將扮演這個重要角色。

據 Rambus 大中華區總經理 Raymond Su 介紹,Rambus 成立于上個世紀 90 年代,是一家領先的 Silicon IP 和芯片提供商,公司主要致力于讓數據傳輸得更快、更安全。而從產品上看,Rambus 的產品主要聚焦于三大塊:分別是基礎架構許可、Silicon IP 授權,還有 buffer chip 芯片業務。

“得益于這些深厚的積累,我們能提供友商所不具備的差異性服務”,Raymond Su 補充說。他指出:

首先,在內存 IP 層面,Rambus 提供一站式的采購和“turn key”服務。而公司在去年完成的對全球知名的 IP 控制器公司 Northwest Logic 和對 Verimatrix 安全 IP 業務部,可以讓 Rambus 能夠提供更好的一站式的服務。

“通過這樣的服務,Rambus IP 可以很好地幫助客戶盡早地把產品推向市場”,Raymond Su 表示。

其次,作為全球領先的 HBM IP 供應商,Rambus 在全球已經有 50 多個成功項目案例,積累了大量的經驗;而在 DDR5 Buffer Chip(緩沖芯片)方面,Rambus 也是全球首發。這讓他們在 DDR5 時代有信心改變整個市場。而在 AI 芯片迫切需要的 HBM2E 和 GDDR 6 IP 方面,Rambus 也都做好了準備。

從 Rambus IP 核產品營銷高級總監 Frank Ferro 的介紹我們得知,他們將 HBM2E 的性能提升到了 4Gbps。在他看來,這個速度是一個全新的行業標桿,而此次 Rambus 發布我們全新的 HBM2E 產品也正是實現了這一行業最高標準。

根據 Rambus 發布的白皮書介紹,他們 HBM2E 接口完全符合 JEDEC JESD235B 標準。支持每個數據引腳高達 3.6 Gbps 的數據傳輸速率。該接口具有 8 個獨立的通道,每個通道包含 128 位,總數據寬度為 1024 位。由此每個堆棧支持的帶寬是 461GB/s,每個堆棧由 2、4、8 或 12 個 DRAMs 組成。

作為一個為 2.5D 系統設計的 IP,它有一個用于在 3D-DRAM 堆棧和 SoC 上的 PHY 之間的中介層由提供信號繞線。這種信號密度和堆積尺寸的組合需要特殊的設計考慮。為了便于實施和提高了設計的靈活性,Rambus 對整個 2.5D 系統進行完整的信號和功率完整性分析,以確保所有信號、功率和散熱要求都得到滿足。而在于其他競爭對手相比,Rambus 的 HBM IP 則有著大多數廠商布局的幾點核心優勢:

第一,Rambus 提供的是完全集成而且經過驗證的 PHY 以及內存控制器 IP 解決方案,在物理層面實現完整的集成互聯。除了完整的內存子系統之外,他們的 PHY 也經過了硬核化處理,同時也完成了 timing closed 也就是時序收斂的工作。

“我們給客戶提供的并不僅僅是自己的 IP 授權、IP 產品,我們也會向客戶提供系統級的全面的集成支持,以及相關的工具套件,以及我們的技術服務。同時,我們也可以幫助客戶更加進一步地減少設計實現的難度。” Frank Ferro 補充說。他進一步指出,在發布了這個 IP 之后,Rambus 將會為人工智能以及機器學習的應用客戶提供更加完整的解決方案,幫助他們進一步地提高帶寬,滿足他們在帶寬上的需求。

第二,Rambus 擁有非常強大的 HBM 生產經驗,在這方面,公司已經擁有了全球超過 50 家成功的客戶案例,這在全球是名列前茅的。更重要的一點,Rambus 所有合作客戶的芯片從設計到原型再到投產,并不需要任何的設計返工,基本上所有的芯片都會實現一次的成功。這足以體現他們的實力。

第三,Rambus 為客戶提供非常完整的參考設計框架,其中最重要的一點就是如何更好地對中介層進行完整的設計和表征化的處理。“因為對于中介層來,講它是 PHY 層和 DRAM 層之間溝通的重要環節,在這個過程中,因為速度非常快,所以說如何保證信號完整性也是必須要去考慮的。” Frank Ferro 表示。

他進一步指出,Rambus 與客戶非常緊密地進行合作,并為他們提供非常完整的參考設計框架,然后幫助他們更好地去設計自己的中介層以及產品的封裝。除此之外,Rambus 也幫助客戶做仿真分析,讓他們對自己每個信號的通道進行完整的分析,來實現整個產品的最高性能。

第四,這也是非常重要的一點,那就是 Rambus 有一套非常重要的工具——Lab Station。借助這個工具,Rambus 會與客戶進行合作,讓他們將其 HBM2E 解決方案直接插入到他們的終端系統當中,來構建一個非常獨立的內存子系統。

能在 HBM2E IP 獲得這樣的成就,一方面,Rambus 的研發投入功不可沒;另一方面,他們與 SK 海力士、AIChip 和臺積電多方人員的通力合作,也是他們能提供快速服務的原因之一。例如在 SK 海力士方面,它為 Rambus 提供的 HBM2E 內存達到了 3.6G 的數據傳輸速率,而在和合作過程中,兩者又將 HBM2E 的速率進一步地推進到了 4.0 Gbps;AIchip 則為 Rambus 提供了 ASIC 的相關解決方案以及產品,幫助其設計了相關中介層以及封裝;此外,臺積電提供了一個交鑰匙的 2.5D Cowos 封裝以及解決方案,來更好地為 Rambus 打造一個晶圓上的基本架構。

“我們的解決方案適用于人工智能以及機器學習的訓練,同時也非常適用于高性能計算系統和 5G 網絡的基礎設施建設”,Frank Ferro 最后說。

除了面向 AI 訓練的 HMB2E IP,Rambus 還推出了面向 AI 推理的 GDDR 6 產品。

據 Rambus 的白皮書介紹,公司的 GDDR6 接口專為性能和功率效率而設計,支持 AI/ML 和 ADAS 推理高帶寬與低延遲要求。它由一個經共同驗證的 PHY 和數字控制器組成,提供一個完整的 GDDR6 內存子系統。Rambus GDDR6 接口完全符合 JEDEC GDDR6 JESD250 標準,每個引腳支持高達 16 Gbps。GDDR6 接口支持 2 個通道,每個通道有 16 位,

總數據寬度為 32 位。Rambus GDDR6 接口每針 16 Gbps,提供帶寬為 64 GB/s。

通過直接與客戶合作,Rambus 能提供完整的系統信號和電源完整性(SI/PI)分析,創建優化的芯片布線版圖。客戶收到一個硬核解決方案與全套測試軟件可以快速啟動,定性和調試。

在“內存墻”的限制下,為了滿足 AI 應用的數據搬運需求,產業界正在探索不同的方法來解決問題。例如英國 AI 芯片初創企業 Graphcore 就希望通過分布式內存設計的方法解決這個問題。

而 Rambus 的這兩個方案出現那就給開發者們提供了在傳統架構設計上獲得性能大提升的可能。

審核編輯 黃昊宇

-

芯片

+關注

關注

459文章

52169瀏覽量

436095 -

內存

+關注

關注

8文章

3108瀏覽量

74985 -

AI

+關注

關注

87文章

34196瀏覽量

275345

發布評論請先 登錄

拋棄8GB內存,端側AI大模型加速內存升級

請問STM32N6 cubeAI部署時用的內存是在內部還是外部?

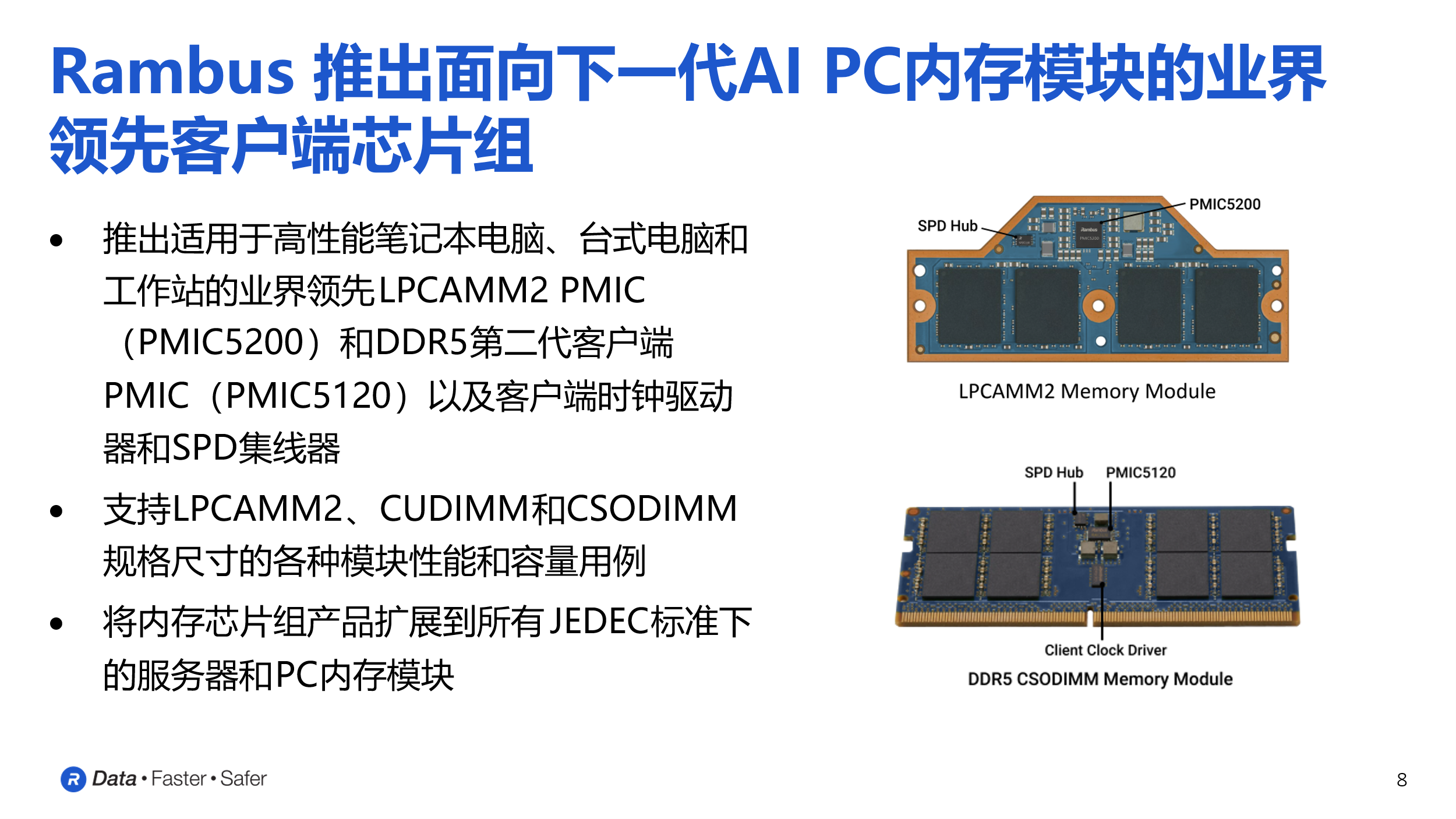

AI PC內存升級,這顆DDR5 PMIC一馬當先

AI時代企業需要怎樣的數據存儲

請問STM32N6 cubeAI部署時用的內存是在內部還是外部?

首創開源架構,天璣AI開發套件讓端側AI模型接入得心應手

英偉達加速認證三星AI內存芯片

海量數據處理需要多少RAM內存

北橋芯片負責與cpu的聯系并控制內存嗎

智能駕駛需要怎樣的ISP?

我們需要怎樣的大模型?

ai開發需要什么配置

AI芯片需要怎樣的內存

AI芯片需要怎樣的內存

評論