2020年7月,實驗室關(guān)于硅和氮化鎵異質(zhì)集成芯片的相關(guān)研究成果在國際半導(dǎo)體器件權(quán)威期刊IEEETransactions on Electron Devices上發(fā)表,郝躍院士團(tuán)隊的張家祺博士和張葦杭博士為本論文的共同第一作者,張春福教授為論文的通訊作者。國際半導(dǎo)體行業(yè)著名雜志《Semiconductor Today》及時對成果進(jìn)行了跟蹤報道,受到國內(nèi)外業(yè)界的關(guān)注。

《Semiconductor Today》總部位于英國,是國際半導(dǎo)體行業(yè)著名雜志和網(wǎng)站,專注于報道國際半導(dǎo)體領(lǐng)域的重要研究進(jìn)展和最新行業(yè)動態(tài),具有很強(qiáng)的行業(yè)影響力。《Semiconductor Today》指出:中國西安電子科技大學(xué)研究團(tuán)隊研發(fā)的“轉(zhuǎn)印與自對準(zhǔn)刻蝕技術(shù)”有效地實現(xiàn)了晶圓級的異質(zhì)集成,有望將多種不同的功能材料如硅、氮化鎵等集成在晶圓級的單片上,以此為基礎(chǔ)制造的器件及集成電路理論上具有更加多樣強(qiáng)大的功能與更高的集成度。基于所研發(fā)的低成本轉(zhuǎn)印與自對準(zhǔn)刻蝕新技術(shù),西安電子科技大學(xué)團(tuán)隊首次實現(xiàn)了晶圓級硅與氮化鎵單片異質(zhì)集成的增強(qiáng)型共源共柵晶體管,取得了硅和氮化鎵晶圓級單片異質(zhì)集成新突破。該新技術(shù)避免了昂貴復(fù)雜的異質(zhì)材料外延和晶圓鍵合的傳統(tǒng)工藝技術(shù),有望成為突破摩爾定律的一條有效技術(shù)路徑。

氮化鎵高功率器件在電力電子領(lǐng)域中受到越來越多的關(guān)注,在汽車電子、機(jī)電控制、光伏產(chǎn)業(yè)和各類電源系統(tǒng)中得到越來越多的應(yīng)用。電力電子器件更加需要常關(guān)態(tài)增強(qiáng)型氮化鎵功率器件,但由于異質(zhì)結(jié)二維電子氣形成原因,一般的氮化鎵器件主要是耗盡型的。一種可行的方案是由一個增強(qiáng)型硅晶體管與一個耗盡型氮化鎵晶體管級聯(lián)組成共源共柵型增強(qiáng)型氮化鎵器件,這種結(jié)構(gòu)擁有穩(wěn)定的正閾值電壓并且與現(xiàn)有的柵驅(qū)動電路相兼容。此外,由于硅MOS結(jié)構(gòu)的引入使得共源共柵氮化鎵器件具有更大的與驅(qū)動電路兼容的柵壓擺幅。

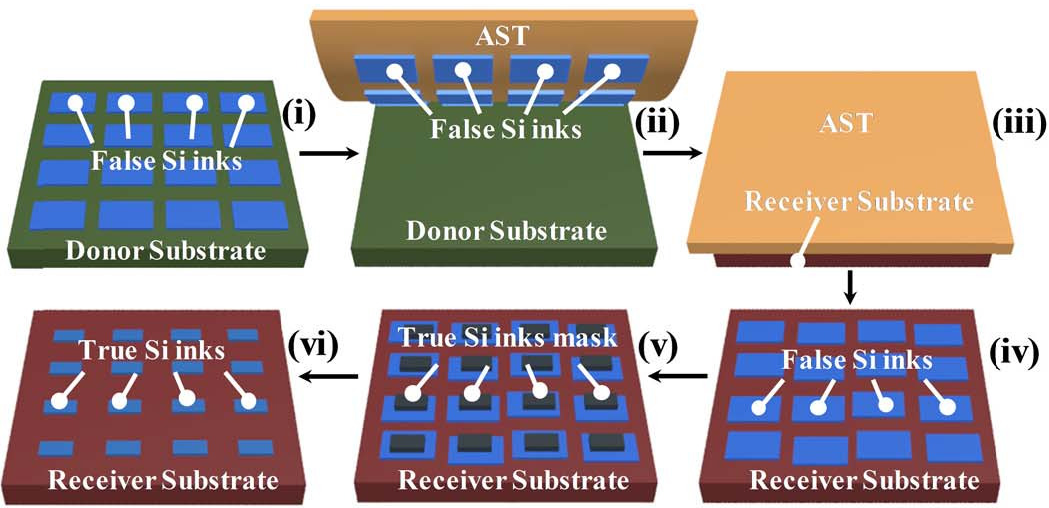

然而,如何實現(xiàn)晶圓級單片集成Si-GaN共源共柵晶體管是一個十分困難的問題,因為這涉及到兩種完全不同的半導(dǎo)體材料集成在同一個晶圓上。郝躍院士團(tuán)隊創(chuàng)新地提出了一種轉(zhuǎn)印和自對準(zhǔn)刻蝕方法,并首次實現(xiàn)了晶圓級的Si-GaN單片異質(zhì)集成的共源共柵晶體管。這項技術(shù)和方法有望實現(xiàn)多種材料的大規(guī)模異質(zhì)集成并基于此制造功能多樣化的器件和電路,避免了昂貴且復(fù)雜的材料異質(zhì)共生技術(shù)或晶圓鍵合工藝。通過轉(zhuǎn)印和自對準(zhǔn)刻蝕的新技術(shù),使得硅器件與氮化鎵器件的互連距離縮短至100μm以下,僅為傳統(tǒng)鍵合線長度的5%。據(jù)估算,新型的共源共柵晶體管可以比傳統(tǒng)鍵合方法減少98.59%的寄生電感。Si-GaN單片異質(zhì)集成的共源共柵晶體管的閾值電壓被調(diào)制為2.1V,實現(xiàn)了增強(qiáng)型器件。該器件柵壓擺幅在柵漏電低于10-5mA/mm的范圍內(nèi)達(dá)到了±18V。經(jīng)過大量器件測試和可靠性試驗后,芯片之間的性能具有良好的一致性,這充分證明了轉(zhuǎn)印和自對準(zhǔn)刻蝕技術(shù)實現(xiàn)晶圓級單片集成共源共柵晶體管的巨大潛力和優(yōu)勢。

-

晶圓級

+關(guān)注

關(guān)注

0文章

37瀏覽量

10005 -

半導(dǎo)體器件

+關(guān)注

關(guān)注

12文章

777瀏覽量

32764 -

GaN器件

+關(guān)注

關(guān)注

1文章

46瀏覽量

8039

原文標(biāo)題:西電郝躍院士團(tuán)隊實現(xiàn)硅與GaN器件的晶圓級單片異質(zhì)集成

文章出處:【微信號:mwrfnet,微信公眾號:微波射頻網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

用于切割晶圓 TTV 控制的硅棒安裝機(jī)構(gòu)

提供半導(dǎo)體工藝可靠性測試-WLR晶圓可靠性測試

深入探索:晶圓級封裝Bump工藝的關(guān)鍵點

日本Sumco宮崎工廠硅晶圓計劃停產(chǎn)

超薄硅晶圓的發(fā)展歷程與未來展望!

為什么晶圓是圓的?芯片是方的?

一文了解晶圓級封裝中的垂直互連結(jié)構(gòu)

利用全息技術(shù)在硅晶圓內(nèi)部制造納米結(jié)構(gòu)的新方法

長電微電子晶圓級微系統(tǒng)集成高端制造項目正式通線

詳解不同晶圓級封裝的工藝流程

碳化硅晶圓和硅晶圓的區(qū)別是什么

長電微電子晶圓級微系統(tǒng)集成高端制造項目即將投產(chǎn)

二維材料 ALD 的晶圓級集成變化

西電郝躍院士團(tuán)隊實現(xiàn)硅與GaN器件的晶圓級單片異質(zhì)集成

西電郝躍院士團(tuán)隊實現(xiàn)硅與GaN器件的晶圓級單片異質(zhì)集成

評論