隨著相控陣雷達、超寬帶雷達、數字陣列雷達相繼地出現,雷達的回波數據量在不斷地增加,因此對高速采集和大容量數據傳輸提出了越來越高的要求。早期基于PCI總線的高速數據采集系統在帶寬、流量控制和數據傳送質量上存在一定缺陷,在某種程度上并不能完全適應高速大容量數據存儲的要求。相比較而言,PCI Expres總線具有鮮明的技術優勢,不僅完全兼容PCI總線,而且全面解決了PCI總線所面臨的帶寬、流量控制和數據傳送質量方面問題,由于使用高速差分總線,時鐘頻率可以達到較高水平,其總線帶寬較PCI總線也有大幅度提升,目前X16的PCI Express峰值帶寬可以達到80 GT/s。PCI Express技術的逐步成熟,為高速數據數據傳輸提供了較好的解決方案。

1、 DMA控制邏輯設計

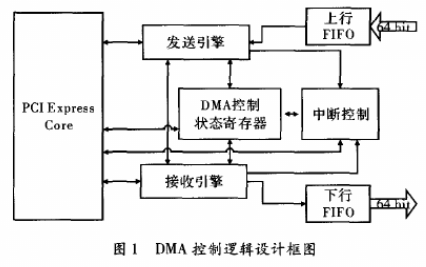

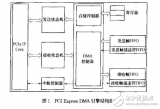

DMA控制邏輯設計如圖1所示,主要有PCIExpress Core、接收引擎、發送引擎、DMA控制狀態寄存器和中斷控制等關鍵模塊。

1.1 PCI Express Core

主要特點如下:(1)符合PCI Express Base Specification 2.0規范。(2)支持X1、X2、X4或X8模式。(3)片上GTP/GTX收發器實現PHY。(4)具有訪問PCI Express配置空間和內部配置的管理接口。(5)支持最大的有效載荷(128~4 096 Byte)。(6)可針對存儲器或I/O進行配置的基地址寄存器(BAR)。

1.2 接收引擎

在PCI Express系統邏輯結構中,接收引擎主要是在接口時鐘的控制下,按照基本TLP接收時序,解析存儲器讀寫請求并從TLP中提取所需信息并將其傳送到存儲器訪問控制器,存儲器訪問控制器處理存儲器寫TLP中寫入存儲器的數據,并使用存儲器中的數據讀來響應存儲器讀TLP;此外接受引擎主要還負責處理存儲器讀完成TLP,響應板卡發起的DMA讀操作。

1.3 發送引擎

在PCI Express系統邏輯結構中,發送引擎主要是在接口時鐘的控制下,按照基本TLP發送時序,為接收到的存儲器讀TLP生成完成包,生成該完成包所需的信息會由存儲控制器傳送到發送引擎;此外發送引擎還負責發起存儲器讀寫請求TLP,實現與PC之間數據的DMA讀寫。

1.4 DMA狀態控制寄存器

在PCI Express系統邏輯結構中,DMA狀態控制寄存器主要是實現PCI Express Core與Root Complex之間數據的傳遞。Windows GUI軟件配置DMA控制狀態寄存器控制DMA操作。DMA控制狀態寄存器映射于PCI Express Memory BAR0空間,Windows GUI軟件通過Memory Write和Read周期訪問寄存器。Windows GUI軟件初始化DMA控制寄存器發起DMA傳輸,而通過狀態寄存器,以中斷方式通知Root Complex DMA傳輸完成。

1.5 中斷控制

當DMA傳輸結束時,為及時通知PC響應并處理中斷,中斷控制部分使用核的配置層接口信號產生中斷。PCI Express支持兩種中斷:消息信號中斷(MSI)和傳統中斷(Legacy INT)。在PCI Express設備枚舉過程中,跟聯合體會根據自身對中斷支持的能力設置配置空間中的命令寄存器和消息信號中斷能力寄存器,來決定使用何種中斷。

2、 PCI Express Masfer DMA讀寫設計驗證

2.1 DMA寫設計驗證

數據流向:上行FIFO數據→PCI Express Master DMA Write→PC內存→PC硬盤。

整個DMA寫過程如下:(1)復位FPGA邏輯,延時1 ms;去除FPGA邏輯,延時1 ms。(2)檢測硬件鏈路初始化。(3)開啟DMA寫完成中斷。(4)設置DMA寫目的地址寄存器,設置DMA寫傳輸長度寄存器。(5)啟動DMA寫操作,選擇記錄路徑。(6)等待DMA寫完成中斷。(7)清除中斷,內存數據轉到硬盤。(8)DMA寫是否結束,是則轉至步驟(9);否則轉至步驟(4)。(9)終止DMA寫,關閉DMA寫完成中斷,斷開記錄路徑。

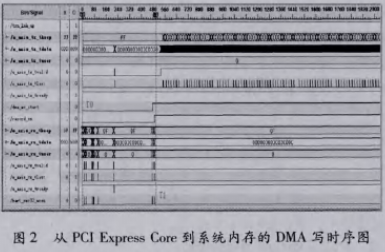

下面給出從PCI Express Core到系統內存的DMA寫時序,圖2是用ChipScope截取的時序圖。

T0~T1之間核接收事務接口上m_axis_rx_tvalid與m_axis_rx_tlast共同有效了8次,即執行了8次PIO內存讀寫操作。其中第6次為PIO讀操作,相應的發送事務接口上s_axis_tx_tvalid與s_axis_tx_tlast有效,產生Cpld完成包以回應PIO讀操作。從圖中可以看出,DMA狀態控制寄存器配置完成后,dma_wr_start信號有效,即啟動DMA寫操作。此后PCI Express Core開始在發送事務接口上發送存儲器寫事物包,事物包的地址、大小已經在DMA狀態控制寄存器中配置。

2.2 DMA讀設計驗證

數據流向:PC硬盤→PC內存→PCI Express Master DMA Read→下行FIFO數據。

整個DMA讀過程如下:(1)復位FPGA邏輯,延時1 ms;去除FPGA邏輯,延時1 ms。(2)檢測硬件鏈路初始化。(3)開啟DMA讀完成中斷。(4)設置DMA讀目的地址寄存器,設置DMA讀傳輸長度寄存器。(5)PC硬盤數據轉到內存。(6)啟動DMA讀操作,選擇回放路徑。(7)等待DMA讀完成中斷。(8)清除中斷,硬盤數據轉到內存。(9)DMA讀是否結束,是則轉至步驟(10);否則轉至步驟(4)。(10)終止DMA讀,關閉DMA讀完成中斷,斷開回放路徑。

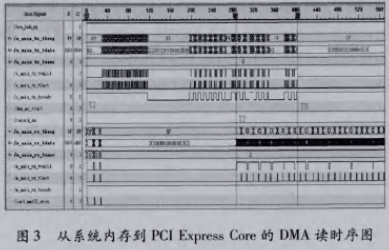

下面給出從系統內存到PCI Express Core的DMA讀時序,圖3是用ChipScope截取的時序圖。

T1~T2之間核接收事務接口上m_axis_rx_tvalid與m_axis_rx_tlast共同有效了3次。此處需要說明的是DMA讀操作在配置完寄存器后需要先從PC硬盤將數據轉到內存開辟的數據緩沖區,此后才能開始DMA讀操作,故T1~T2之間核接收事務接口上m_axis_rx_tvalid與m_axis_rx_ tlast有效為配置DMA讀地址和啟動DMA讀操作。當DMA讀操作啟動后,核的發送事務接口上s_axis_tx_tvalid與s_axis_tx_tlast有效,發送存儲器讀請求包,當PC收到PCI Express Core發出的存儲器讀請求包后會根據TLP中的信息回復相應的Cpld完成包。根據PCIExpress總線規范中對PCI Express序的規定,允許接收事務接口在接收Cpld完成包的同時發送事務接口在發送存儲器讀請求包,見圖中T1~T2之間所示。

2.3 PCI Express中斷控制

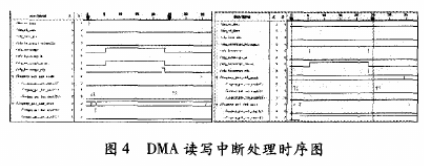

當DMA寫結束,即dma_wr_done或dma_rd_done其中之一有效時,用戶應該通過配置接口cfg_interrupt和cfg_interrupt_assert來提交中斷,當核接收到有效中斷時將cfg_interrupt_rdy置為有效,表示中斷請求被接受。PC通過讀DMA中斷寄存器從而認領中斷事務,響應處理中斷后清除中斷。用ChipScope捕獲的DMA讀寫完成中斷時序,如圖4所示。

3、 系統性能測試

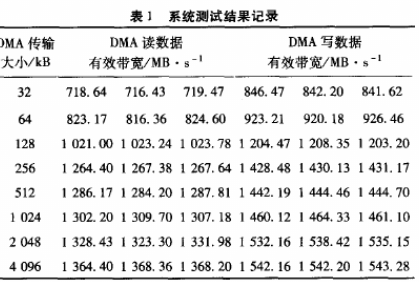

系統性能測試結果如表1所示。存儲器讀寫DMA數據有效帶寬測試為DMA啟動到最后一個存儲器寫TLP或最后一個存儲器讀完成包,測試數據總量為8 GB。

測試平臺:Xilinx ML605開發板(Virtex-6 FPGA);Windows7 64位操作系統,Windriver驅動;PCIExpress鏈路寬度:X8,PCI Express Core版本:V2.5;MaxPayload Size:128 Bytes;Max Read Request Size:512 Byte;Root Complex Read Completion Boundary:64 Byte。

4 、結束語

研究了基于Xilinx PCI Express Core的高速DMA讀寫設計,適用于現代雷達系統和高速數據采集系統的要求,并具有良好的移植和擴展性。文中給出了DMA設計框圖,并對系統各部分進行了分析。系統設計中主要研究了PCI Express Master DMA讀寫設計及中斷控制,并給出了DMA讀寫和中斷控制的采樣時序,通過系統性能測試數據,可以看出本文所設計的基于Xilinx PCI Express Core的高速DMA讀寫可以滿足高速信號處理的要求。

責任編輯:gt

-

寄存器

+關注

關注

31文章

5421瀏覽量

123324 -

存儲器

+關注

關注

38文章

7635瀏覽量

166407 -

總線

+關注

關注

10文章

2949瀏覽量

89346

發布評論請先 登錄

基于IP核的PCI總線接口設計與實現

PCI總線接口芯片9054及其應用

基于PCI總線的CPLD實現

ISA總線的標準DMA技術在Linux中的實現

總線接口控制器PCI9052資料推薦

利用S5935實現DMA傳輸的研究

基于PCI Express總線高速數據采集卡的設計與實現

PCI總線至UTOPIA接口控制的CPLD設計實現

PCI Express總線介紹與光纖通道HBA卡DMA引擎的設計與實現

S5935如何實現DMA傳輸的設計與研究

基于PCI Core的鏈式DMA控制器設計

基于PCI Expres總線實現DMA控制邏輯的設計

基于PCI Expres總線實現DMA控制邏輯的設計

評論