芯片設(shè)計是每個國家的發(fā)展重點(diǎn)之一,而壯大中國芯片設(shè)計行業(yè)將有利于降低我國對國外芯片的依賴程度。再往期文章中,小編曾對芯片設(shè)計的正反向流程、芯片設(shè)計前景等內(nèi)容進(jìn)行過相關(guān)介紹。本文中,小編將為大家介紹帶來芯片設(shè)計實(shí)戰(zhàn)篇——射頻識別芯片設(shè)計中的時鐘樹功耗的優(yōu)化與實(shí)現(xiàn)。

1 概述

UHF RFID是一款超高頻射頻識別標(biāo)簽芯片。該芯片采用無源供電方式:在收到載波能量后,RF前端單元產(chǎn)生Vdd電源信號,供給整芯片工作。由于供電系統(tǒng)的限制,該芯片無法產(chǎn)生較大的電流驅(qū)動,因此低功耗設(shè)計成為芯片研發(fā)過程中的主要突破點(diǎn)。為了使數(shù)字電路部分產(chǎn)生盡量少的功耗,在數(shù)字邏輯電路設(shè)計過程中,除了簡化系統(tǒng)結(jié)構(gòu)外(功能簡單,只包含編碼模塊、解碼模塊、隨機(jī)數(shù)生成模塊、時鐘、復(fù)位模塊,Memory控制單元以及整體控制模塊),在部分電路設(shè)計中采用了異步電路設(shè)計方式。在這個過程中,我們看到由于時鐘樹消耗掉了數(shù)字邏輯的很大一部分功耗(大約30%以上),所以降低時鐘樹帶來的功耗也成為降低數(shù)字邏輯功耗以及整個標(biāo)簽芯片功耗的重要步驟。

2 芯片功耗組成及降低功耗的方法

2.1功耗的組成

圖1 芯片功耗的組成

動態(tài)功耗主要包括短路功耗和翻轉(zhuǎn)功耗,是本設(shè)計功耗的主要組成部分。短路功耗即內(nèi)部功耗,指由器件內(nèi)部由于P管和N管在某一瞬間同時導(dǎo)通引起的瞬時短路引起。翻轉(zhuǎn)功耗由CMOS器件的輸出端負(fù)載電容充放電引起。漏電功耗主要包括亞閾區(qū)漏電和柵極泄漏引起的功耗。

當(dāng)今,功耗兩個最主要的來源是:電容轉(zhuǎn)換和亞閾值泄漏。

2.2降低功耗的主要方法

圖2 降低芯片功耗的主要方法

2.2.1降低電源電壓Vdd

Voltage Island:不同的模塊使用不同的供電電壓。

MulTI-level Voltage Scaling:同一模塊中存在多種電壓源,根據(jù)應(yīng)用不同在這些電壓源之間切換。

Dynamic Voltage Frequency Scaling:“多級電壓調(diào)整”的升級版,根據(jù)各模塊的工作頻率動態(tài)進(jìn)行電壓調(diào)整。

AdapTIve Voltage Scaling:DVFS的升級版,使用能夠監(jiān)視電路行為的反饋電路,自適應(yīng)地調(diào)整電壓。

亞閾值電路(設(shè)計困難較多,還停留在學(xué)術(shù)界研究范圍)

2.2.2降低頻率f及翻轉(zhuǎn)率A

代碼優(yōu)化(提取公因子,資源重用,operand isolaTIon,串行工作降低峰值功耗等)

門控時鐘

多時鐘策略

2.2.3降低負(fù)載電容(CL)及晶體管尺寸(Wmos)

減少時序單元

芯片面積和規(guī)模減小

工藝升級換代

2.2.4降低漏電電流Ileak

控制閾值電壓(Threshold Voltage)(閾值電壓↑漏電流↓如使用MTCMOS 、VTCMOS 、DTCMOS)

控制柵極電壓(Gate Voltage)(通過控制柵源電壓以控制漏電流)

Transistor Stack(串接冗余晶體管,增加電阻以降低漏電流)

門控電源(Power gaTIng或PSO)(在模塊不工作時,關(guān)斷電源,即可有效減小漏電流)

3 RFID芯片中時鐘樹功耗的優(yōu)化

芯片工作時,很大一部分功耗是由于時鐘網(wǎng)絡(luò)的翻轉(zhuǎn)消耗的,如果時鐘網(wǎng)絡(luò)較大,這部分引起的功耗損失會很大。在眾多低功耗技術(shù)中,門控時鐘對翻轉(zhuǎn)功耗和內(nèi)部功耗的抑制作用最強(qiáng)。本設(shè)計多級門控時鐘技術(shù)相結(jié)合,以及特殊的時鐘樹優(yōu)化策略,節(jié)省了很大一部分功耗。本項(xiàng)目在邏輯設(shè)計時使用了功耗的多種優(yōu)化策略,在后端的綜合和物理設(shè)計也嘗試了一些方法,通過前后端幾次功耗優(yōu)化和迭代,找出最小功耗的邏輯代碼設(shè)計和綜合的方法。

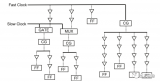

4.1 RTL階段手工加時鐘門控

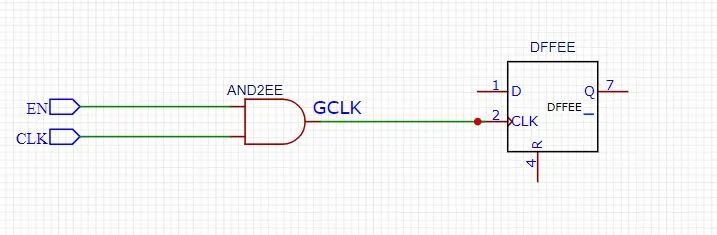

圖3 門控時鐘原理圖

module data_reg (En, Data, clk, out)

input En,clk;

input [7:0] Data;

output [7:0] out;

always @(posedge clk)

if (En) out = Data;

endmodule

這個階段的目的主要有兩個:第一是根據(jù)各模塊時鐘翻轉(zhuǎn)概率更加合理的加入門控時鐘單元以控制翻轉(zhuǎn)率,減小動態(tài)功耗,第二是產(chǎn)生一個結(jié)構(gòu)盡量平衡的時鐘網(wǎng)絡(luò),這樣可以保證在后端時鐘樹綜合階段可以少加入一些時鐘buffer以減小功耗。在實(shí)際的代碼設(shè)計中可以直接采用foundry單元庫中的ICG(集成門控)單元。

4.2 綜合階段工具插于集成門控單元

圖4 邏輯綜合過程中門控時鐘插入

#Set clock gating options, max_fanout default is unlimited

set_clock_gating_style -sequential_cell latch \

-positive_edge_logic {integrated} \

-control_point before \

-control_signal scan_enable

#Create a more balanced clock tree by inserting “always enabled” ICGs

set power_cg_all_registers true

set power_remove_redundant_clock_gates true

read_db design.gtech.db

current_design top

link

source design.cstr.tcl

#Insert clock gating

insert_clock_gating

compile

#Generate a report on clock gating inserted

report_clock_gating

這個階段的目的是通過綜合工具(DC)進(jìn)行門控單元的自動插入,以便進(jìn)一步減小功耗。

需要注意的是對插入ICG的參數(shù)的設(shè)定,比如maximum fanout(扇出越大越節(jié)省功耗,扇出越平衡skew越小,視設(shè)計而定,如圖所示),以及minimum_bitwidth參數(shù)的設(shè)定,另外對于較復(fù)雜的門控結(jié)構(gòu)需要插入常開ICG以使時鐘網(wǎng)絡(luò)結(jié)構(gòu)更加平衡。

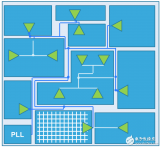

4.3 時鐘樹綜合階段優(yōu)化功耗

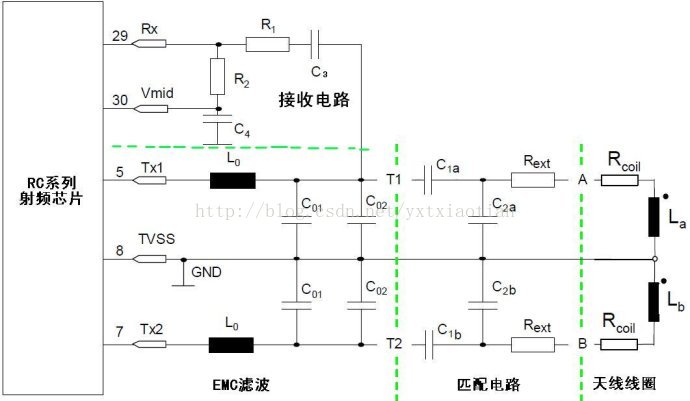

圖5 兩種時鐘樹結(jié)構(gòu)對比(a):多級縱深型;(b):少級扁平型

先介紹一下時鐘樹綜合參數(shù)對時鐘樹結(jié)構(gòu)的影響:

Skew :時鐘偏移,總的時鐘樹綜合目標(biāo)。

Insertion delay(Latency):時鐘路徑總延時,用于限定時鐘樹級數(shù)的增加。

Max taranstion:由最大轉(zhuǎn)換時間限定一級buffer能驅(qū)動的buffer 的數(shù)量。

Max Capacitance Max Fanout:由最大負(fù)載電容、最大扇出限定一級buffer 能驅(qū)動的buffer 數(shù)量。

一般設(shè)計中的時鐘樹綜合以降低時鐘skew為最終目的,加大level級數(shù),減小每級fanout,將投入較多buffer,更精確的平衡每條時鐘路徑的 latency,從而得到較小skew。但是對于低功耗設(shè)計,尤其是當(dāng)時鐘頻率較低的時候,時序要求并不是很高,所以希望能減小時鐘樹的規(guī)模以減小時鐘樹帶來的動態(tài)翻轉(zhuǎn)功耗。如圖所示,通過減小時鐘樹level級數(shù),加大fanout可以有效減小時鐘樹的規(guī)模,但由于buffer 數(shù)量的減少,較之多級結(jié)構(gòu)的時鐘樹,級數(shù)較少結(jié)構(gòu)的時鐘樹只是大概平衡每條時鐘路徑的latency,得到的skew較大。可見,以降低時鐘樹規(guī)模為目標(biāo),進(jìn)行低功耗時鐘樹綜合是以增大一定的skew為代價的。

具體到本RFID芯片,我們采用了TSMC 0.18um CMOS LOGIC/MS/RF工藝,時鐘頻率只有1.92M,是非常低的,此時時鐘進(jìn)行時鐘樹綜合時,采用以降低時鐘樹規(guī)模為目標(biāo)的低功耗時鐘樹綜合,主要對 skew,latency和transiton這幾個約束進(jìn)行了設(shè)定,由于約束fanout會帶來時鐘樹級數(shù)的增加,帶來功耗的增加,所以沒有設(shè)定這個值,采用庫里的默認(rèn)值。在實(shí)際中,我們使用了9種不同的時鐘樹約束條件,約束條件及綜合結(jié)果如表1 所示。

5 結(jié)論

如表1所示,總的趨勢就是target skew設(shè)的越大,最終的時鐘樹規(guī)模越小,時鐘樹buffer數(shù)量越小,對應(yīng)的動態(tài)靜態(tài)功耗也越小,這樣就達(dá)到了節(jié)省時鐘樹功耗的目的。可以看到當(dāng)target skew大于10ns后,功耗基本不再變化,但是基于大的skew值會帶來hold時序的變差導(dǎo)致修復(fù)時序的時候插入buffer增多,所以應(yīng)該進(jìn)行折中,從圖表來看策略5和策略6為優(yōu)選方案。另外當(dāng)skew設(shè)置選出最優(yōu)后,還可以看到Max transition值設(shè)的越大最終得到的功耗也越小,這可以理解為時鐘信號躍遷的時間越長所需要的能量越小。另外latency約束的設(shè)置可以盡量放大,其值的大小對最終的功耗結(jié)果影響不大。

-

芯片

+關(guān)注

關(guān)注

459文章

52174瀏覽量

436134 -

射頻

+關(guān)注

關(guān)注

106文章

5728瀏覽量

169732 -

時鐘樹

+關(guān)注

關(guān)注

0文章

56瀏覽量

10964

發(fā)布評論請先 登錄

時鐘樹優(yōu)化與有用時鐘延遲

射頻識別芯片設(shè)計中時鐘樹功耗的優(yōu)化與實(shí)現(xiàn)

STM32芯片的時鐘樹圖

前后端協(xié)同的時鐘樹設(shè)計方法

低功耗無源超高頻射頻識別應(yīng)答器芯片的射頻電路

時鐘網(wǎng)格與時鐘樹設(shè)計方法對比研究

基于CCopt引擎的SMIC40nm低功耗工藝CortexA9的時鐘樹實(shí)現(xiàn)

LUCT工具主要特性及不確定性時鐘樹設(shè)計方法和算法的介紹

評價時鐘樹質(zhì)量的方法

時鐘樹綜合CTS階段如何去降低Latency和Skew

芯片設(shè)計進(jìn)階—門控時鐘

射頻識別芯片設(shè)計的時鐘樹功耗實(shí)戰(zhàn)

射頻識別芯片設(shè)計的時鐘樹功耗實(shí)戰(zhàn)

評論