目前全球最先進(jìn)的半導(dǎo)體工藝已經(jīng)進(jìn)入 7nm,下一步還要進(jìn)入 5nm、3nm 節(jié)點,制造難度越來越大,其中晶體管結(jié)構(gòu)的限制至關(guān)重要,未來的工藝需要新型晶體管。來自中科院的消息稱,中國科學(xué)家研發(fā)了一種新型垂直納米環(huán)柵晶體管,它被視為 2nm 及以下工藝的主要技術(shù)候選,意義重大。

從 Intel 首發(fā) 22nm FinFET 工藝之后,全球主要的半導(dǎo)體廠商在 22/16/14nm 節(jié)點開始啟用 FinFET 鰭式晶體管,一直用到現(xiàn)在的 7nm,未來 5nm、4nm 等節(jié)點也會使用 FinFET 晶體管,但 3nm 及之后的節(jié)點就要變了,三星在去年率先宣布 3nm 節(jié)點改用 GAA 環(huán)繞柵極晶體管。

根據(jù)官方所說,基于全新的 GAA 晶體管結(jié)構(gòu),三星通過使用納米片設(shè)備制造出了 MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應(yīng)管),該技術(shù)可以顯著增強(qiáng)晶體管性能,主要取代 FinFET 晶體管技術(shù)。

此外,MBCFET 技術(shù)還能兼容現(xiàn)有的 FinFET 制造工藝的技術(shù)及設(shè)備,從而加速工藝開發(fā)及生產(chǎn)。

前不久三星還公布了 3nm 工藝的具體指標(biāo),與現(xiàn)在的 7nm 工藝相比,3nm 工藝可將核心面積減少 45%,功耗降低 50%,性能提升 35%。

從上面的信息也可以看出 GAA 環(huán)繞柵極晶體管的重要意義,而中科院微電子所先導(dǎo)中心朱慧瓏研究員及其課題組日前突破的也是這一領(lǐng)域,官方表示他們從 2016 年起針對相關(guān)基礎(chǔ)器件和關(guān)鍵工藝開展了系統(tǒng)研究,提出并實現(xiàn)了世界上首個具有自對準(zhǔn)柵極的疊層垂直納米環(huán)柵晶體管(Vertical Sandwich Gate-All-Around FETs 或 VSAFETs),獲得多項中、美發(fā)明專利授權(quán)。

這一研究成果近日發(fā)表在國際微電子器件領(lǐng)域的頂級期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2954537)。

左上:STEM 頂視圖,用原子層選擇性刻蝕鍺硅的方法制作的直徑為 10 納米的納米線(左)和厚度為 23 納米的納米片(右)

右上:具有自對準(zhǔn)高k金屬柵的疊層垂直納米環(huán)柵晶體管(VSAFETs)的 TEM 截面圖(左)及 HKMG 局部放大圖(右)

下: pVSAFETs 器件的結(jié)構(gòu)和I-V 特性:器件結(jié)構(gòu)示意圖(左),轉(zhuǎn)移特性曲線(中)和輸出特性曲線(右)

據(jù)介紹,朱慧瓏課題組系統(tǒng)地研發(fā)了一種原子層選擇性刻蝕鍺硅的方法,結(jié)合多層外延生長技術(shù)將此方法用于鍺硅/硅超晶格疊層的選擇性刻蝕,從而精確地控制納米晶體管溝道尺寸和有效柵長;首次研發(fā)出了垂直納米環(huán)柵晶體管的自對準(zhǔn)高k金屬柵后柵工藝;其集成工藝與主流先進(jìn) CMOS 制程兼容。課題組最終制造出了柵長 60 納米,納米片厚度 20 納米的p型 VSAFET。原型器件的 SS、DIBL 和電流開關(guān)比(Ion/Ioff)分別為 86mV/dec、40mV 和 1.8x105。

-

三星電子

+關(guān)注

關(guān)注

34文章

15885瀏覽量

182124 -

晶體管

+關(guān)注

關(guān)注

77文章

9978瀏覽量

140637

發(fā)布評論請先 登錄

無結(jié)場效應(yīng)晶體管詳解

手機(jī)芯片進(jìn)入2nm時代,首發(fā)不是蘋果?

集成電路制造工藝中的偽柵去除技術(shù)介紹

日本開發(fā)出用于垂直晶體管的8英寸氮化鎵單晶晶圓

臺積電2nm工藝將量產(chǎn),蘋果iPhone成首批受益者

7納米工藝面臨的各種挑戰(zhàn)與解決方案

臺積電分享 2nm 工藝深入細(xì)節(jié):功耗降低 35% 或性能提升15%!

IBM與Rapidus在多閾值電壓GAA晶體管技術(shù)的新突破

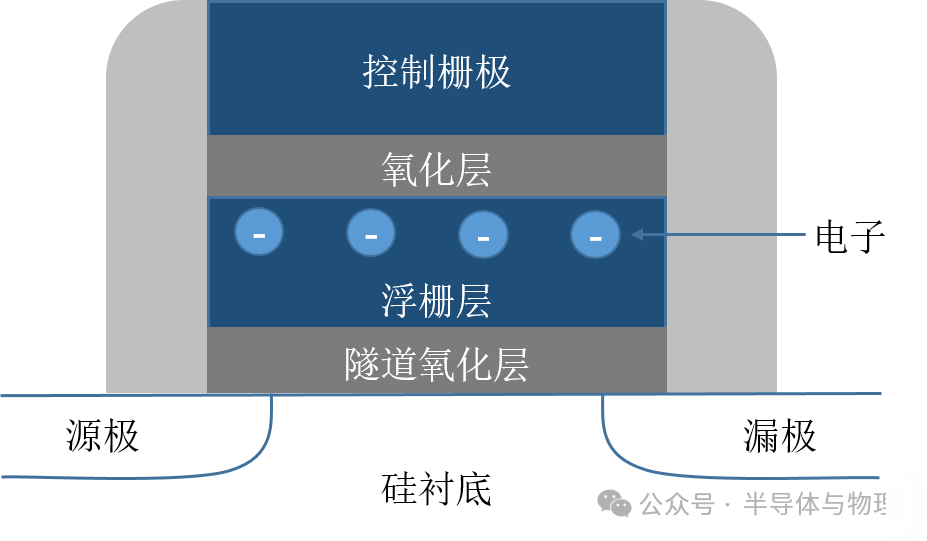

浮柵晶體管的組成結(jié)構(gòu)以及原理

3D-NAND浮柵晶體管的結(jié)構(gòu)解析

新型垂直納米環(huán)柵晶體管,或是2nm及以下工藝的備選

新型垂直納米環(huán)柵晶體管,或是2nm及以下工藝的備選

評論