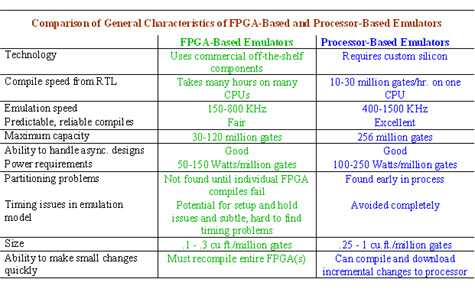

工程師更廣泛地理解基于FPGA的仿真,因為工程師習慣于使用FPGA進行設計。對基于處理器的仿真器的理解不太了解,而且有大量錯誤信息的例子比比皆是。本文將嘗試消除解釋基于處理器的仿真如何工作以及如何將設計構造映射到其中的謎團,例如三態總線,復雜存儲器和異步時鐘。

早期基于處理器的仿真

在1990年代早期,IBM開創了基于處理器的仿真技術,這是他們早期工作的一個分支。基于硬件的仿真引擎。硬件技術由大量布爾處理器組成,這些處理器能夠以非常高的速度相互共享數據。軟件技術包括在許多處理器之間劃分設計,并以正確的時間順序和最佳方式調度各個布爾運算。

最初,性能無法與基于FPGA的仿真器匹配,但編譯時間不到一小時,消除了困擾基于FPGA的仿真器的時序問題,使新技術對許多使用模型很有吸引力,特別是模擬加速。該技術的后代最終在仿真速度上超越了FPGA系統,同時保留了編譯時間的巨大優勢?并且沒有一百臺PC的農場用于編譯。

軟件技術的進步擴展了基于處理器的仿真器的應用,以處理具有任意數量時鐘的異步設計。其他擴展支持設計中所有信號的100%可見性,從仿真運行開始的任何時間對所有信號的可見性,以及邏輯分析器觸發事件的動態設置,無需重新編譯。在基于FPGA的系統的仿真速度不斷降低的同時,新一代基于處理器的系統不僅以驚人的速度提高了仿真速度,而且還證明了其容量可擴展到數億個門。

基于處理器的仿真器架構

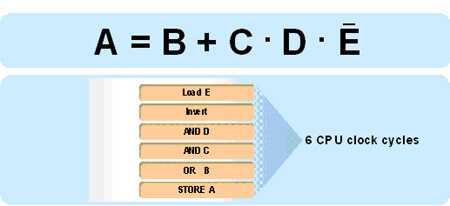

了解處理器的方式基于仿真器的工作原理,簡要回顧一下邏輯仿真器的工作原理很有用。回想一下,計算機的ALU(算術邏輯單元)可以對變量執行基本的布爾運算,例如AND,OR,NOT,并且諸如“always @(posedge Clock)Q = D”之類的語言構造構成了a的基礎。拖鞋。

在門(和透明鎖存器)的情況下,模擬順序很重要。信號通過門鏈示意性地“從左到右”競爭,或者在RTL源代碼中“從上到下”。觸發器(寄存器)打破門鏈以進行排序。

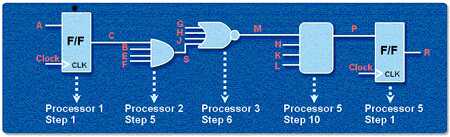

圖1 ??邏輯模擬; CPU對信號執行布爾運算,寄存器

一種類型的模擬器,一個分級編譯邏輯模擬器,以正確的順序一次一個地執行布爾方程。 (時間延遲與功能邏輯仿真無關。)如果有兩個ALU可用,您可以想象將設計分解為兩個獨立的邏輯鏈并將每個鏈分配給ALU,從而并行化并減少所需的時間,也許是一半。

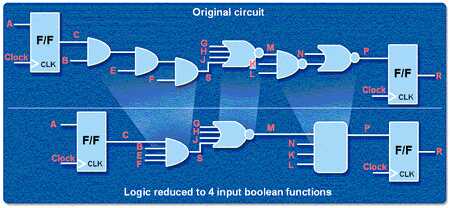

基于處理器的仿真器具有數萬到數十萬個ALU,這些ALU可以有效地進行調度,以正確的順序執行設計中的所有布爾方程。以下系列圖紙說明了這一過程。對于此示例,我們假設模擬器中有一個4輸入布爾基元。

圖2 ??步驟1:將布爾邏輯簡化為四輸入函數

將邏輯簡化為四輸入函數后的布爾方程組是:

IF(時鐘上升) C = A

S = C& B& E& F

M = NOT(G + H + J + S)

P = NOT(N + NOT(M& K& L))

IF(時鐘上升)R = P

此外,以下排序約束集適用:

必須首先評估觸發器

必須在M之前計算S

M必須在P

之前計算

在計算S之前必須對主輸入B,E和F進行采樣

在計算M之前必須對主輸入G,H和J進行采樣

在計算P之前必須對主輸入K,L和N進行采樣

注意:在觸發器之后的任何時間都可以對主輸入A進行采樣

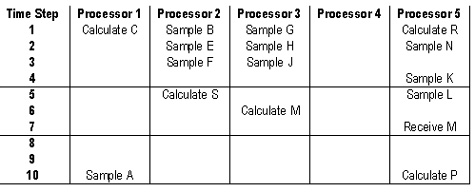

上面顯示了一種可能的調度。這是出于說明目的而完成的,并且可能不是最有效的調度。

圖3 ??調度邏輯的結果

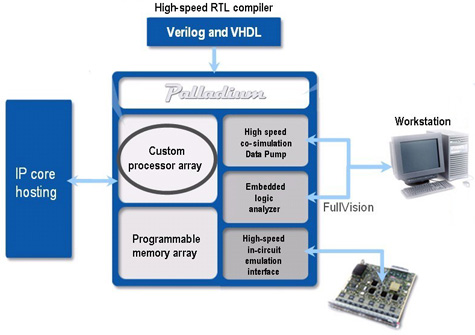

圖4 ??基于處理器的仿真器架構

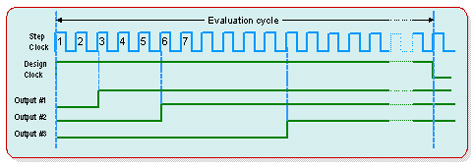

仿真周期包括運行所有處理器步驟以完成設計的完整建模。大型設計通常安排在125? 320步。如果設計可以使用1x時鐘(稍后描述),則基于處理器的仿真器的仿真速度將在600KHz和1.5MHz之間。

在每個時間步驟中,每個處理器都能夠執行任何4輸入邏輯功能,使用任何處理器的任何先前計算結果和任何設計輸入或存儲器內容作為輸入。處理器在集群中物理實現,在集群內快速通信。編譯器優化處理器調度以最大化速度和容量。

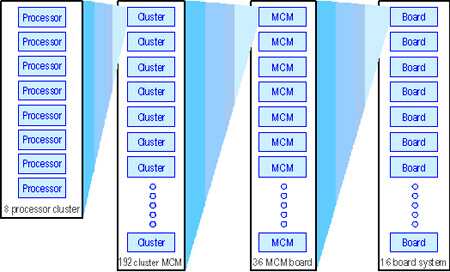

圖5 ??處理器陣列架構示例

設計編譯

RTL設計的編譯完全自動化,并按以下順序完成:

1)將RTL代碼映射到原始單元,例如門和寄存器。

2)合成存儲器。

3)展平設計的層次結構。

4)將布爾邏輯(門)減少為4 - 輸入功能。

5)通過在最佳位置插入寄存器來中斷設計中的異步循環。

6)為目標系統和任何硬IP分配外部連接。

7)設置任何需要的儀表邏輯(例如邏輯分析儀“視覺”)。

8)以統一的方式將所有設計輸入和輸出分配給處理器。

9)將設計中的每個單元分配給處理器。優先考慮將具有公共輸入和/或輸出的信元分配給相同的處理器或集群,并為每個處理器分配相同數量的信元。

10)將每個處理器的活動安排為連續的時間步長。目標是最小化最大時間步數。

編譯器還必須考慮模擬加速連接,三態總線建模,內存建模,非均勻處理器連接,邏輯分析儀探測和觸發等因素。

但編譯器無需處理FPGA仿真器中高度可變的FPGA內部時序。因此,基于處理器的仿真編譯速度更快,資源更少。盡管執行了布爾優化,編譯器仍會維護所有最初指定的RT級網名,以便在調試中使用。這允許用戶使用他們熟悉的信號名稱進行調試。

三態總線建模

三態總線采用組合邏輯建模。當沒有啟用任何啟用時,用戶可以選擇“上拉”,“下拉”或“保留狀態”。在后一種情況下,當沒有啟用驅動器時,將鎖存器插入設計中以保持總線的狀態。在多個使能開啟的情況下,對于上拉和保持狀態邏輯0將“贏”并且對于下拉邏輯1將獲勝。 (注意:這是使用斷言的好地方。)

異步循環中斷

由于仿真器不對門級硅時序建模,因此異步循環會自動中斷編譯期間的延遲觸發器。編譯器將自動中斷異步循環而無需用戶干預。

但是,通過允許用戶指定應該發生循環中斷的位置,可以提高性能,因為基于處理器的仿真器的性能與長組合路徑的長度有關。通過插入延遲元件來打破錯誤路徑或多時鐘周期路徑,如果這些路徑是設計的關鍵路徑,則可以提高性能。

長組合路徑

仿真器的處理器使用特定深度的指令“堆棧”運行,例如160個字。這些是設計計算順序的時間步驟。

有時,設計中可能會有一個非常長的組合路徑,無法將其安排到可用的連續步驟數中。注意,這并不一定意味著邏輯路徑具有更多“門級”,因為調度必須考慮許多時間序列約束。

在這種情況下,調度程序將通過使用未使用的處理器時間步驟在第二遍中調度剩余的布爾運算來完成路徑。這也可能是因為嘗試將太多的門擠入仿真器,但是,作為一個好處,它提供了用戶權衡仿真速度與容量的關系。

基于處理器的仿真器中的時鐘處理

如前所述,時鐘是基于FPGA的仿真器不可靠性的主要來源之一。基于處理器的仿真器完全避免了這個問題,因為它們可以生成設計所需的所有時鐘或接受外部生成的時鐘。

讓仿真器生成所需的所有設計時鐘會更方便嗎?它運行得更快。您可以指定每個時鐘的頻率,也可以讓編譯器從測試平臺中提取此信息(如果有的話)。某些基于處理器的仿真器允許您從目標系統向仿真器提供外部時鐘。在這種情況下,仿真器將其內部時鐘與外部時鐘同步。

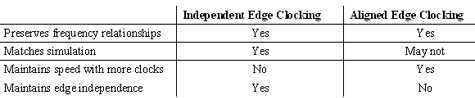

為了提供盡可能高的仿真速度,同時保持所需的異步精度,一些基于處理器的仿真器提供了兩種處理異步設計時鐘的方法:對齊邊和獨立邊緣。

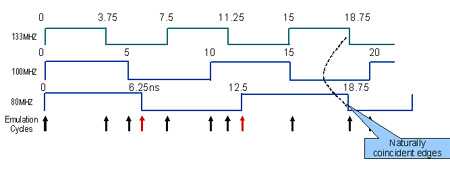

圖6 ??時鐘示例??三個異步時鐘

獨立邊沿時鐘

由于仿真器不對設計時序進行建模,而是功能等效,因此異步時鐘邊沿之間的精確時序無關緊要。只需要在“現實生活”中不同時的時鐘邊緣是獨立模擬的。

通過獨立的邊沿時鐘,基于處理器的仿真器為每個時鐘的每個邊沿調度仿真周期,除非邊緣與已經調度的邊緣自然共同發生。這與事件驅動的模擬器非常相似。

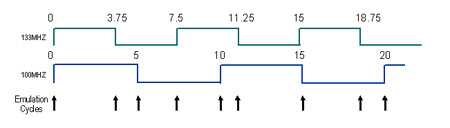

圖7 ??兩個異步時鐘的獨立邊沿時鐘

從兩個時鐘開始,133 MHz時鐘從0到7.5,15.0等的高電平有時(以ns為單位)從高電平轉換為高電平。在時間為5,15,25等時,100MHz時鐘從低到高從低到高轉換為高,低為5,15,25等。注意兩者是任意同步的在時間= 0.

仿真周期#1:133 MHz時鐘上升,100 MHz時鐘上升(兩者同時發生)。

仿真周期#2:133 MHz下降(時間= 3.75)。 100 MHz無效。

仿真周期#3:100 MHz下降(時間= 5.00)。 133 MHz無效。

仿真周期#4:133 MHz上升(時間= 7.5)。 100 MHz無效。

仿真周期#5:10 MHz上升(時間= 10)。 133 MHz無效。

仿真周期#6:133 MHz下降(時間= 11.25)。 100 MHz無效。

仿真周期#7:133 MHz上升,100 MHz下降(時間= 15ns ??兩次轉換)

圖8 ??添加具有獨立邊沿時鐘的第三個異步時鐘

所以時間表如下:仿真周期#1:133 MHz時鐘上升,100 MHz和80 MHz時鐘上升(同時發生) 。仿真周期#2:133 MHz下降(時間= 3.75)80 MHz,100 MHz什么都不做。

仿真周期#3:100 MHz下降(時間= 5.00)80 MHz,133 MHz什么也不做。

仿真周期#4:80 MHz下降(時間= 6.25)100 MHz,133 MHz什么也不做。

仿真周期#5:133 MHz上升(時間= 7.5)80 MHz,100 MHz什么都不做。

仿真周期#6:100 MHz上升。 (時間= 10)80 MHz,100 MHz不執行任何操作。

仿真周期#7:133 MHz下降。 (時間= 11.25)80 MHz,100 MHz無效。

仿真周期#8:80 MHz上升。 (時間= 12.5)100 MHz,133 MHz什么都不做。

仿真周期#9:133 MHz上升,100 MHz下降(時間= 15ns ??兩次轉換)。

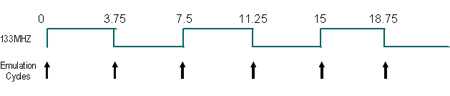

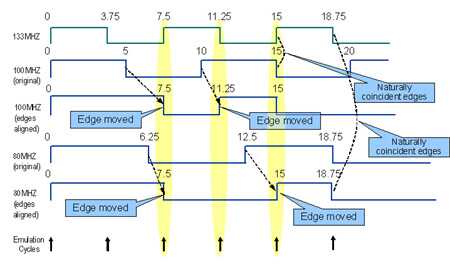

對齊邊沿時鐘

對齊邊沿時鐘基于以下事實:盡管設計中的許多時鐘由于其頻率而碰巧具有非重合邊緣,但正確的電路操作并不依賴于邊緣是獨立的。在這種情況下,在保持適當的頻率關系的同時,時鐘邊沿與最高頻率時鐘對齊,從而減少了所需的仿真周期數,并提高了仿真速度。

在對齊的邊沿時鐘中,我們首先為設計中最快時鐘的每個邊沿調度仿真周期。

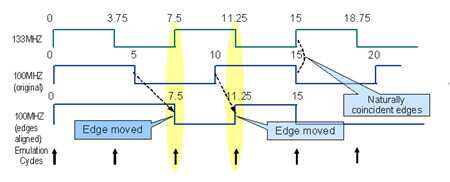

圖9 ??通過為最快時鐘的每個邊沿分配仿真周期開始對齊邊沿時鐘

然后,所有其他時鐘相對于此時鐘進行調度,較慢的時鐘邊沿與下一個預定仿真“對齊”周期。請注意,第二個(較慢)時鐘沒有添加額外的仿真周期。因此保持了仿真速度。另請注意,雖然邊沿移動到跟隨最快的時鐘邊沿,但仍保持頻率關系,這對于正確的電路操作是必不可少的。

圖10 ??添加第二個時鐘對齊邊緣到最快時鐘

圖11 ??通過將邊緣與最快時鐘對齊來添加其他時鐘

對齊邊緣時鐘中的過采樣和欠采樣

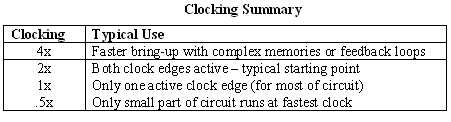

當在最快設計時鐘的兩個邊沿存在仿真周期時,它被稱為“2x”時鐘(每個最快時鐘周期兩個仿真周期)。

1x時鐘

有時在設計中只有最快設計時鐘的一個邊沿有效,或者一個邊緣占主導地位,而另一個邊沿占用最少量的電路。在這種稱為“1x時鐘”的情況下,每個設計時鐘周期的單個仿真周期加倍?還是差不多?仿真速度。所需容量可能略有增加。

如果一個邊緣不占優勢,那么仍然可以應用這種技術,但所需容量的增加將會顯著增加。請注意,只有使用最快時鐘的電路和任何大于最快時鐘速度一半的時鐘才能滿足所需容量的增加。

4x時鐘?過采樣

這可以快速啟動包含復雜異步路徑的設計。具有讀 - 修改 - 寫存儲器或背靠背鎖存器的設計可以通過最初使用4x時鐘更快地進行仿真。

有時稱為“過采樣”,4x時鐘為每個活動時鐘邊沿提供兩個仿真周期(或更多)。當存在復雜的異步反饋循環時,這也會有所幫助。基于鎖存器的設計可能需要過采樣,因為編譯器必須在鎖存器的兩個級別之間插入延遲。如果存在復雜的反饋路徑,則可能無法始終將此延遲放在最佳位置。

.5x時鐘

這種技術可在某些基于處理器的仿真器上使用,主要用于在最快的設計時鐘運行少量邏輯時。在.5x時鐘中,兩個最快的設計時鐘在一個仿真周期中進行仿真。這可以進一步提高仿真速度超過1倍時鐘,但有一定的限制:只有最快設計時鐘的一個邊沿可能有效,此時鐘不能有復雜的時鐘門控,并且不能有太多的設計邏輯以此速度運行,因為它可以顯著增加模擬設計所需的容量。

使用戶可以靈活地在對齊邊緣時鐘或獨立邊緣之間切換時鐘為各種設計風格提供高異步精度和最快的仿真速度。

基于處理器的仿真器中的內存建模

編譯器將識別用可綜合的Verilog和VHDL RTL代碼編寫的大多數內存并自動處理它們,包括:

多個讀寫端口

端口共享最小化面積/延遲

改變讀/寫依賴性

不同的寫使能(邊緣與電平靈敏度)

同步和異步樣式

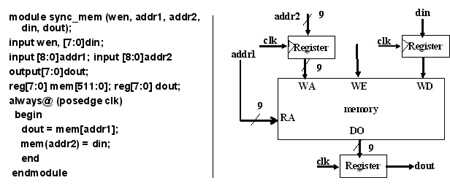

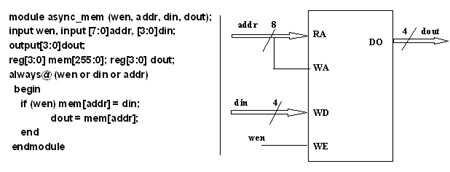

從用戶的Verilog代碼自動建模的兩個存儲器示例如下。

圖12 ??示例:具有邊沿敏感時鐘的同步存儲器是從用戶的Verilog代碼自動生成的

圖13 ??示例:具有電平敏感寫入啟用的異步存儲器是從用戶的Verilog代碼自動生成的。

如果必須手動構建異常存儲器,用戶將在仿真器的原始存儲器單元周圍寫一個“包裝器”以提供必要的回應。

在線仿真接口

輸出時序控制

當與現實世界接口時有時需要控制輸出信號的相對定時。 DRAM存儲器接口就是這樣一個例子??在斷言寫入使能之前,所有地址線必須穩定。

由于基于處理器的仿真器調度邏輯操作按順序發生,因此很容易在仿真周期內對各個(或組)輸出信號添加約束,以控制定時到非常相對于其他輸出信號的高分辨率。然后,編譯器在仿真周期的適當位置調度此輸出計算。基于FPGA的仿真器無法實現這一點,因為它們無法控制設計時鐘內的時序。

圖14 ??基于處理器的仿真器可以高精度調整輸出時序

輸入時序控制

以類似的方式?并出于類似的原因??輸入信號上的定時(“采樣”)可由用戶控制以滿足特定情況。同樣,基于處理器的仿真器可以簡單地調度特定輸入引腳,以便在仿真周期內的其他引腳之前或之后進行采樣。使用基于FPGA的仿真器,用戶必須通過增加某些信號的延遲來“調整”時序,包括一個大的保護頻帶,因為基于FPGA的仿真器無法控制不同邏輯路徑上的絕對時序。對于基于FPGA的仿真器,這是一個命中注定的命題,可能因編譯而異。

摘要結果

硬件加速器和仿真器提供比邏輯仿真器更高的驗證性能,但需要額外的部署工作。在線仿真提供了最高的性能,通常比模擬器快10,000到100,000倍,但需要使用速度緩沖設備圍繞它構建仿真環境。加速器和仿真器要求用戶了解仿真和硅(仿真器和芯片)之間的差異:

仿真有12個或更多狀態,硅只有兩個狀態。

模擬通常按順序執行RTL語句,硅同時“執行”RTL。

模擬是高度交互的,硅不那么。

基于FPGA的仿真器使用商用FPGA,體積更小,功耗更低,而基于處理器的仿真器需要定制芯片設計并消耗更多功率。另一方面,基于處理器的仿真器在十分之一的工作站上編譯設計速度快十倍?分鐘與小時。幾乎所有設計的仿真速度都更快,平均速度提高了2倍。

兩種仿真器都證明了它們在設計中同樣能夠處理大量異步時鐘而不會對性能產生影響。基于處理器的仿真器能夠立即探測新信號并改變觸發條件而無需緩慢的FPGA編譯,這極大地提高了調試的交互性。由于用戶大部分時間都在調試,因此基于處理器的仿真器每天可以提供比基于FPGA的仿真器更多的設計周轉時間。這樣可以縮短新產品的上市時間并提高產品質量。

Ray Turner是Cadence的Incisive Palladium加速器和在線仿真系統的高級產品線經理,該系統是Incisive功能驗證平臺的一部分。在加入Cadence之前,他曾擔任P CAD產品的EDA營銷經理7年。總體而言,Ray在EDA產品的產品管理方面擁有18年的經驗。他還在電信,航空航天,ATE和微處理器行業擁有14年的硬件,軟件和IC設計經驗。

-

處理器

+關注

關注

68文章

19805瀏覽量

233533 -

FPGA

+關注

關注

1643文章

21960瀏覽量

614059 -

仿真器

+關注

關注

14文章

1033瀏覽量

84948

發布評論請先 登錄

基于FPGA的仿真如何工作

基于FPGA的仿真如何工作

評論