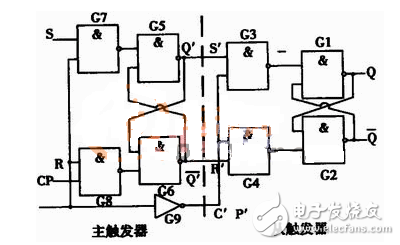

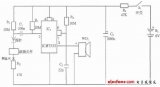

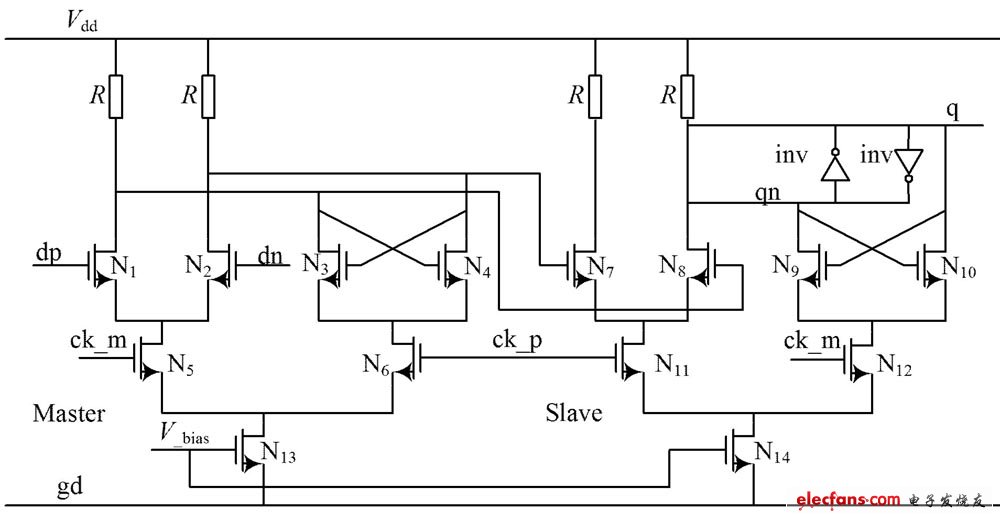

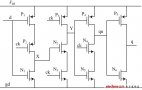

該觸發器由2 個CML 結構鎖存器組成, 它們構成主從型結構, 每個鎖存器都要經過2 個階段: 跟蹤階段和保持階段。當主鎖存器跟蹤輸入信號時, 從鎖存器處于鎖存保持階段, 然后交替。其中N13 , N14 為尾電流管, 偏置電壓V_bias 使N13 , N14管工作在飽和狀態, 充當恒流源的作用。dp 和dn 是由輸入信號d 經傳輸門和反相器產生的一對互補差分信號, ck_m 和ck_p 是由輸入時鐘信號clk 經傳輸門和反相器產生的一對互補時鐘差分信號。主鎖存器工作狀態為: 當ck_m 為高電平時, N5 管導通, N6 管關閉, 此時N1 , N2 管工作在差分狀態, 將輸入信號dp, dn 采入。當ck_p 為高電平時,N6 管導通, N5 管關閉, 此時N3 , N4 使電路維持在鎖存狀態, 從鎖存器工作狀態恰好與主鎖存器工作狀態相反。設計中在觸發器輸出端q, qn 之間加了2 個反相器從而在q, qn 之間形成正反饋, 增強了電路的輸出驅動能力。工作時, 電路的尾電流應當足夠大, 有利于提高電路工作頻率和輸出信號的擺幅。

CML鎖存器構成的主從式觸發器電路

- 鎖存器(40691)

- CML(18766)

- 觸發器電路(9777)

相關推薦

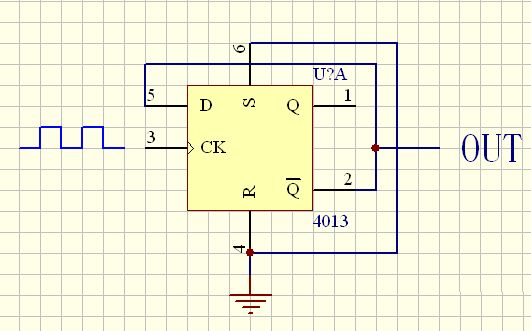

D觸發器與Latch鎖存器電路設計

D觸發器,是時序邏輯電路中必備的一個基本單元,學好 D 觸發器,是學好時序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構成數字電路組合、時序邏輯的基礎。

2023-10-09 17:26:57 234

234

234

234

rs觸發器的置位和復位指令是什么

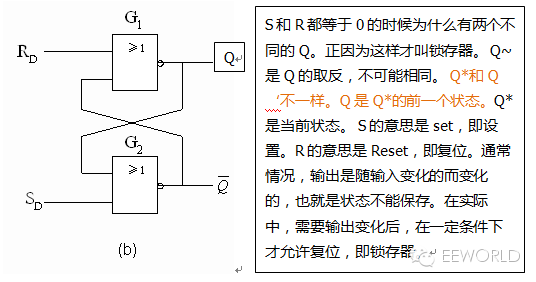

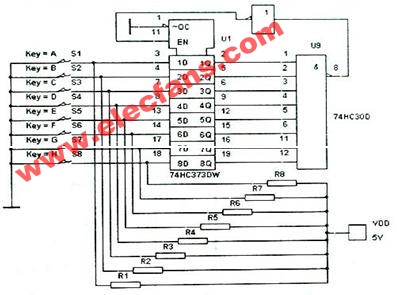

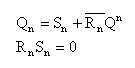

在數字電路中,RS觸發器(也稱為RS鎖存器)是一種基本的雙穩態觸發器,它可以通過特定的輸入信號來實現置位(Set)和復位(Reset)操作。

2023-09-28 16:31:07 1317

1317

1317

1317rs觸發器為什么不能都為1

rs觸發器為什么不能都為1? RS觸發器屬于數字電路中的一種重要的鎖存器。它由兩個輸入端和兩個輸出端組成。理論上,輸入信號可以為任意值,包括1或0。但是,在實際應用中,不能讓RS觸發器的兩個輸入信號

2023-09-17 14:47:12 341

341

341

341rs觸發器和rs鎖存器的區別是什么

在傳統的異步 RS 觸發器中,當輸入的 R 和 S 同時為 1 時,會引發互鎖問題,輸出結果是不確定的。為了避免這個問題,常常使用帶有使能控制的同步觸發器,如帶有時鐘信號的 D 觸發器或 JK 觸發器。這些觸發器在時鐘邊沿上才會響應輸入信號,解決了異步 RS 觸發器的互鎖問題。

2023-08-28 15:44:35 641

641

641

641什么是D觸發器,D觸發器如何工作的?

鎖存器和觸發器有時組合在一起,因為它們都可以在其輸出上存儲一位(1或0)。與鎖存器相比,觸發器是需要時鐘信號(Clk)的同步電路。D 觸發器僅在時鐘從

2023-06-29 11:50:18 5258

5258

5258

5258

FPGA學習之觸發器和鎖存器

鎖存器是構成各種時序電路的基本元件,它的特點是具有0和1兩種穩定的狀態,一旦狀態被確定,就能自行保持,即長期存儲1位的二進制碼,直到有外部信號作用時才有可能改變。鎖存器是一種對電平敏感的存儲單元電路,它們可以在特定輸入電平作用下改變狀態。

2023-03-23 16:03:32 658

658

658

658

鎖存器和觸發器的定義和比較

鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態,當Gate輸入為高電平時,輸入D透明傳輸到輸出Q;當Gate從高變低或者保持低電平時,輸出Q被鎖存保持不變。鎖存器是電平觸發的存儲器。

2023-03-23 14:48:54 1357

1357

1357

1357

數字電路中的RS觸發器詳解

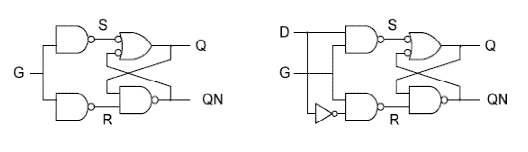

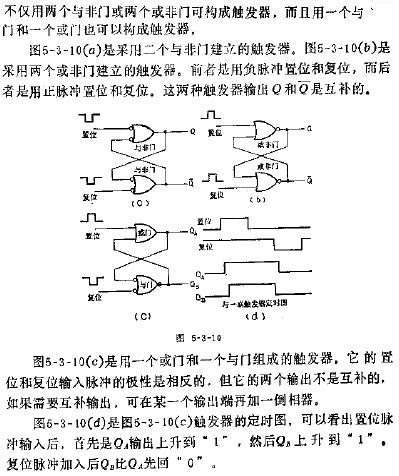

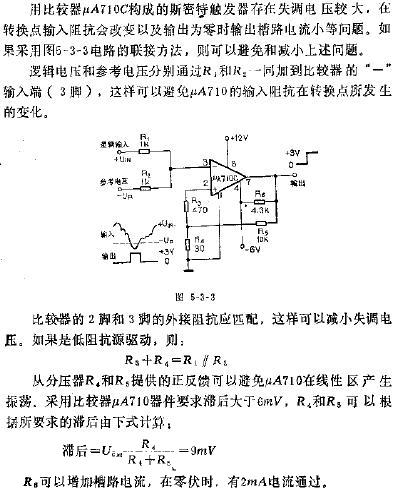

其中R、S分別是英文復位Reset和置位Set的縮寫,作為最簡單的一種觸發器,是構成各種復雜觸發器的基礎。RS觸發器的邏輯電路圖如下圖所示。

2023-02-08 09:19:45 2572

2572

2572

2572一文詳細區分寄存器、鎖存器和觸發器

你有沒有遇到過這樣奇怪的事:你一直以為自己知道某件事,但當你試著向別人解釋它時,你才發現自己的論述中存在漏洞和邏輯上的差異?這就是我最近所遇到的情況,當時有人問我鎖存器和觸發器之間的區別,以及為什么它們都與寄存器有關。

2023-01-30 15:21:15 2073

2073

2073

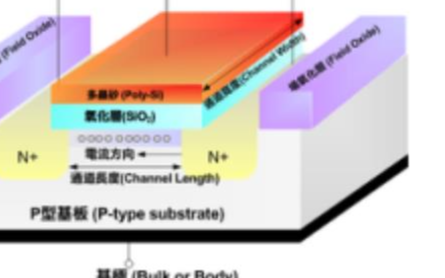

2073解讀從CMOS到觸發器 鎖存器常見結構與鎖存器應用

主要內容: ·雙穩態器件 ·鎖存器常見結構 ·鎖存器的應用 ·觸發器 ·觸發器的建立時間和保持時間 1、雙穩態器件 ** 雙穩態器件**是指穩定狀態有兩種,一種是0,一種是1的器件;雙穩態器件

2023-01-28 09:28:00 2426

2426

2426

2426

鎖存器、觸發器、寄存器的關聯與區別及其相應的verilog描述

1:鎖存器、觸發器、寄存器的關聯與區別 首先應該明確鎖存器和觸發器是由與非門之類的東西構成。尤其是鎖存器,雖說數字電路定義含有鎖存器或觸發器的電路叫時序電路,但鎖存器有很多組合邏輯電路的特性。 鎖存

2022-12-19 12:25:01 3721

3721

3721

3721淺談四種入門觸發器

來源:羅姆半導體社區 觸發器的電路圖由邏輯門組合而成,其結構均由R-S鎖存器派生而來(廣義的觸發器包括鎖存器)。觸發器可以處理輸入、輸出信號和時鐘頻率之間的相互影響。 在R-S鎖存器的前面加一個由

2022-11-29 17:35:40 1584

1584

1584

1584rs觸發器電路圖與rs觸發器內部電路圖

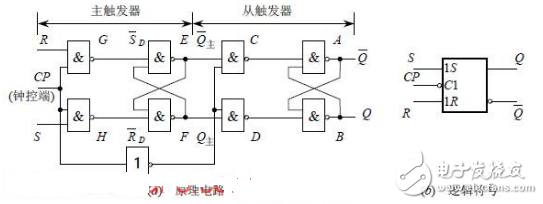

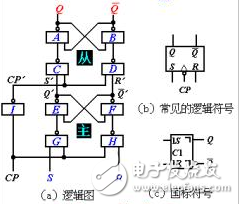

rs觸發器電路圖與rs觸發器內部電路圖 rs觸發器電路圖 主從RS觸發器電路圖: 主從觸發器由兩級觸發器構成,其中一級接收輸入信號,其狀態直接由輸入信號決定,稱為主觸發器,還有一級的輸入與主觸發器

2022-10-19 19:16:03 16964

16964

16964

16964

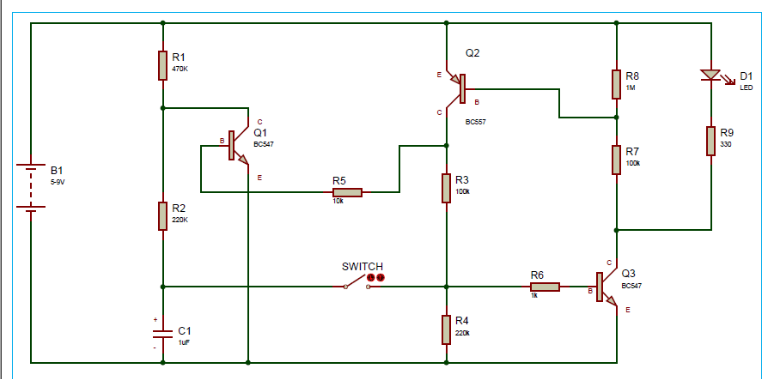

如何制作一個軟鎖存電路

電路中,電路只能被鎖存到一種狀態,并且可以改變需要移除電源的狀態。通常移位寄存器和觸發器用于鎖存電路,就像我們在Clap-on-Clap-off 電路中使用的一樣。

2022-08-25 16:32:47 2779

2779

2779

2779

FDCE/FDPE/FDRE/FDSE觸發器簡介

每個 Slice 有 8 個 FF 。四個可以配置為 D 型觸發器或電平敏感鎖存器,另外四個只能配置為 D 型觸發器,但是需要記得是:當原來的四個 FF 配置為鎖存器時,不能使用這四個 FF 。

2022-03-15 11:59:34 7158

7158

7158

7158基本RS觸發器實驗

新課第五章 觸發器5.1 概述1、觸發器具有“記憶”功能,它是構成時序邏輯電路的基本單元。本章首先介紹基本RS觸發器的組成原理、特點和邏輯功能。然后引出能夠防止“空翻”現象的主從觸發器和邊沿觸發器。同時,較詳細地討論RS觸發器、JK觸發器、D觸發器、T觸發器、T'觸發器的邏輯功能及其描述方法。

2009-04-02 11:58:41

8位CPU設計(1) 門電路和鎖存器、觸發器

這是一個系列文章,從最簡單的門電路介紹,從基礎的鎖存器、觸發器、編碼器、譯碼器等一系列數字邏輯電路開始,最終構造一個簡易版的CPU實物

2021-11-06 09:20:58 16

16

16

16鎖存器與寄存器有哪些區別

首先應該明確鎖存器和觸發器也是由與非門之類的東西構成。尤其是鎖存器,雖說數字電路定義含有鎖存器或觸發器的電路叫時序電路,但鎖存器有很多組合電路的特性。 組合電路就是一個真值表,一個函數,一組輸入對應

2021-08-12 10:26:12 3567

3567

3567

3567鎖存器與觸發器的區別

,鎖存器有兩個輸入,一個是有效信號EN,一個是輸入數據信號DATA_IN,有一個輸出Q,它的功能就是在EN有效的時候把DATA_IN的值傳給Q,也就是鎖存的過程。 2)觸發器 觸發器(Flip-Flop,簡寫為FF)也叫雙穩態門,又稱雙穩態觸發器,是一種可以在兩種

2020-11-29 11:02:11 20662

20662

20662

20662FPGA的設計中為什么避免使用鎖存器

文章都對鎖存器有個誤解,我們后面會詳細說明。 這篇文章,我們包含如下內容: ①鎖存器、觸發器和寄存器的原理和區別,為什么鎖存器不好? ② 什么樣的代碼會產生鎖存器? ③ 為什么鎖存器依然存在于FPGA中? 鎖存器、觸發器和寄存器的原理和區別,為什么鎖存器

2020-11-16 11:42:00 7206

7206

7206

7206

JK觸發器邏輯符號_jk觸發器的特性方程

JK觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能,在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

2019-11-08 14:48:44 79652

79652

79652

79652

如何操作基本類型的鎖存器和觸發器

鎖存器(有時也稱為S/R鎖存器)是最小的存儲器塊。它們可以使用兩個NOR邏輯門(S和R為高電平有效)或兩個NAND門(輸入為低電平有效)構建,并用于構建更復雜的鎖存器和觸發器。

2019-07-30 11:23:28 5658

5658

5658

5658

d觸發器邏輯電路及符號

CP=1時,門。。打開,門。。被封鎖,從觸發器保持原來狀態不變,D信號進入主觸發器。但是要特別注意,這時主觸發器只跟隨而不鎖存,即。。跟隨D變化,D怎么變。。也隨之怎么變。

2019-07-15 08:57:32 42337

42337

42337

42337

D型觸發器電路真值表和計數器數的據鎖存器摘要

D型觸發器是一個改進的置位復位觸發器,增加了一個反相器,由此可見以防止S和R輸入處于相同的邏輯電平,此狀態將強制兩個輸出都處于邏輯“1”,超越反饋鎖存動作,無論哪個輸入先進入邏輯電平“1”都將失去控制,而另一個仍處于邏輯“0”的輸入控制鎖存器的結果狀態。

2019-06-26 15:36:28 14537

14537

14537

14537

鎖存器Lacth & 觸發器Flip-flop就是實現儲存功能的兩種邏輯單元電路

觸發器按邏輯功能分類有D觸發器、JK觸發器、T觸發器和SR觸發器。它們的功能可用特性表、特性方程和狀態圖來描述。觸發器的電路結構與邏輯功能沒有必然聯系。例如JK觸發器既有主從結構也有維持阻塞或利用傳輸延遲結構。每一種邏輯功能的觸發器都可以通過增加門電路和適當的外部連線轉換為其它功能的觸發器。

2019-04-12 14:04:18 7875

7875

7875

7875

數字電路教程之觸發器課件的詳細資料說明

本文檔的主要內容詳細介紹的是數字電路教程之觸發器課件的詳細資料說明主要內容包括了:一 SR鎖存器,二 電平觸發的觸發器,三 脈沖觸發的觸發器,四 邊沿觸發的觸發器,五 觸發器的邏輯功能及其描述方法

2018-12-28 08:00:00 17

17

17

17鎖存器Latch和觸發器Flip-flop有何區別

本文首先介紹了鎖存器Latch結構和鎖存器latch的優缺點,其次介紹了觸發器Flip-flop的結構與優缺點,最后介紹了鎖存器Latch和觸發器Flip-flop兩者之間的區別。

2018-04-18 14:10:10 128942

128942

128942

128942

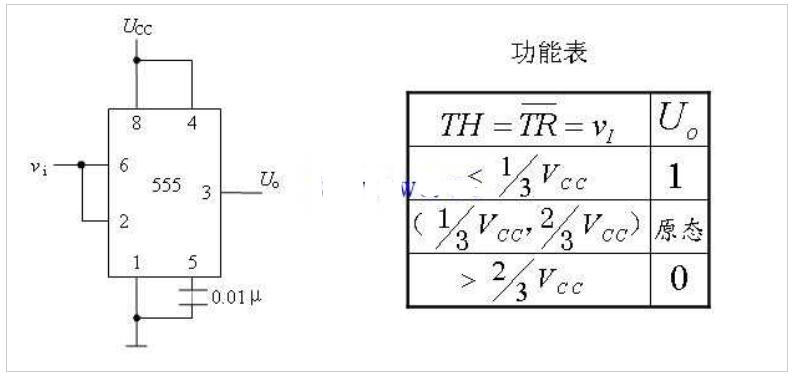

什么是單穩態觸發器_單穩態觸發器特點以及構成

本文開始介紹了什么是單穩態觸發器以及單穩態觸發器的電路組成,其次闡述了單穩態觸發器特點、門電路構成的單穩態觸發器、D觸發器構成的單穩態觸發器,最后詳細的闡述了時基電路構成的單穩態觸發器。

2018-03-27 09:24:23 68948

68948

68948

68948

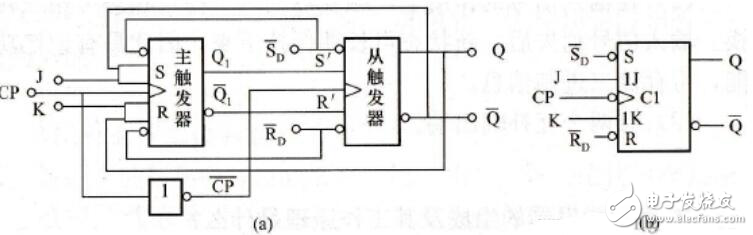

主從sr觸發器基本原理分析

主從觸發器的工作分兩步進行。第一步,當CP由0跳變到1及CP=1期間,主觸發器接收輸入信號激勵,狀態發生變化;而主從sr觸發器基本原理分析由1變為0,主從sr觸發器基本原理分析=0,從觸發器被封

2018-02-08 14:07:03 58179

58179

58179

58179

主從rs觸發器特性表及特性方程

主從觸發器由兩級觸發器構成,其中一級接收輸入信號,其狀態直接由輸入信號決定,稱為主觸發器,還有一級的輸入與主觸發器的輸出連接,其狀態由主觸發器的狀態決定,稱為從觸發器。

2018-02-08 13:49:43 48291

48291

48291

48291

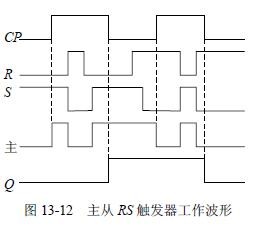

主從rs觸發器波形圖介紹

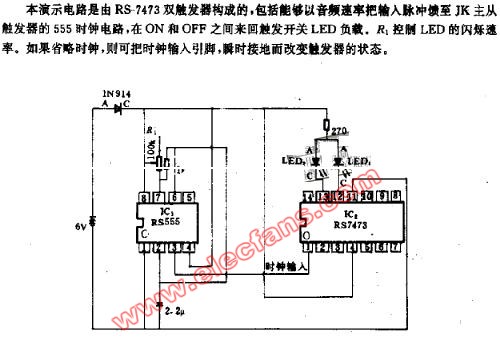

主從觸發器由主觸發器和從觸發器組成,時鐘信號CP經由非門,變成CP’控制從觸發器。當CP=1時,CP‘=0,主觸發器動作,從觸發器被封鎖;當CP=0時,CP’=1,主觸發器被封鎖,從觸發器動作。

2018-02-08 13:40:39 19198

19198

19198

19198

d鎖存器與sr鎖存器的區別

鎖存器就是把單片機的輸出的數據先存起來,可以讓單片機繼續做其它事。它的LE為高的時候,數據就可以通過它。當為低時,它的輸出端就會被鎖定RS觸發器是構成其它各種功能觸發器的基本組成部分。又稱為基本RS觸發器。

2018-01-31 14:48:13 28618

28618

28618

28618

jk觸發器是什么原理_jk觸發器特性表和狀態轉換圖

JK觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能,在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

2017-12-25 17:30:03 172587

172587

172587

172587

鎖存器和觸發器的區別

鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態 鎖存器是電平觸發的存儲單元,數據存儲的動作取決于輸入時鐘(或者使能)信號的電平值,僅當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。

2017-11-02 09:24:41 92855

92855

92855

92855

鎖存器的主要作用有哪些?

所謂鎖存器,就是輸出端的狀態不會隨輸入端的狀態變化而變化,僅在有鎖存信號時輸入的狀態被保存到輸出,直到下一個鎖存信號到來時才改變。典型的鎖存器邏輯電路是 D 觸發器電路。 PS:鎖存信號(即對LE賦高電平時Data端的輸入信號)。鎖存,就是把信號暫存以維持某種電平狀態。

2017-10-30 14:35:53 58733

58733

58733

58733

什么是觸發器?鎖存器和觸發器的區別?

觸發器的功能:

① 完成比約束更復雜的數據約束:觸發器可以實現比約束更為復雜的數據約束

② 檢查所做的SQL是否允許:觸發器可以檢查SQL所做的操作是否被允許。例如:在產品庫存表里,如果

2017-08-19 12:05:00 41369

41369

41369

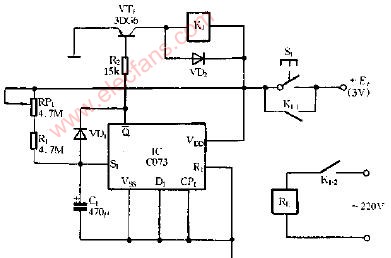

41369555定時器構成的單穩態觸發器為基礎的測試電路

555定時器構成的單穩態觸發器為基礎的測試電路根據雙向導電元件的導電原理,利用555 定時器構成的單穩態觸發器的觸發反應,驅動蜂鳴器發聲,顯示測試結果。

2012-06-09 16:43:28 16200

16200

16200

16200

觸發器與時序邏輯電路

一、基本要求1、理解R-S觸發器、J-K觸發器和D觸發器的邏輯功能;2、掌握觸發器構成的時序電路的分析,并了解其設計方法;3、理解計數器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57

57

57主從觸發器(master-slave flip-flop)基

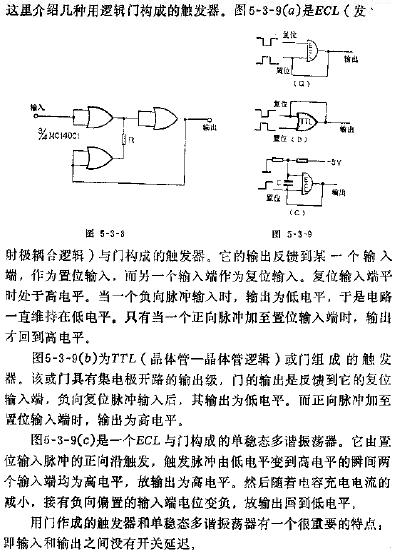

圖13-11(a)所示為主從RS觸發器原理電路。它是由兩個高電平觸發方式的同步RS觸發器構成。其中門E、F、G、H構成主觸發器,時鐘信號為CP,輸出為Q、

2010-08-19 09:09:10 5980

5980

5980

5980

鎖存器和觸發器原理

1、掌握鎖存器、觸發器的電路結構和工作原理;

2、熟練掌握SR觸發器、JK觸發器、D觸發器及T 觸發器的邏輯功能;

3、正確理解鎖存器、觸發器的動態特性

2010-08-18 16:39:35 233

233

233

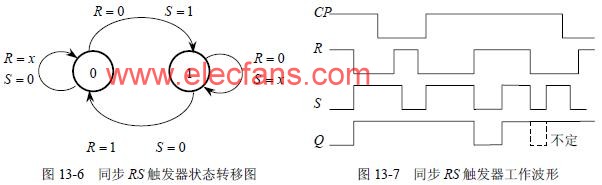

233同步RS觸發器原理

由與非門構成的同步RS觸發器如圖13-5(a)所示,其邏輯符號如圖13-5(b)所示。圖中門A和B構成基本觸發器,門C和E構成觸發引導電路。由圖13-5(a)可見,基本觸發器的輸

2010-08-18 09:00:00 14775

14775

14775

14775

主從觸發器,主從觸發器的原理和特點有哪些?

主從觸發器,主從觸發器的原理和特點有哪些?

1.電路組成和符號 主從RS觸發器電路和邏輯符號如圖Z1406所示。其中A、

2010-03-08 14:06:10 11423

11423

11423

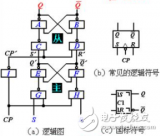

11423JK觸發器原理是什么?

JK觸發器原理是什么?

JK觸發器是一種功能較完善,應用很廣泛的雙穩態觸發器。圖9-5(a)所示是一種典型結構的JK觸發器——主從型JK觸

2010-03-08 13:41:11 23241

23241

23241

23241JK觸發器,JK觸發器是什么意思

JK觸發器,JK觸發器是什么意思

1.主從JK觸發器主從結構觸發器也可以徹底解決直接控制,防止空翻。這里以性能優良、廣泛使用的主從JK觸發器為

2010-03-08 13:36:29 5842

5842

5842

5842RS觸發器的芯片介紹

74LS71 與輸入R—S主從觸發器(帶預置和清除端)

74279、74LS279、74HC279 四/R—/S鎖存器雙嵌位輸入,圖騰柱輸出。

2008-01-22 12:45:32 26171

26171

26171

26171 電子發燒友App

電子發燒友App

評論