大多數(shù)數(shù)字系統(tǒng)中,除了需要具有邏輯運(yùn)算和算術(shù)運(yùn)算功能的組合邏輯電路外,還需要具有儲(chǔ)存功能的電路,組合邏輯電路和儲(chǔ)存電路相結(jié)合可構(gòu)成時(shí)序邏輯電路,鎖存器Lacth& 觸發(fā)器Flip-flop就是實(shí)現(xiàn)儲(chǔ)存功能的兩種邏輯單元電路。

鎖存器是對(duì)電平敏感的電路,它們?cè)谝欢娖阶饔孟赂淖儬顟B(tài)。基本SR鎖存器由輸入信號(hào)電平直接控制其狀態(tài),傳輸門控或邏輯門控鎖存器在使能電平作用下由輸入信號(hào)決定其狀態(tài)。在使能信號(hào)作用期間,門控鎖存器輸出跟隨輸入信號(hào)變化而變化。

觸發(fā)器則是對(duì)時(shí)鐘脈沖邊沿敏感的電路,根據(jù)不同的電路結(jié)構(gòu),它們?cè)跁r(shí)鐘脈沖的上升沿或下降沿作用下改變狀態(tài)。目前流行的觸發(fā)器電路主要有主從、維持阻塞和利用傳輸延遲等幾種結(jié)構(gòu),它們的工作原理個(gè)不相同。

觸發(fā)器按邏輯功能分類有D觸發(fā)器、JK觸發(fā)器、T觸發(fā)器和SR觸發(fā)器。它們的功能可用特性表、特性方程和狀態(tài)圖來描述。觸發(fā)器的電路結(jié)構(gòu)與邏輯功能沒有必然聯(lián)系。例如JK觸發(fā)器既有主從結(jié)構(gòu)也有維持阻塞或利用傳輸延遲結(jié)構(gòu)。每一種邏輯功能的觸發(fā)器都可以通過增加門電路和適當(dāng)?shù)耐獠窟B線轉(zhuǎn)換為其它功能的觸發(fā)器。

之所以能夠有記憶功能能夠存儲(chǔ)信息,最主要的就是它把輸出有反饋到了輸入,形成了反饋這樣它就能保持穩(wěn)定。這使得Lacth & Flip-flop與組合邏輯電路的分析有了很大的不同,當(dāng)然Latch & Flip-flop本來就只有這么幾種,記住就行。不需要自己去創(chuàng)新。

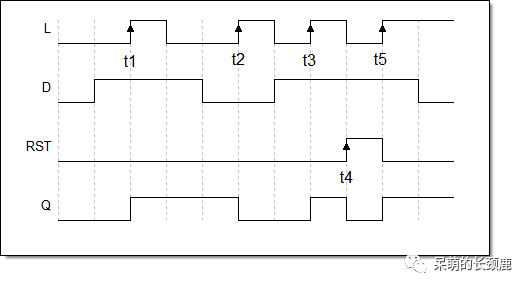

從最基本的用兩個(gè)或非門構(gòu)成的SR鎖存器到在前面加上兩個(gè)與門和一個(gè)使能端E的邏輯門控SR鎖存器,這樣就可以實(shí)現(xiàn)多個(gè)鎖存器同步進(jìn)行數(shù)據(jù)鎖存。但是SR鎖存器有個(gè)很不好的地方就是當(dāng)SR同時(shí)為1的時(shí)候,它會(huì)出現(xiàn)不確定狀態(tài),解決這個(gè)問題其實(shí)也很簡單在邏輯門SR鎖存器的S和R之間串上一個(gè)非門這樣S和R永遠(yuǎn)都不會(huì)一樣,當(dāng)然同時(shí)為0的狀態(tài)時(shí)有使能端E決定的,這個(gè)就是D鎖存器,當(dāng)E為1時(shí),輸出Q = D;當(dāng)E為0時(shí),輸出Q保持之前的狀態(tài)不變。再講了傳輸門門控D鎖存器,大致工作原理是當(dāng)E為1的時(shí)候,放輸入信號(hào)進(jìn)來,當(dāng)E為0時(shí),鎖存前一時(shí)刻(E=1時(shí))的數(shù)據(jù),后來就提出了在時(shí)序圖中的幾個(gè)基本概念:建立時(shí)間(Tsu)、保持時(shí)間(Th)、脈沖寬度(Tw)和傳輸延遲時(shí)間()。

觸發(fā)器的電路結(jié)構(gòu)就不仔細(xì)分析了,關(guān)鍵是看看幾種觸發(fā)器的邏輯功能,觸發(fā)器在每次時(shí)鐘脈沖觸發(fā)沿到來之前的狀態(tài)稱為現(xiàn)態(tài),而在此之后的狀態(tài)稱為次態(tài)。所謂觸發(fā)器的邏輯功能,是指次態(tài)與現(xiàn)態(tài)、輸入信號(hào)之間的邏輯關(guān)系。

D觸發(fā)器功能比較簡單,輸出Q的值直接等于輸入D就行。JK觸發(fā)器由特性表,特性方程或狀態(tài)圖都可以看出,當(dāng)J=1,K=0時(shí),觸發(fā)器的下一個(gè)狀態(tài)被置1;當(dāng)J=0,K=1時(shí),將被置0;當(dāng)J=K=0時(shí),觸發(fā)器狀態(tài)保持不變;當(dāng)J=K=1時(shí),觸發(fā)器翻轉(zhuǎn)。在所有類型的觸發(fā)器中JK觸發(fā)器具有最強(qiáng)的邏輯功能,它能執(zhí)行置1、置0、保持和翻轉(zhuǎn)四種操作,并可以簡單的附加電路轉(zhuǎn)換為其他功能的觸發(fā)器,因此在數(shù)字電路中被廣泛應(yīng)用。在某些場合,需要對(duì)計(jì)數(shù)功能進(jìn)行控制,當(dāng)控制信號(hào)T=1時(shí),每來一個(gè)CP脈沖,它的狀態(tài)翻轉(zhuǎn)一次;而當(dāng)T=0時(shí),則不對(duì)CP信號(hào)做出響應(yīng)而保持狀態(tài)不變。這就是T觸發(fā)器。其實(shí)T觸發(fā)器很簡單就是把JK觸發(fā)器的JK兩端接在了一起。僅有置位、復(fù)位功能的觸發(fā)器稱為SR觸發(fā)器,并且還有約束條件SR=0。

各種觸發(fā)器之間是可以很輕松的相互轉(zhuǎn)換的,要會(huì)靈活應(yīng)用。

鎖存器能根據(jù)輸入端把結(jié)果自行保持;觸發(fā)器是指由時(shí)鐘邊沿觸發(fā)的存儲(chǔ)器單元;由敏感信號(hào)(電平,邊沿)控制的鎖存器就是觸發(fā)器;

寫電路時(shí),產(chǎn)生鎖存器的原因:

if語句中,沒有寫else,默認(rèn)保持原值,產(chǎn)生鎖存器,可能不是想要的結(jié)果;

case語句中,沒有寫完整default項(xiàng),也容易產(chǎn)生鎖存器;

例子:

always@(a or b)

begin

if(a) q=b;

end

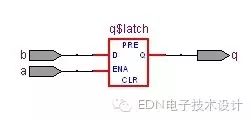

產(chǎn)生了鎖存器,如下

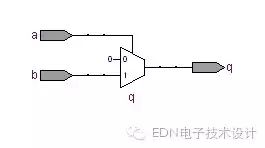

沒有鎖存器的情況

always@(a or b)

begin

if(a) q=b;

else q=0;

end

避免使用D鎖存器,盡量使用D觸發(fā)器

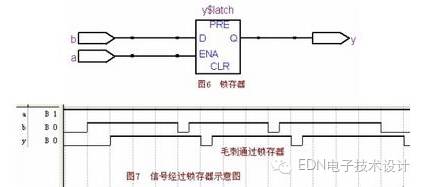

D鎖存器

moduletest_latch(y,a,b);

outputy;inputa;inputb;regy;

always@(aorb)begin

if(a==1’b1)

y=b;

endendmodule

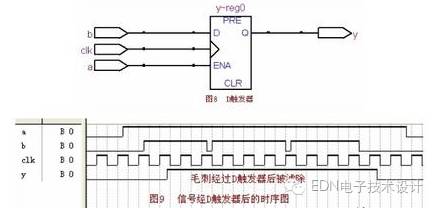

D觸發(fā)器

moduletest_d(y,clk,a,b);

outputy;inputclk;inputa;inputb;regy; always@(posedgeclk)begin if(a==1'b1)

y=b;

endendmodule

從圖8可知,例10對(duì)應(yīng)的電路是D觸發(fā)器。信號(hào)a被綜合成D觸發(fā)器的使能端,只有在時(shí)鐘上沿到來且a為高時(shí),b信號(hào)的值才能傳遞給a;只要在時(shí)鐘上升沿期間信號(hào)b是穩(wěn)定,即使在其他時(shí)候b還有毛刺,經(jīng)過D觸發(fā)器后數(shù)據(jù)是穩(wěn)定的,毛刺被濾除。

-

電路

+關(guān)注

關(guān)注

173文章

6022瀏覽量

174425 -

鎖存器

+關(guān)注

關(guān)注

8文章

922瀏覽量

42113 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2032瀏覽量

61877

原文標(biāo)題:鎖存器Latch和觸發(fā)器Flip-flop有何區(qū)別?

文章出處:【微信號(hào):mcu168,微信公眾號(hào):硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

鎖存器Lacth & 觸發(fā)器Flip-flop就是實(shí)現(xiàn)儲(chǔ)存功能的兩種邏輯單元電路

鎖存器Lacth & 觸發(fā)器Flip-flop就是實(shí)現(xiàn)儲(chǔ)存功能的兩種邏輯單元電路

評(píng)論