完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > fifo

First Input First Output的縮寫,先入先出隊(duì)列,這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。

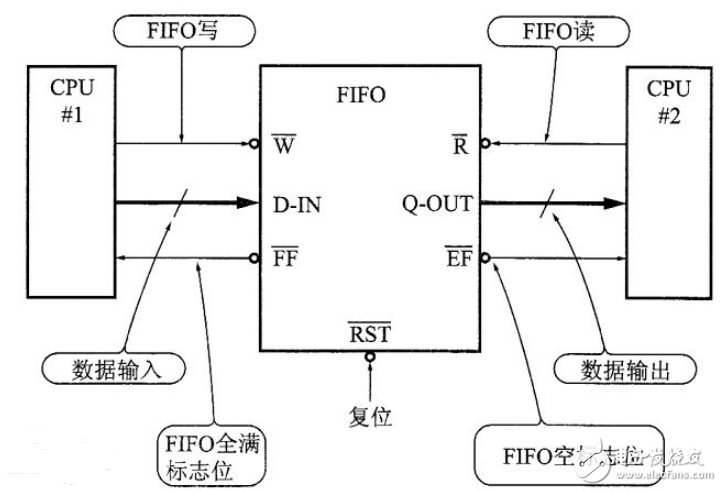

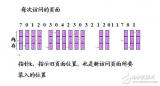

在計(jì)算機(jī)中,先入先出隊(duì)列是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令(指令就是計(jì)算機(jī)在響應(yīng)用戶操作的程序代碼,對(duì)用戶而言是透明的)。如圖1所示,當(dāng)CPU在某一時(shí)段來不及響應(yīng)所有的指令時(shí),指令就會(huì)被安排在FIFO隊(duì)列中,比如0號(hào)指令先進(jìn)入隊(duì)列,接著是1號(hào)指令、2號(hào)指令……當(dāng)CPU完成當(dāng)前指令以后就會(huì)從隊(duì)列中取出0號(hào)指令先行執(zhí)行,此時(shí)1號(hào)指令就會(huì)接替0號(hào)指令的位置,同樣,2號(hào)指令、3號(hào)指令……都會(huì)向前挪一個(gè)位置,這樣解釋大家清楚了吧?

First Input First Output的縮寫,先入先出隊(duì)列,這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。

FIFO簡(jiǎn)介

在計(jì)算機(jī)中,先入先出隊(duì)列是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令(指令就是計(jì)算機(jī)在響應(yīng)用戶操作的程序代碼,對(duì)用戶而言是透明的)。如圖1所示,當(dāng)CPU在某一時(shí)段來不及響應(yīng)所有的指令時(shí),指令就會(huì)被安排在FIFO隊(duì)列中,比如0號(hào)指令先進(jìn)入隊(duì)列,接著是1號(hào)指令、2號(hào)指令……當(dāng)CPU完成當(dāng)前指令以后就會(huì)從隊(duì)列中取出0號(hào)指令先行執(zhí)行,此時(shí)1號(hào)指令就會(huì)接替0號(hào)指令的位置,同樣,2號(hào)指令、3號(hào)指令……都會(huì)向前挪一個(gè)位置,這樣解釋大家清楚了吧?

![]()

圖1 先進(jìn)先出隊(duì)列FIFO是隊(duì)列機(jī)制中最簡(jiǎn)單的,每個(gè)接口上都存在FIFO隊(duì)列,表面上看FIFO隊(duì)列并沒有提供什么QoS(Quality of Service,服務(wù)質(zhì)量)保證,甚至很多人認(rèn)為FIFO嚴(yán)格意義上不算做一種隊(duì)列技術(shù),實(shí)則不然,F(xiàn)IFO是其它隊(duì)列的基礎(chǔ),F(xiàn)IFO也會(huì)影響到衡量QoS的關(guān)鍵指標(biāo):報(bào)文的丟棄、延時(shí)、抖動(dòng)。既然只有一個(gè)隊(duì)列,自然不需要考慮如何對(duì)報(bào)文進(jìn)行復(fù)雜的流量分類,也不用考慮下一個(gè)報(bào)文怎么拿、拿多少的問題,而且因?yàn)榘错樞蛉?bào)文,F(xiàn)IFO無需對(duì)報(bào)文重新排序。簡(jiǎn)化了這些實(shí)現(xiàn)其實(shí)也就提高了對(duì)報(bào)文時(shí)延的保證。FIFO關(guān)心的就是隊(duì)列長(zhǎng)度問題,隊(duì)列長(zhǎng)度會(huì)影響到時(shí)延、抖動(dòng)、丟包率。因?yàn)殛?duì)列長(zhǎng)度是有限的,有可能被填滿,這就涉及到該機(jī)制的丟棄原則。常見的一個(gè)丟棄原則叫做Tail Drop機(jī)制。簡(jiǎn)單地說就是該隊(duì)列如果已經(jīng)滿了,那么后續(xù)進(jìn)入的報(bào)文被丟棄,而沒有什么機(jī)制來保證后續(xù)的報(bào)文可以擠掉已經(jīng)在隊(duì)列內(nèi)的報(bào)文。在這種機(jī)制中,如果定義了較長(zhǎng)的隊(duì)列長(zhǎng)度,那么隊(duì)列不容易填滿,被丟棄的報(bào)文也就少了,但是隊(duì)列長(zhǎng)度太長(zhǎng)了會(huì)出現(xiàn)時(shí)延的問題,一般情況下時(shí)延的增加會(huì)導(dǎo)致抖動(dòng)也增加。如果定義了較短的隊(duì)列,時(shí)延的問題可以得到解決,但是發(fā)生Tail Drop的報(bào)文就變多了。

FIFO隊(duì)列原理簡(jiǎn)述

FIFO隊(duì)列不對(duì)報(bào)文進(jìn)行分類,當(dāng)報(bào)文進(jìn)入接口的速度大于接口能發(fā)送的速度時(shí),F(xiàn)IFO按報(bào)文到達(dá)接口的先后順序讓報(bào)文進(jìn)入隊(duì)列,同時(shí),F(xiàn)IFO在隊(duì)列的出口讓報(bào)文按進(jìn)隊(duì)的順序出隊(duì),先進(jìn)的報(bào)文將先出隊(duì),后進(jìn)的報(bào)文將后出隊(duì)。FIFO隊(duì)列具有處理簡(jiǎn)單,開銷小的優(yōu)點(diǎn)。但FIFO不區(qū)分報(bào)文類型,采用盡力而為的轉(zhuǎn)發(fā)模式,使對(duì)時(shí)間敏感的實(shí)時(shí)應(yīng)用(如VoIP)的延遲得不到保證,關(guān)鍵業(yè)務(wù)的帶寬也不能得到保證。

使用FIFO

FIFO一般用于不同時(shí)鐘域之間的數(shù)據(jù)傳輸,比如FIFO的一端是AD數(shù)據(jù)采集,另一端是計(jì)算機(jī)的PCI總線,假設(shè)其AD采集的速率為16位 100K SPS,那么每秒的數(shù)據(jù)量為100K×16bit=1.6Mbps,而PCI總線的速度為33MHz,總線寬度32bit,其最大傳輸速率為1056Mbps,在兩個(gè)不同的時(shí)鐘域間就可以采用FIFO來作為數(shù)據(jù)緩沖。另外對(duì)于不同寬度的數(shù)據(jù)接口也可以用FIFO,例如單片機(jī)位8位數(shù)據(jù)輸出,而DSP可能是16位數(shù)據(jù)輸入,在單片機(jī)與DSP連接時(shí)就可以使用FIFO來達(dá)到數(shù)據(jù)匹配的目的。

重要參數(shù)

FIFO的寬度:也就是英文資料里常看到的THE WIDTH,它指的是FIFO一次讀寫操作的數(shù)據(jù)位,就像MCU有8位和16位,ARM32位等等,F(xiàn)IFO的寬度在單片成品IC中是固定的,也有可選擇的,如果用FPGA自己實(shí)現(xiàn)一個(gè)FIFO,其數(shù)據(jù)位,也就是寬度是可以自己定義的。

FIFO的深度:THE DEEPTH,它指的是FIFO可以存儲(chǔ)多少個(gè)N位的數(shù)據(jù)(如果寬度為N)。如一個(gè)8位的FIFO,若深度為8,它可以存儲(chǔ)8個(gè)8位的數(shù)據(jù),深度為12 ,就可以存儲(chǔ)12個(gè)8位的數(shù)據(jù),F(xiàn)IFO的深度可大可小,個(gè)人認(rèn)為FIFO深度的計(jì)算并無一個(gè)固定的公式。在FIFO實(shí)際工作中,其數(shù)據(jù)的滿/空標(biāo)志可以控制數(shù)據(jù)的繼續(xù)寫入或讀出。在一個(gè)具體的應(yīng)用中不可能由一些參數(shù)精確算出所需的FIFO深度為多少,這在寫速度大于讀速度的理想狀態(tài)下是可行的,但在實(shí)際中用到的FIFO深度往往要大于計(jì)算值。一般來說根據(jù)電路的具體情況,在兼顧系統(tǒng)性能和FIFO成本的情況下估算一個(gè)大概的寬度和深度就可以了。而對(duì)于寫速度慢于讀速度的應(yīng)用,F(xiàn)IFO的深度要根據(jù)讀出的數(shù)據(jù)結(jié)構(gòu)和讀出數(shù)據(jù)由那些具體的要求來確定。

滿標(biāo)志:FIFO已滿或?qū)⒁獫M時(shí)由FIFO的狀態(tài)電路送出的一個(gè)信號(hào),以阻止FIFO的寫操作繼續(xù)向FIFO中寫數(shù)據(jù)而造成溢出(overflow)。

空標(biāo)志:FIFO已空或?qū)⒁諘r(shí)由FIFO的狀態(tài)電路送出的一個(gè)信號(hào),以阻止FIFO的讀操作繼續(xù)從FIFO中讀出數(shù)據(jù)而造成無效數(shù)據(jù)的讀出(underflow)。

讀時(shí)鐘:讀操作所遵循的時(shí)鐘,在每個(gè)時(shí)鐘沿來臨時(shí)讀數(shù)據(jù)。

寫時(shí)鐘:寫操作所遵循的時(shí)鐘,在每個(gè)時(shí)鐘沿來臨時(shí)寫數(shù)據(jù)。

讀指針:指向下一個(gè)讀出地址。讀完后自動(dòng)加1。

寫指針:指向下一個(gè)要寫入的地址的,寫完自動(dòng)加1。

讀寫指針其實(shí)就是讀寫的地址,只不過這個(gè)地址不能任意選擇,而是連續(xù)的。

4.FIFO的分類

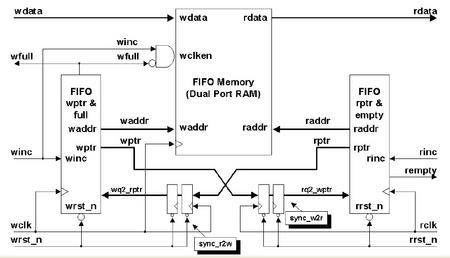

根據(jù)FIFO工作的時(shí)鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時(shí)鐘和寫時(shí)鐘為同一個(gè)時(shí)鐘。在時(shí)鐘沿來臨時(shí)同時(shí)發(fā)生讀寫操作。異步FIFO是指讀寫時(shí)鐘不一致,讀寫時(shí)鐘是互相獨(dú)立的。

5.FIFO設(shè)計(jì)的難點(diǎn)

FIFO設(shè)計(jì)的難點(diǎn)在于怎樣判斷FIFO的空/滿狀態(tài)。為了保證數(shù)據(jù)正確的寫入或讀出,而不發(fā)生溢出或讀空的狀態(tài)出現(xiàn),必須保證FIFO在滿的情況下,不能進(jìn)行寫操作。在空的狀態(tài)下不能進(jìn)行讀操作。怎樣判斷FIFO的滿/空就成了FIFO設(shè)計(jì)的核心問題。由于同步FIFO幾乎很少用到,這里只描述異步FIFO的空/滿標(biāo)志產(chǎn)生問題。

在用到觸發(fā)器的設(shè)計(jì)中,不可避免的會(huì)遇到亞穩(wěn)態(tài)的問題(關(guān)于亞穩(wěn)態(tài)這里不作介紹,可查看相關(guān)資料)。在涉及到觸發(fā)器的電路中,亞穩(wěn)態(tài)無法徹底消除,只能想辦法將其發(fā)生的概率將到最低。其中的一個(gè)方法就是使用格雷碼。格雷碼在相鄰的兩個(gè)碼元之間只由一位變換(二進(jìn)制碼在很多情況下是很多碼元在同時(shí)變化)。這就會(huì)避免計(jì)數(shù)器與時(shí)鐘同步的時(shí)候發(fā)生亞穩(wěn)態(tài)現(xiàn)象。但是格雷碼有個(gè)缺點(diǎn)就是只能定義2^n的深度,而不能像二進(jìn)制碼那樣隨意的定義FIFO的深度,因?yàn)楦窭状a必須循環(huán)一個(gè)2^n,否則就不能保證兩個(gè)相鄰碼元之間相差一位的條件,因此也就不是真正的格雷碼了。第二就是使用冗余的觸發(fā)器,假設(shè)一個(gè)觸發(fā)器發(fā)生亞穩(wěn)態(tài)的概率為P,那么兩個(gè)級(jí)聯(lián)的觸發(fā)器發(fā)生亞穩(wěn)態(tài)的概率就為P的平方。但這會(huì)導(dǎo)致延時(shí)的增加。亞穩(wěn)態(tài)的發(fā)生會(huì)使得FIFO出現(xiàn)錯(cuò)誤,讀/寫時(shí)鐘采樣的地址指針會(huì)與真實(shí)的值之間不同,這就導(dǎo)致寫入或讀出的地址錯(cuò)誤。由于考慮延時(shí)的作用,空/滿標(biāo)志的產(chǎn)生并不一定出現(xiàn)在FIFO真的空/滿時(shí)才出現(xiàn)。可能FIFO還未空/滿時(shí)就出現(xiàn)了空/滿標(biāo)志。這并沒有什么不好,只要保證FIFO不出現(xiàn)overflow or underflow 就OK了。

很多關(guān)于FIFO的文章其實(shí)討論的都是空/滿標(biāo)志的不同算法問題。

在Vijay A. Nebhrajani的《異步FIFO結(jié)構(gòu)》一文中,作者提出了兩個(gè)關(guān)于FIFO空/滿標(biāo)志的算法。

第一個(gè)算法:構(gòu)造一個(gè)指針寬度為N+1,深度為2^N字節(jié)的FIFO(為方便比較,將格雷碼指針轉(zhuǎn)換為二進(jìn)制指針)。當(dāng)指針的二進(jìn)制碼中最高位不一致而其它N位都相等時(shí),F(xiàn)IFO為滿(在Clifford E. Cummings的文章中以格雷碼表示是前兩位均不相同,而后兩位LSB相同為滿,這與換成二進(jìn)制表示的MSB不同其他相同為滿是一樣的)。當(dāng)指針完全相等時(shí),F(xiàn)IFO為空。這也許不容易看出,舉個(gè)例子說明一下:一個(gè)深度為8字節(jié)的FIFO怎樣工作(使用已轉(zhuǎn)換為二進(jìn)制的指針)。FIFO_WIDTH=8,F(xiàn)IFO_DEPTH= 2^N = 8,N = 3,指針寬度為N+1=4。起初rd_ptr_bin和wr_ptr_bin均為“0000”。此時(shí)FIFO中寫入8個(gè)字節(jié)的數(shù)據(jù)。wr_ptr_bin =“1000”,rd_ptr_bin=“0000”。當(dāng)然,這就是滿條件。現(xiàn)在,假設(shè)執(zhí)行了8次的讀操作,使得rd_ptr_bin =“1000”,這就是空條件。另外的8次寫操作將使wr_ptr_bin 等于“0000”,但rd_ptr_bin 仍然等于“1000”,因此FIFO為滿條件。

顯然起始指針無需為“0000”。假設(shè)它為“0100”,并且FIFO為空,那么8個(gè)字節(jié)會(huì)使wr_ptr_bin =“1100”,, rd_ptr_bin 仍然為“0100”。這又說明FIFO為滿。

在Vijay A. Nebhrajani的這篇《異步FIFO結(jié)構(gòu)》文章中說明了怎樣運(yùn)用格雷碼來設(shè)置空滿的條件,但沒有說清為什么深度為8的FIFO其讀寫指針要用3+1位的格雷碼來實(shí)現(xiàn),而3+1位的格雷碼可以表示16位的深度,而真實(shí)的FIFO只有8位,這是怎么回事?而這個(gè)問題在Clifford E. Cummings的文章中得以解釋。三位格雷碼可表示8位的深度,若在加一位最為MSB,則這一位加其他三位組成的格雷碼并不代表新的地址,也就是說格雷碼的0100表示表示7,而1100仍然表示7,只不過格雷碼在經(jīng)過一個(gè)以0位MSB的循環(huán)后進(jìn)入一個(gè)以1為MSB的循環(huán),然后又進(jìn)入一個(gè)以0位MSB的循環(huán),其他的三位碼仍然是格雷碼,但這就帶來一個(gè)問題,在0100的循環(huán)完成后,進(jìn)入1000,他們之間有兩位發(fā)生了變換,而不是1位,所以增加一位MSB的做法使得該碼在兩處:0100~1000,1100~0000有兩位碼元發(fā)生變化,故該碼以不是真正的格雷碼。增加的MSB是為了實(shí)現(xiàn)空滿標(biāo)志的計(jì)算。Vijay A. Nebhrajani的文章用格雷碼轉(zhuǎn)二進(jìn)制,再轉(zhuǎn)格雷碼的情況下提出空滿條件,僅過兩次轉(zhuǎn)換,而Clifford E. Cummings的文章中直接在格雷碼條件下得出空滿條件。其實(shí)二者是一樣的,只是實(shí)現(xiàn)方式不同罷了。

第二種算法:Clifford E. Cummings的文章中提到的STYLE#2。它將FIFO地址分成了4部分,每部分分別用高兩位的MSB 00 、01、 11、 10決定FIFO是否為going full 或going empty (即將滿或空)。如果寫指針的高兩位MSB小于讀指針的高兩位MSB則FIFO為“幾乎滿”,

若寫指針的高兩位MSB大于讀指針的高兩位MSB則FIFO為“幾乎空”。

在Vijay A. Nebhrajani的《異步FIFO結(jié)構(gòu)》第三部分的文章中也提到了一種方法,那就是方向標(biāo)志與門限。設(shè)定了FIFO容量的75%作為上限,設(shè)定FIFO容量的25%為下限。當(dāng)方向標(biāo)志超過門限便輸出滿/空標(biāo)志,這與Clifford E. Cummings的文章中提到的STYLE #2可謂是異曲同工。他們都屬于保守的空滿判斷。其實(shí)這時(shí)輸出空滿標(biāo)志FIFO并不一定真的空/滿。

說到此,我們已經(jīng)清楚地看到,F(xiàn)IFO設(shè)計(jì)最關(guān)鍵的就是產(chǎn)生空/滿標(biāo)志的算法的不同產(chǎn)生了不同的FIFO。但無論是精確的空滿還是保守的空滿都是為了保證FIFO工作的可靠。

本文主要介紹了fifo存儲(chǔ)器芯片型號(hào)有哪些?FIFO存儲(chǔ)器是系統(tǒng)的緩沖環(huán)節(jié),如果沒有FIFO存儲(chǔ)器,整個(gè)系統(tǒng)就不可能正常工作,它主要有幾方面的功能:1)...

fifo先入先出隊(duì)列,這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。即先進(jìn)先出隊(duì)列。在超市購(gòu)物之后會(huì)提著我們滿滿的購(gòu)物車來...

FIFO芯片和單片機(jī)實(shí)現(xiàn)的圖像采集系統(tǒng)

在單片機(jī)應(yīng)用系統(tǒng)中,由于圖像采集速度、程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器的尋址空間的限制,要完整存儲(chǔ)30 fps、640480像素大小的一幅圖像是相當(dāng)困難的。本文運(yùn)...

C語言是一門通用計(jì)算機(jī)編程語言,應(yīng)用廣泛。C語言的設(shè)計(jì)目標(biāo)是提供一種能以簡(jiǎn)易的方式編譯、處理低級(jí)存儲(chǔ)器、產(chǎn)生少量的機(jī)器碼以及不需要任何運(yùn)行環(huán)境支持便能運(yùn)...

FIFO隊(duì)列有兩個(gè)位置指示指針。一個(gè)是寫指針,指向隊(duì)列的第一個(gè)存儲(chǔ)單元。一個(gè)讀指針,指向隊(duì)列的最后一個(gè)存儲(chǔ)單元。當(dāng)有寫命令的時(shí)候,數(shù)據(jù)寫入寫指針指向的存...

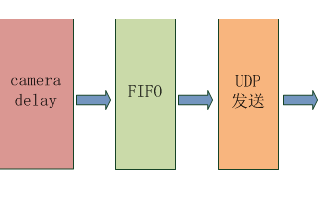

【紫光同創(chuàng)國(guó)產(chǎn)FPGA教程】【第二十七章】千兆以太網(wǎng)視頻傳輸實(shí)驗(yàn)

本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處( http://www. alinx.com ...

異步FIFO設(shè)計(jì)方案詳解 異步FIFO設(shè)計(jì)的難點(diǎn)在哪里

一般而言,處理跨時(shí)鐘域的方法有這么幾種(大家在網(wǎng)上也都能找到資料,這些資料大都來自幾篇經(jīng)典的論文,中文方面的資料大都是翻譯過著理解這幾篇論文而來):少量...

2018-09-10 標(biāo)簽:fifo數(shù)據(jù)通訊 1.3萬 0

fifo存儲(chǔ)器是什么_fifo存儲(chǔ)器有什么特點(diǎn)

FIFO( First In First Out)簡(jiǎn)單說就是指先進(jìn)先出。由于微電子技術(shù)的飛速發(fā)展,新一代FIFO芯片容量越來越大,體積越來越小,價(jià)格越來...

2017-12-06 標(biāo)簽:fifofifo存儲(chǔ)器 1.1萬 0

擁塞管理是指網(wǎng)絡(luò)在發(fā)生擁塞時(shí),如何進(jìn)行管理和控制。FIFO隊(duì)列不對(duì)報(bào)文進(jìn)行分類,按報(bào)文到達(dá)接口的先后順序讓報(bào)文進(jìn)入隊(duì)列,采用盡力而為的轉(zhuǎn)發(fā)模式,PQ隊(duì)列...

2018-02-23 標(biāo)簽:fifo擁塞計(jì)算機(jī)數(shù)據(jù)通信 1.1萬 0

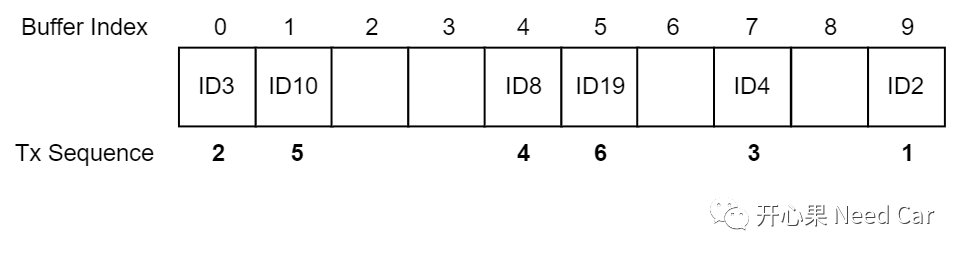

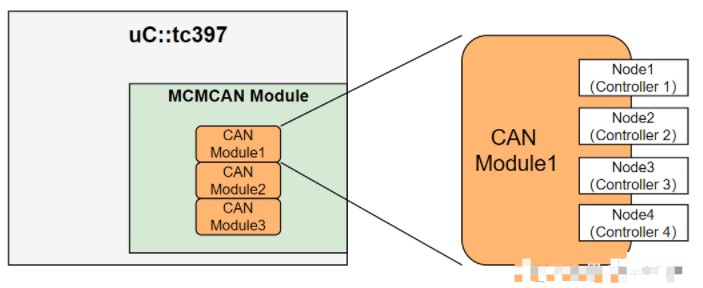

CAN報(bào)文發(fā)送有優(yōu)先級(jí)嗎?

降低同一時(shí)刻,多個(gè)發(fā)送報(bào)文的Burst Send問題。這個(gè)問題屬于QA1的延申。一個(gè)節(jié)點(diǎn),發(fā)送的報(bào)文類型可以有多種(QA1提到)。

224

1

【連載視頻教程(十六)】小梅哥FPGA設(shè)計(jì)思想與驗(yàn)證方法視頻教程之FIFO介紹與時(shí)序驗(yàn)證

標(biāo)簽:fifoFPGA開發(fā)板 32086 224

LT8988無線收發(fā)芯片的數(shù)據(jù)手冊(cè)免費(fèi)下載立即下載

類別:IC中文資料 2019-05-05 標(biāo)簽:發(fā)射機(jī)FIFO無線收發(fā)芯片

First Input First Output的縮寫,先入先出隊(duì)列,這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。是一種...

2021-05-29 標(biāo)簽:單片機(jī)存儲(chǔ)器數(shù)據(jù)傳輸 3.2萬 0

MPU6050移植讀取數(shù)據(jù)時(shí)出現(xiàn)FIFO溢出問題解析

MPU-6000(6050)為全球首例整合性6軸運(yùn)動(dòng)處理組件,相較于多組件方案,免除了組合陀螺儀與加速器時(shí)間軸之差的問題,減少了大量的封裝空間。為什么F...

診斷報(bào)文:一般選擇配置成BASIC CAN類型(結(jié)合FIFO Buffer使用),因?yàn)樵\斷報(bào)文的請(qǐng)求/響應(yīng)不能錯(cuò)序,需按照順序處理,且數(shù)據(jù)不能覆蓋;

First Input First Output的縮寫,先入先出隊(duì)列,這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。在計(jì)算...

2017-12-06 標(biāo)簽:fifoad數(shù)據(jù)采集 1.4萬 0

FPGA編程時(shí)的一些實(shí)際問題闡述及解決方案詳解

問題: 隨著NI的FPGA產(chǎn)品的廣泛使用,很多同事和客戶都碰到了一些FPGA編程時(shí)遇到的問題。由于FPGA不能實(shí)時(shí)調(diào)試,每次修改一點(diǎn)代碼之后都要編譯很長(zhǎng)...

使用硬件FIFO來優(yōu)化串口的數(shù)據(jù)收發(fā)

本文在探討傳統(tǒng)數(shù)據(jù)收發(fā)不足之后,介紹如何使用帶FIFO的串口來減少接收中斷次數(shù),通過一種自定義通訊協(xié)議格式,給出幀打包方法;之后介紹一種特殊的串口數(shù)據(jù)發(fā)...

本文首先對(duì)異步 FIFO 設(shè)計(jì)的重點(diǎn)難點(diǎn)進(jìn)行分析,最后給出詳細(xì)代碼。 一、FIFO簡(jiǎn)單講解 FIFO的本質(zhì)是RAM, 先進(jìn)先出 重要參數(shù):fifo深度(...

2017-11-15 標(biāo)簽:fifo 8878 0

LabVIEW FPGA模塊實(shí)現(xiàn)FIFO深度設(shè)定

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來的數(shù)據(jù)不連續(xù)問題,結(jié)合LabVIEWFPGA的編程特點(diǎn)和DMA FIFO的工作原理...

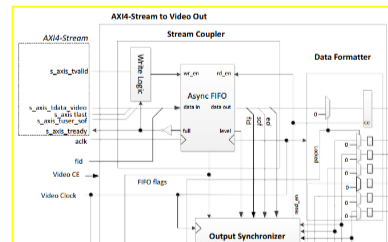

關(guān)于Video out IP和Video Timing Controller IP的介紹

本文對(duì)Video out IP和Video Timing Controller IP進(jìn)行簡(jiǎn)要介紹,為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示...

FIFO是在FPGA設(shè)計(jì)中使用的非常頻繁,也是影響FPGA設(shè)計(jì)代碼穩(wěn)定性以及效率等得關(guān)鍵因素。在數(shù)據(jù)連續(xù)讀取時(shí),為了能不間斷的讀出數(shù)據(jù)而又不導(dǎo)致FIFO...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |